|

|

PDF AD9993 Data sheet ( Hoja de datos )

| Número de pieza | AD9993 | |

| Descripción | Integrated Mixed-Signal Front End | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9993 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Data Sheet

Integrated Mixed-Signal Front End (MxFE)

AD9993

FEATURES

Quad 14-bit 250 MSPS ADC

SFDR = 83 dBc at 87 MHz input

Dual 14-bit 500 MSPS DAC

SFDR = 75 dBc at 20 MHz output

On-chip PLL clock synthesizer

Low power

1536 mW, 1 GHz master clock, on-chip synthesizer

500 MHz double data rate (DDR)

LVDS interfaces for DACs and ADCs

Small 12 mm × 12 mm lead-free BGA package

APPLICATIONS

Point to point microwave backhaul radios

Wireless repeaters

GENERAL DESCRIPTION

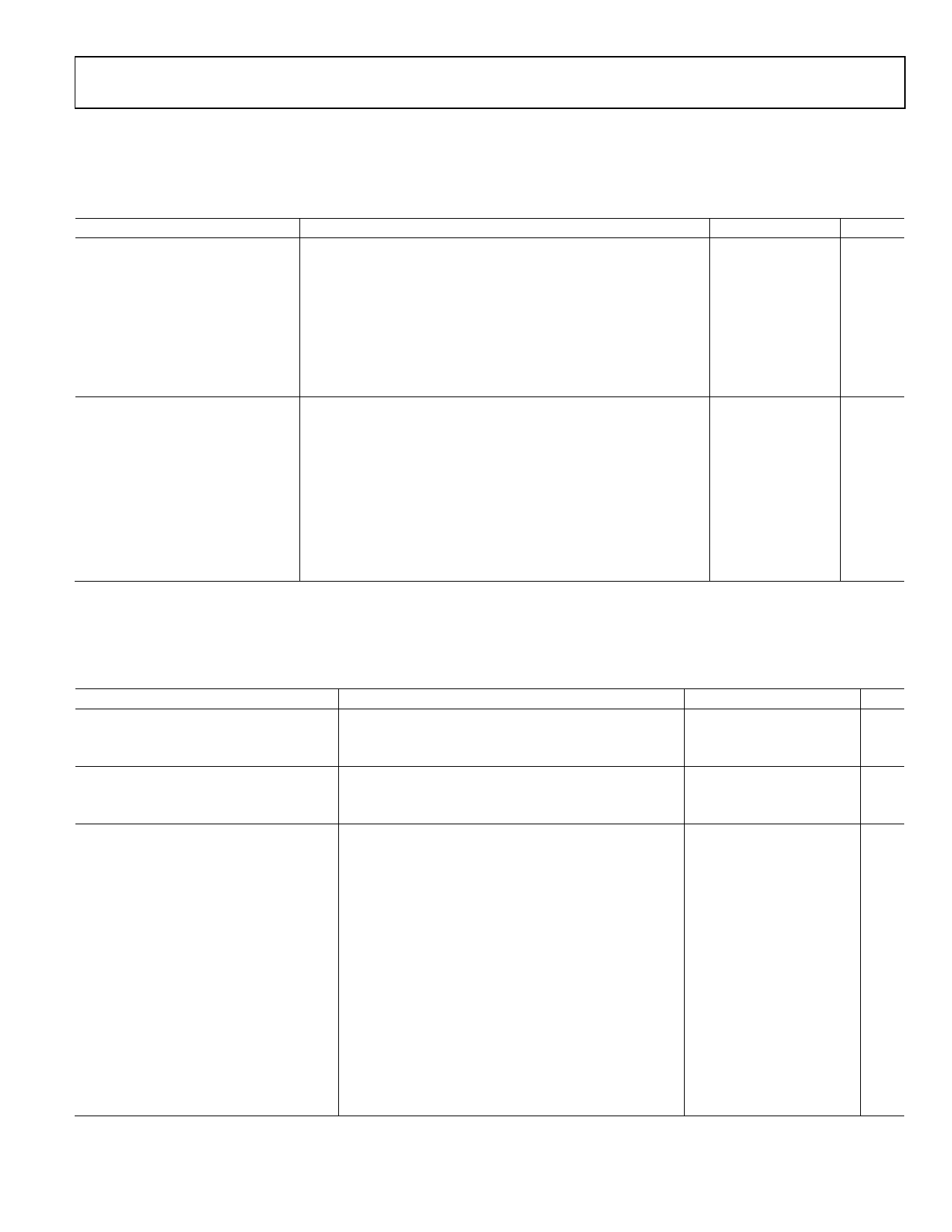

The AD9993 is a mixed-signal front-end (MxFE®) device that

integrates four 14-bit ADCs and two 14-bit DACs. Figure 1

shows the block diagram of the MxFE. The MxFE is

programmable using registers accessed via a serial peripheral

interface (SPI). ADC and DAC datapaths include FIFO buffers

to absorb phase differences between LVDS lane clocks and the

data converter sampling clocks.

The MxFE DACs are part of the Analog Devices, Inc., high

speed CMOS DAC core family. These DACs are designed to be

used in wide bandwidth communication system transmitter

(Tx) signal chains.

The MxFE ADCs are multistage pipelined CMOS ADC cores

designed for use in communications receivers.

FUNCTIONAL BLOCK DIAGRAM

2 14

ADC_A

2 14

ADC_B

14

4

DCO CLOCK

STROBE

LVDS

BUFFER

DOUT3A_x TO DOUT0A_x

DOUT3B_x TO DOUT0B_x

DOUT3C_x TO DOUT0C_x

DOUT3D_x TO DOUT0D_x

DCO_x

STROBE_x

2 14

ADC_C

DIGITAL

–ADC AND DAC

DATAPATHS

14

DIN6A_x TO DIN0A_x

2

ADC_D

14

–CONTROLS

–SPI REGISTERS

LVDS

BUFFER

DIN6B_x TO DIN0B_x

–FIFO BUFFERS

DCI CLOCK

DCI_x

2 14

DAC_A

2 14

DAC_B

4 SPI_SCLK, SPI_CS, SPI_SDI, SPI_SDO

RST

ALERT

PLL

31.25MHz

OR

62.5MHz

DIV

0

1

1GHz

CLOCK GENERATOR

Figure 1.

MxFE

AD9993

Rev. A

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarksandregisteredtrademarksarethepropertyoftheirrespectiveowners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

©2014 Analog Devices, Inc. All rights reserved.

Technical Support

www.analog.com

1 page

Data Sheet

AD9993

AC SPECIFICATIONS

TMIN to TMAX, AVDD33 = 3.3 V, DVDD = AVDD = 1.8 V, DAC sampling rate = 500 MSPS and ADC sampling rate = 250 MSPS, unless

otherwise specified.

Table 2.

Parameter

DAC OUTPUT

Spurious-Free Dynamic Range

(SFDR)

Two Tone Intermodulation

Distortion (IMD3)

Noise Spectral Density (NSD),

Single Tone

256-QAM Adjacent Channel

Power (ACP)

ADC INPUT

Signal to Noise Ratio (SNR)

fIN = 87 MHz

Spurious-Free Dynamic Range

(SFDR)

fIN = 10 MHz

fIN = 87 MHz

Two-Tone IMD3

Full Power Bandwidth

Test Conditions/Comments

fOUT = 20 MHz

fOUT = 80 MHz

fOUT = 80 MHz

fCENTER = 50 MHz, single carrier, 3.375 MHz offset frequency

Min Typ Max Unit

75

65

−160

76

dBc

dBc

dBm/Hz

dBc

Measured with −1.0 dBFS sine wave input

Measured with −1.0 dBFS sine wave input

fIN1 = 89 MHz, fIN2 = 92 MHz, AIN = −12 dBFS

Bandwidth of operation in which proper ADC performance can be

achieved

70

86

83

90

1000

dBc

dBc

dBc

dBc

MHz

DIGITAL SPECIFICATIONS

TMIN to TMAX, AVDD33 = 3.3 V, DVDD = AVDD = 1.8 V, unless otherwise noted.

Table 3.

Parameter

CMOS INPUT LOGIC LEVEL

Input VIN Logic High

Input VIN Logic Low

CMOS OUTPUT LOGIC LEVEL

Output VOUT Logic High

Output VOUT Logic Low

ADC AND DAC LVDS DATA INTERFACES

ADC LVDS Transmitter Outputs

DCO_P/DCO_N to Data Skew (tSKEW)

Output Voltage High, VOH, Single

Ended

Output Voltage Low, VOL, Single

Ended

Output Differential Voltage

Output Offset Voltage

DAC LVDS Receiver Inputs

Input Voltage Range, Single Ended

Input Differential Threshold

Input Differential Hysteresis

Receiver Differential Input

Impedance

Test Conditions/Comments

Data to DDR DCO_P/DCO_N transition delay

Applies to output voltage, positive and negative, VOUTP

and VOUTN

Applies to VOUTP and VOUTN

Specifications apply to DAC data inputs and DCI_P/DCI_N

Applies to input voltage, positive and negative, VINP and

VINN

Min Typ

1.8

0.0

1.2

350

1375

1025

200

1200

825

−100

25

85

Max Unit

V

V

V

0.8 V

ps

mV

mV

mV

mV

1575 mV

+100 mV

mV

115 Ω

Rev. A | Page 5 of 56

5 Page

Data Sheet

AD9993

TYPICAL PERFORMANCE CHARACTERISTICS

RECEIVER ADC PERFORMANCE

fADC = 250 MHz, unless otherwise specified.

0

–15

–30

–45

–60

–75

–90

–105

–120

–135

3

6

2

5

4

15 30 45 60 75 90 105

FREQUENCY (MHz)

Figure 3. Single Tone FFT, fIN = 87 MHz

120

120

100

80

60

40

20 SNR (dBc)

SNR (dBFS)

SFDR (dBc)

SFDR (dBFS)

0

–90 –80 –70 –60 –50 –40 –30 –20 –10 0

INPUT AMPLITUDE (dBFS)

Figure 4. Single Tone SNR and SFDR vs. Input Amplitude (AIN), fIN = 87 MHz

0

SFDR (dBc)

SFDR (dBFS)

–20

–40

–60

–80

–100

–120

–90 –80 –70 –60 –50 –40 –30 –20 –10

INPUT AMPLITUDE (dBFS)

Figure 5. Two Tone SFDR vs. Input Amplitude (AIN), fIN1 = 89.12 MHz,

fIN2 = 92.12 MHz

IMD3 (dBc)

–20 IMD3 (dBFS)

–40

–60

–80

–100

–120

–90 –80 –70 –60 –50 –40 –30 –20 –10

INPUT AMPLITUDE (dBFS)

Figure 6. Two Tone IMD3 vs. Input Amplitude (AIN), fIN1 = 89.12 MHz, fIN2 =

92.12 MHz

95

90

85

80

75

70

65

20 40 60 80 100 120

fIN (MHz)

Figure 7. Single Tone SNR vs. Input Frequency (fIN)

95

90

85

80

75

70

65

20 40 60 80 100 120

fIN (MHz)

Figure 8. Single Tone SNR vs. Input Frequency (fIN)

Rev. A | Page 11 of 56

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet AD9993.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9990 | 14-Bit CCD Signal Processor and Precision Timing Core | Analog Devices |

| AD9991 | 10-Bit CCD Signal Processor | Analog Devices |

| AD9992 | 12-Bit CCD Signal Processor | Analog Devices |

| AD9993 | Integrated Mixed-Signal Front End | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |