|

|

PDF NT5DS16M16ES Data sheet ( Hoja de datos )

| Número de pieza | NT5DS16M16ES | |

| Descripción | Commercial and Industrial Consumer DDR 256Mb SDRAM | |

| Fabricantes | Nanya | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NT5DS16M16ES (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DDR 256Mb SDRAM

Confidential

NT5DS32M8ES / NT5DS16M16ES

Nanya Technology Corp.

NT5DS32M8ES / NT5DS16M16ES

Commercial and Industrial Consumer DDR 256Mb SDRAM

Features

JEDEC DDR Compliant

- Differential clock inputs (CK and )

- DLL aligns DQ and DQS transition with CK transitions

- 2n Prefetch Architecture

- DQS is edge-aligned with data for reads and

center-aligned with data for WRITEs

- DQ and DM referenced to both edges of DQS

- tRAS lockout (tRAP = tRCD)

Signal Integrity

- Configurable DS for system compatibility

Data Integrity

- Auto Refresh Mode

- Self Refresh Mode

Power Saving Mode

- Power Down Mode

Interface and Power Supply

- SSTL_2 compatible (All inputs)

- SSTL_2, Class II compatible (All outputs)

- VDD/VDDQ=2.5V±0.2V (DDR-333)

- VDD/VDDQ=2.6V±0.1V (DDR-400)

Speed Grade (CL-TRCD-TRP) 1,2

- 400 Mbps / 3-3-3

Options

Temperature Range (TA)

- Commercial Grade = 0℃~70℃

- Industrial Grade = -40℃~85℃

CAS Latency (2.5, 3, 4)

Burst Length (2, 4, 8)

Programmable Functions

Burst Type (Sequential, Interleaved)

Driver Strength (Normal, Weak)

Packages / Density Information

Lead-free RoHS compliance and Halogen-free

256Mb

(Org. / Package)

Length x Width5

(mm)

Pin pitch

(mm)

32M x 8

66 pin

TSOPII

16M x 16

22.22 x 10.16

0.65

Density and Addressing

Item

Organization

Number of banks

Bank Address

Auto precharge

tRFC(ns) 3

tREFI (µs) 4

Row Address

Column Address

256Mb

32M x 8

4

BA0,BA1

A10/AP

72

7.8

A0-A12

A0-A9

16M x 16

4

BA0,BA1

A10/AP

72

7.8

A0-A12

A0-A8

Notes:

1. The timing specification of high speed bin is backward compatible with low speed bin.

2. The functionality described in, and the timing specifications included in this data sheet are for the DLL Enabled mode of operation.

3. Violating tRFC specification will induce malfunction.

4. tREFI values for all bank refresh is within temperature specification.

5. It excludes the pin.

Version 1.2

11/2013

1 Nanya Technology Corporation ©

NTC has the rights to change any specifications or product without notification.

All Rights Reserved

1 page

DDR 256Mb SDRAM

NT5DS32M8ES / NT5DS16M16ES

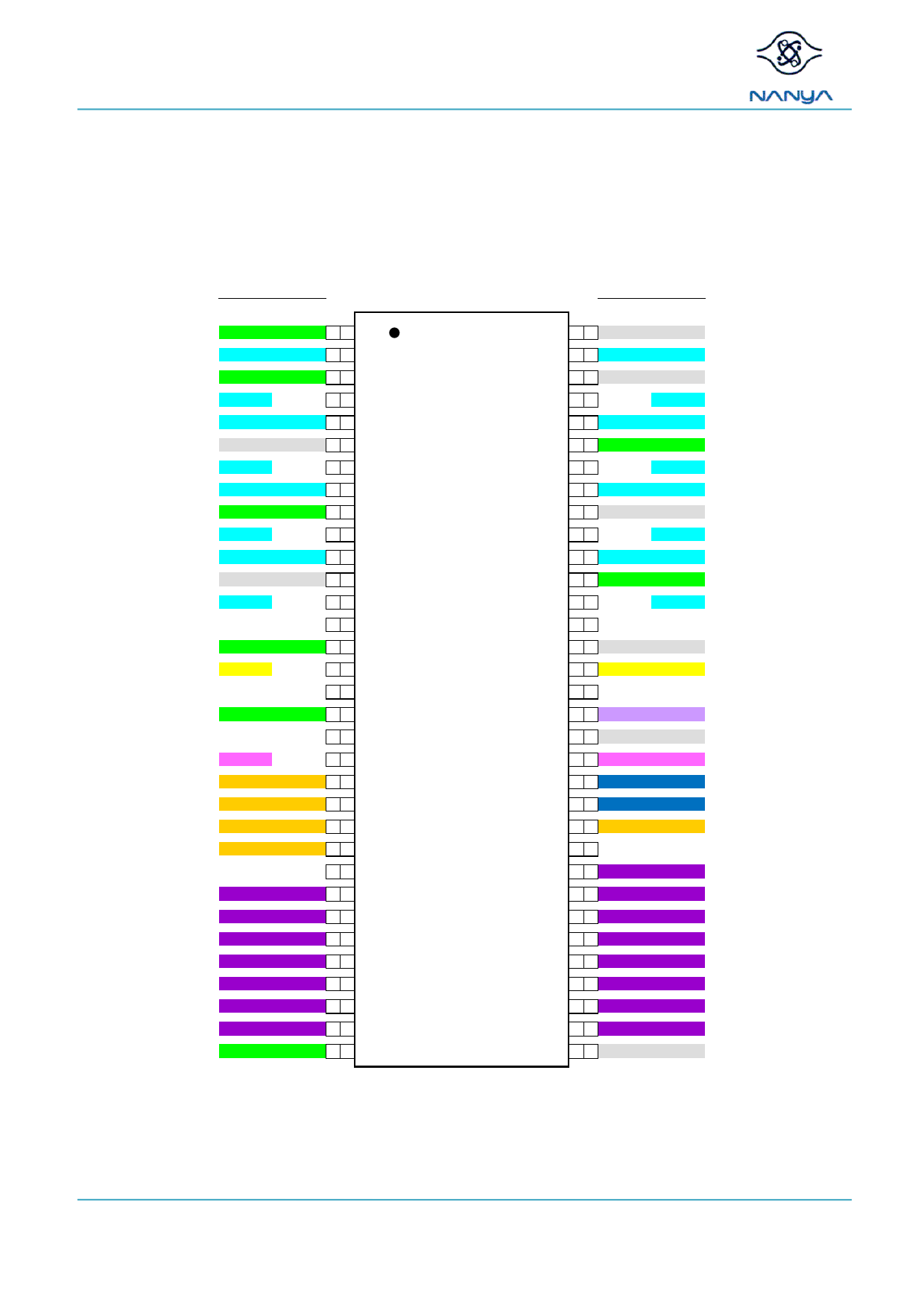

Pin Configuration (X8 / X16)

< TOP View>

See the balls through the package

X16 X8

X8 X16

VDD VDD

1

66 VSS VSS

DQ0 DQ0

2

65 DQ7 DQ15

VDDQ VDDQ

3

64 VSSQ VSSQ

DQ1 NC

4

63 NC DQ14

DQ2 DQ1

5

62 DQ6 DQ13

VSSQ VSSQ

6

61 VDDQ VDDQ

DQ3 NC

7

60 NC DQ12

DQ4 DQ2

8

59 DQ5 DQ11

VDDQ VDDQ

9

58 VSSQ VSSQ

DQ5 NC

10

57 NC DQ10

DQ6 DQ3

11

56 DQ4 DQ9

VSSQ VSSQ

12

55 VDDQ VDDQ

DQ7 NC

13

54 NC DQ8

NC NC

14 TOP VIEW 53

NC NC

VDDQ VDDQ

15

52 VSSQ VSSQ

LDQS NC

16

51 DQS UDQS

NC NC

17

50 NC NC

VDD VDD

18

49 VREF VREF

NC NC

19

48 VSS VSS

LDM

WE

NC

WE

20

21

47 DM UDM

46

AS

RAS

S

AS

RAS

S

22

23

24

45 CK CK

44 CKE CKE

43 NC NC

NC NC

25

42 A12 A12

BA0 BA0

26

41 A11 A11

BA1 BA1

27

40 A9 A9

A10/AP A10/AP

28

39 A8 A8

A0 A0

29

38 A7 A7

A1 A1

30

37 A6 A6

A2 A2

31

36 A5 A5

A3 A3

32

35 A4 A4

VDD VDD

33

34 VSS VSS

Version 1.2

11/2013

5 Nanya Technology Corporation ©

All Rights Reserved

5 Page

DDR 256Mb SDRAM

NT5DS32M8ES / NT5DS16M16ES

Functional Descriptions

The 256Mb DDR SDRAM is a high-speed CMOS, dynamic random-access memory containing 268,435,456 bits. It is

internally configured as a quad-bank DRAM.

It uses a double-data-rate architecture to achieve high-speed operation. The double-data-rate architecture is essentially a

2n prefetch architecture, with an interface designed to transfer two data words per clock cycle at the I/O pins. A single

read or write access consists of a single 2n-bit wide, one clock cycle data transfer at the internal DRAM core and two

corresponding n-bit wide, one-half clock cycle data transfers at the I/O pins.

Read and write accesses to the DDR SDRAM are burst oriented; accesses start at a selected location and continue for a

programmed number of locations in a programmed sequence. Accesses begin with the registration of an Active command,

which is then followed by a Read or Write command. The address bits registered coincident with the Active command are

used to select the bank and row to be accessed (BA0, BA1 select the bank; A0-A12 select the row). The address bits

registered coincident with the Read or Write command are used to select the starting column location for the burst access.

Prior to normal operation, the DDR SDRAM must be initialized. The following sections provide detailed information

covering device initialization, register definition, command descriptions and device operation.

Initialization

Only one of the following two conditions must be met.

• No power sequencing is specified during power up or power down given the following criteria:

VDD and VDDQ are driven from a single power converter output, and

VTT is limited to 1.35V, and

VREF tracks VDDQ /2

OR

• The following relationships must be followed:

VDDQ is driven after or with VDD such that VDDQ < VDD + 0.3V

VTT is driven after or with VDDQ such that VTT < VDDQ + 0.3V

VREF is driven after or with VDDQ such that VREF < VDDQ + 0.3V

The DQ and DQS outputs are in the High-Z state, where they remain until driven in normal operation (by a read access).

After all power supply and reference voltages are stable, and the clock is stable, the DDR SDRAM requires a 200s delay

prior to applying an executable command.

Once the 200s delay has been satisfied, a Deselect or NOP command should be applied, and CKE must be brought

HIGH. Following the NOP command, a Precharge ALL command must be applied. Next a Mode Register Set command

must be issued for the Extended Mode Register, to enable the DLL, and then a Mode Register Set command must be

issued for the Mode Register, to reset the DLL, and to program the operating parameters. 200 clock cycles are required

between the DLL reset and any read command. A Precharge ALL command should be applied, placing the device in the

“all banks idle” state

Version 1.2

11/2013

11 Nanya Technology Corporation ©

All Rights Reserved

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet NT5DS16M16ES.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NT5DS16M16ES | Commercial and Industrial Consumer DDR 256Mb SDRAM | Nanya |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |