|

|

PDF PE99153DIE Data sheet ( Hoja de datos )

| Número de pieza | PE99153DIE | |

| Descripción | Hi-Rel 6A DC-DC Converter | |

| Fabricantes | Peregrine Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PE99153DIE (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

Product Description

The PE99153 DIE is a radiation tolerant point-of-load

buck regulator delivering high efficiency at VIN = 5V and

output currents up to 6A continuous. This single-chip

solution is perfect for Hi-Rel applications and delivers

peak efficiency exceeding 93%. A minimal external

component count and high switching frequency enables

>10 W/in2 standard PCB designs while high efficiency

minimizes thermal concerns. All power switching devices

are integrated on-chip.

Fabricated in Peregrine’s patented UltraCMOS®

technology, the PE99153 offers excellent power

efficiency and intrinsic radiation tolerance.

Table 1. Radiation Performance

TID 100 kRad(Si)

SEL > 90 MeV•cm2/mg

SEB

> 90 MeV•cm2/mg

SET

> 90 MeV•cm2/mg

SEFI

> 90 MeV•cm2/mg

SEGR

> 90 MeV•cm2/mg

SEL, SEB, SEGR, SEU, SEFI: None observed, Au/60 degrees

SET: No events exceeding 30 mV transient observed @ Au,

LET=90, 60 degrees and normal incidence

Figure 1. Typical Application Diagram

Product Specification

PE99153 DIE

Hi-Rel 6A DC-DC Converter

Radiation Tolerant UltraCMOS®

Monolithic Point-of-Load Synchronous

Buck Regulator with Integrated Switches

Features

• Up to 6A continuous

• Output voltage range from 1.0–3.6V by

external select resistors

• Input voltage range 4.6–6.0V

• Current mode control, pulse-by-pulse

current limit, current sharing enabled

and (N+K) redundancy compatible

shutdown mode

• SYNC function, 100 kHz–5 MHz lock

range with selectable 500 kHz / 1 MHz

free running frequency

• Shutdown pin, Power Good output

pin for supply sequencing

• Better than 1% typical initial accuracy

(25°C)

• Control inputs compatible with TTL,

LVTTL, LVCMOS (2.5V and 3.3V)

and 5V CMOS

Document No. DOC-50371-6 │ www.e2v-us.com

©2012–2015 Peregrine Semiconductor Corp. All rights reserved.

Page 1 of 15

1 page

PE99153 DIE

Product Specification

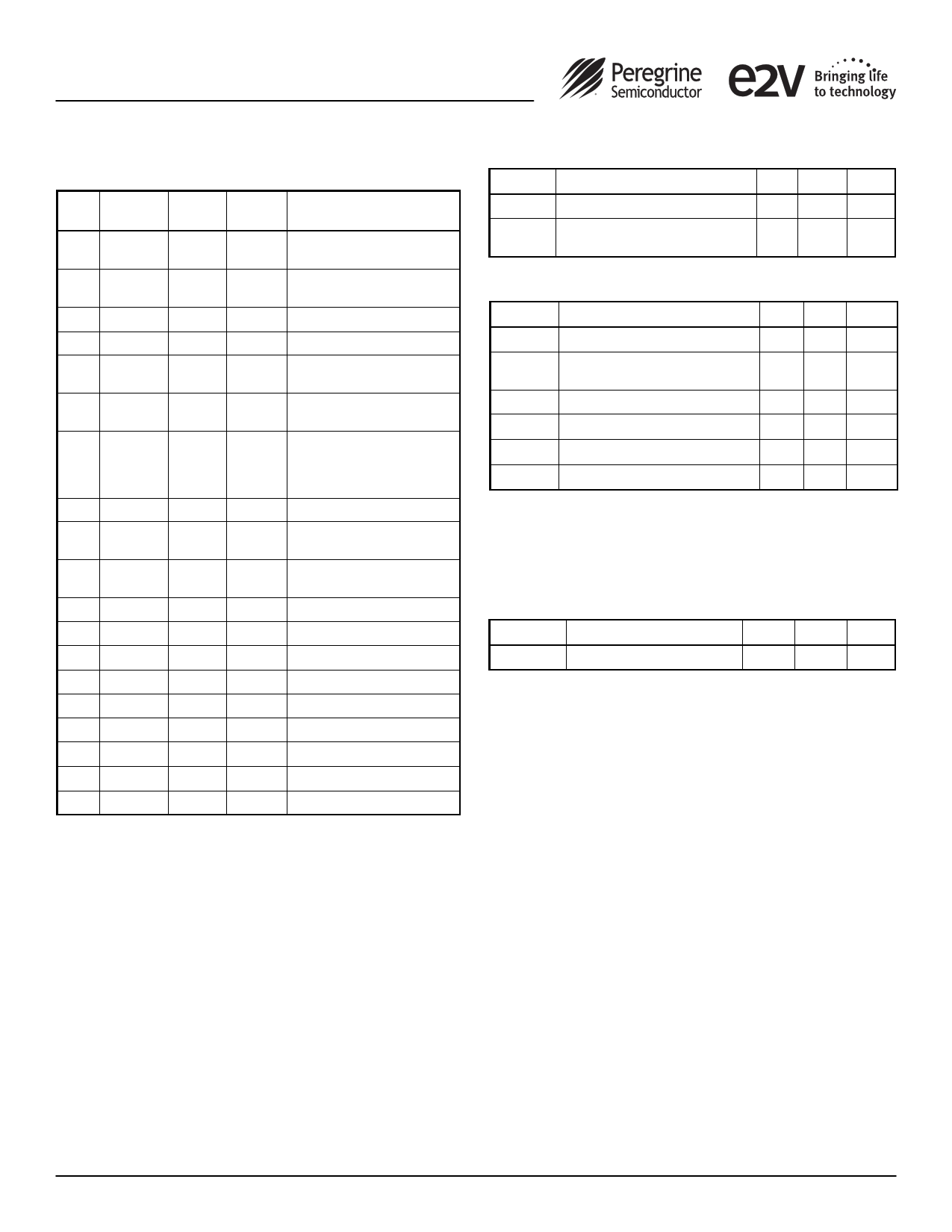

Table 3. Pin Coordinates and Descriptions

(continued)

Pin

No.

Pin Name

X

Y

Description

25

TCSEL0 –2343.9

148.5

Bandgap Reference Voltage

Fine Adjust (0)

26

TCSEL1 –2343.9

297.2

Bandgap Reference Voltage

Fine Adjust (0)

27 GND –2343.9 500 Ground

28 CCSEL –2343.9 696.1 Course trim code

29

EAINM

–2343.9

869.7

Error Amplifier (–) Input,

Loop to VREF

30

EAINP

–2343.9

1068.3

Error Amplifier (+) Input,

Load Feedback

1.000V Reference output,

31

VREF

–2343.9

1266.9

Loop to AAINP. Additional

Low Pass Filtering May be

Necessary

32 AGND –2142.8 1283.2 Bandgap ground

33

SScap

–1944.2

1283.2

Resistor to Set Reference

Current

34

SYNC

–1745.6

1283.2

Loop-Through Complement

Output

35

SDb

–1547 1283.2 Shutdown (L)/enable input

36 TEST –1348.4 1283.2 Ground

37 GND –2343.9 1437.25 Ground

38 VIN –397.5 1000 Input Power Supply

39 VIN 1102.5 1000 Input Power Supply

40 VIN 102.5 0 Input Power Supply

41 VIN 1602.5 0 Input Power Supply

42 VIN –397.5 –1000 Input Power Supply

43 VIN 1102.5 –1000 Input Power Supply

Table 4. Operating Ranges

Symbol

Parameter/Condition

VIN Power supply voltage

TA

Operating temperature range

(case)

Min Max

4.6 6.0

Unit

V

–55 +125 oC

Table 5. Absolute Maximum Ratings

Symbol

Parameter/Condition

Min Max Unit

VIN Power supply voltage

–0.5 6.5

V

TJ

Operating temperature range

(junction)

–55 +145 oC

TST Storage temperature range (case) –65 +150 oC

II DC into any signal input

–10 10 mA

IO DC into any signal output

–50 50 mA

IP DC into any single power pin

–2 2

A

Exceeding absolute maximum ratings may cause

permanent damage. Operation between maximum

operating ranges and absolute maximum operating

ranges for extended periods may reduce reliability.

Table 6. Electrostatic Discharge (ESD) Ratings

Model

Parameter/Condition

Min Max Unit

HBM* VESD All pins

1000

V

Note: * Human Body Model ESD Voltage (HBM, MIL_STD 883 Method 3015.7).

Electrostatic Discharge (ESD) Precautions

When handling this UltraCMOS device, observe the

same precautions that you would use with other

ESD-sensitive devices. Although this device

contains circuitry to protect it from damage due to

ESD, precautions should be taken to avoid

exceeding the specified rating.

Latch-Up Immunity

Unlike conventional CMOS devices, UltraCMOS

devices are immune to latch-up.

ELDRS

The UltraCMOS process does not exhibit enhanced

low-dose-rate sensitivity (ELDRS) since bipolar

minority carrier elements are not used.

Document No. DOC-50371-6 │ www.e2v-us.com

©2012–2015 Peregrine Semiconductor Corp. All rights reserved.

Page 5 of 15

5 Page

PE99153 DIE

Product Specification

The DC resistance of the Inductor will primarily impact

efficiency. For optimal efficiency, the inductor DC

resistance should be selected to be on the order of

magnitude of the RON of the high side switch and low side

switch. Calculation of the efficiency impact will be

discussed in the efficiency section of the Design Guide. A

smaller DC resistance will improve efficiency but will likely

impact PCB area, a subject not addressed in this Design

Guide.

Output Capacitor Selection

The output Capacitor works in tandem with the output

Inductor to filter the Inductor ripple current and to source

and sink current to meet the load demand during a load

step. The output Capacitor is implemented as a network of

parallel capacitors covering low, mid, and high frequency

operation. The capacitor Equivalent Series Resistance

(ESR) and Equivalent Series Inductance (ESL) have a

direct impact on the output voltage ripple, output voltage

droop under transient loading, and loop stability. Ceramic

X7R dielectric capacitors are recommended for their

thermal and electrical properties, along with their size and

cost.

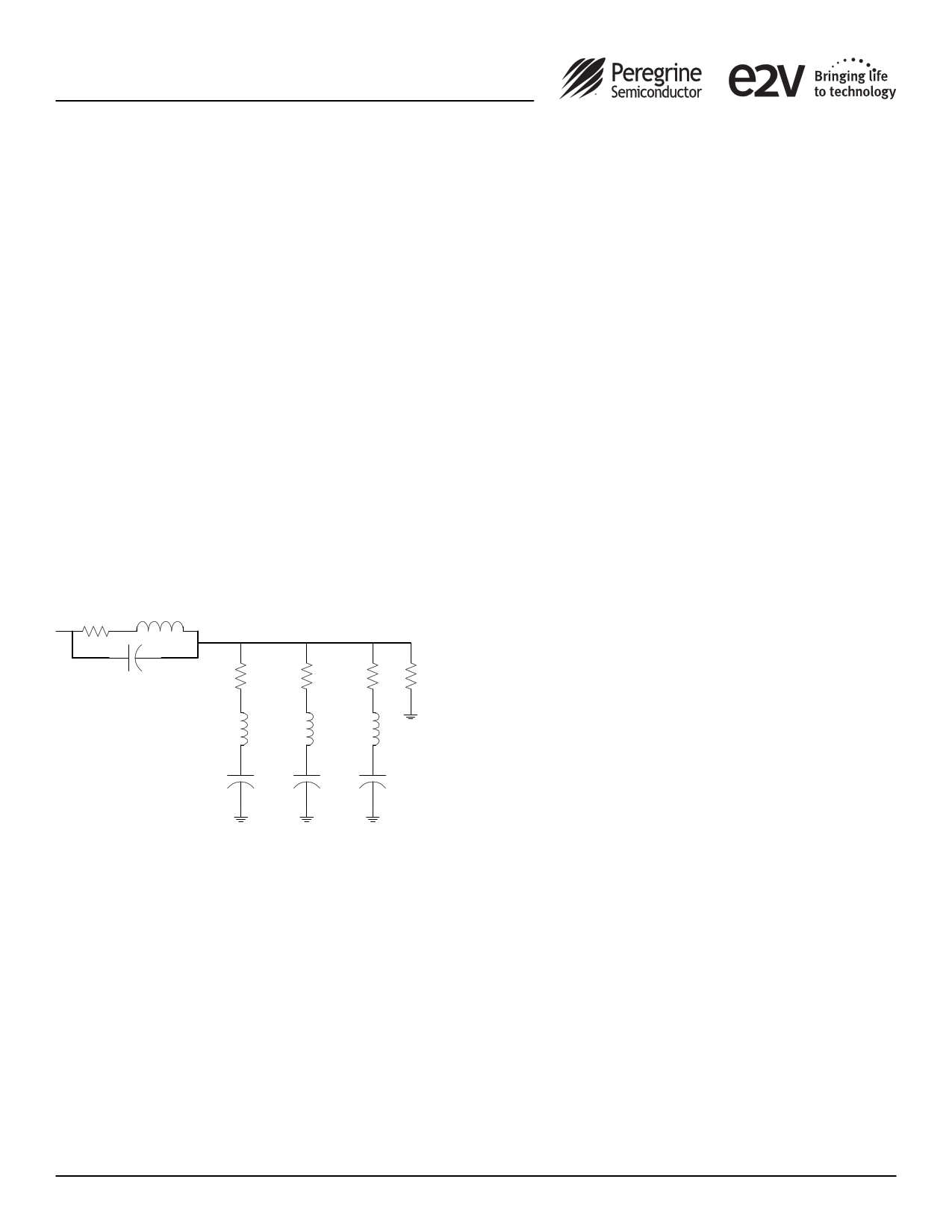

Figure 7. Output Capacitor Selection

DCR Inductor

Vout

SRF Cap

ESR 1

ESR 2

ESR 3

Load

ESL 1

ESL 2

ESL 3

Cout 1

Low Freq

Cout 2

Mid Freq

Cout 3

High Freq

The output voltage droop should be empirically determined

to satisfy the application load step response requirements.

During a transient step in the load current, the output

voltage will initially experience an IR drop of ∆ILOAD × ESR.

If the output capacitor bank is too large, the IR drop is

minimized but the VOUT recovery time is longer. If the

output capacitor bank is too small, the IR drop is increased

but the VOUT recovery time is shorter.

The output voltage ripple should be chosen to meet the

application requirements and tradeoff with the physical

size of the capacitor bank. The output voltage ripple

waveform can be estimated by taking the inverse Fourier

transform of the product of the Fourier transform of the

input signal and the frequency domain transfer function of

the network in Figure 7. (The input to the transfer function

can be approximated as an ideal square wave with period

of FSW, amplitude of VIN and a duty ratio of VOUT / VIN.)

If a SPICE simulation tool is available, the above

estimation can be done by placing the above mentioned

square wave at the input of the filter network and solving

for the output waveform.

Additionally, the total output capacitance and load

resistance set the dominant pole of the voltage mode

control loop. Voltage mode loop stability is described in the

"Voltage Control Loop Compensation Network Design"

section.

In addition to playing a role in stability and output voltage

ripple, the output capacitor bank must be able to absorb

the inductor ripple current. The inductor peak-to-peak

ripple current, calculated as ∆IL in the inductor selection

section, will be absorbed by the capacitor bank. Note that

the RMS current through the output cap can be calculated

as ∆IL/√3 since inductor ripple current waveform is

triangular. The frequency range of capacitors absorbing

the ripple current must be rated to handle this ripple

current.

The PE99153 reference design features three output

capacitors (Cout1, Cout2, and Cout3) that have been chosen

to blend total capacitance, ESR, and ESL to meet the ripple,

droop, and stability requirements over frequency.

Input Capacitor Selection

The input capacitor network sources the trapezoidal

current wave through the source terminal of the high side

switch. Therefore, the RMS current handling and maximum

voltage rating are the main considerations in selecting the

input capacitors.

Neglecting the small (as compared with the load) Inductor

ripple current and assuming that the input capacitor

sources all of the ripple current, the RMS current through

the input capacitor can be calculated as

IRMS–CIN = ILOAD (max) × √ [D × (1–D)]

In addition to sourcing the trapezoidal current wave

through the high side switch, the input bypass capacitors

absorb the high frequency components of the switching

power supply preventing conducted EMI from reaching the

up stream supply. As such, the input bypass capacitor SRF

should be on the order of 10x higher than the switching

frequency of the buck regulator. Additional high frequency

capacitors may be added to further attenuate the high

frequency conducted EMI.

Like the output capacitors, Ceramic X7R dielectric

capacitors are recommended with the added benefit that

the X7R capacitors have very low DC voltage de-rating.

Document No. DOC-50371-6 │ www.e2v-us.com

©2012–2015 Peregrine Semiconductor Corp. All rights reserved.

Page 11 of 15

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet PE99153DIE.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PE99153DIE | Hi-Rel 6A DC-DC Converter | Peregrine Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |