|

|

PDF AT49F040A Data sheet ( Hoja de datos )

| Número de pieza | AT49F040A | |

| Descripción | 5-volt only in-system reprogrammable Flash memory | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT49F040A (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

Features

• Single-voltage Operation

– 5V Read

– 5V Reprogramming

• Fast Read Access Time – 55 ns

• Internal Program Control and Timer

• Sector Architecture

– One 16K Bytes Boot Block with Programming Lockout

– Two 8K Bytes Parameter Blocks

– Eight Main Memory Blocks (One 32K Bytes, Seven 64K Bytes)

• Fast Erase Cycle Time – 6 Seconds

• Byte-by-Byte Programming – 20 µs/Byte Typical

• Hardware Data Protection

• DATA Polling for End of Program Detection

• Low Power Dissipation

– 20 mA Active Current

– 70 µA CMOS Standby Current

• Typical 10,000 Write Cycles

• Green (Pb/Halide-free) Packaging Option

4-megabit

(512K x 8)

5-volt Only

Flash Memory

AT49F040A

1. Description

The AT49F040A is a 5-volt only in-system reprogrammable Flash memory. Its

4 megabits of memory is organized as 524,288 words by 8 bits. Manufactured with

Atmel’s advanced nonvolatile CMOS technology, the device offers access times to

55 ns with power dissipation of just 110 mW over the commercial temperature range.

When the device is deselected, the CMOS standby current is less than 70 µA. To

allow for simple in-system reprogrammability, the AT49F040A does not require high

input voltages for programming. Five-volt-only commands determine the read and

programming operation of the device. Reading data out of the device is similar to

reading from an EPROM; it has standard CE, OE, and WE inputs to avoid bus conten-

tion. Reprogramming the AT49F040A is performed by erasing a block of data and

then programming on a byte-by-byte basis. The byte programming time is a fast 20

µs. The end of a program cycle can be optionally detected by the DATA polling fea-

ture. Once the end of a byte program cycle has been detected, a new access for a

read or program can begin. The typical number of program and erase cycles is in

excess of 10,000 cycles.

The device is erased by executing the erase command sequence; the device inter-

nally controls the erase operations. There are two 8K byte parameter block sections,

eight main memory blocks, and one boot block.

The device has the capability to protect the data in the boot block; this feature is

enabled by a command sequence. The 16K-byte boot block section includes a repro-

gramming lock out feature to provide data integrity. The boot sector is designed to

contain user secure code, and when the feature is enabled, the boot sector is perma-

nently protected from being reprogrammed.

3359C–FLASH–3/05

1 page

AT49F040A

6. Boot Block Programming Lockout

The device has one designated block that has a programming lockout feature. This feature pre-

vents programming of data in the designated block once the feature has been enabled. The size

of the block is 16K bytes. This block, referred to as the boot block, can contain secure code that

is used to bring up the system. Enabling the lockout feature will allow the boot code to stay in the

device while data in the rest of the device is updated. This feature does not have to be activated;

the boot block’s usage as a write protected region is optional to the user. The address range of

the boot block is 00000 to 03FFF.

Once the feature is enabled, the data in the boot block can no longer be erased or programmed.

Data in the main memory block can still be changed through the regular programming method.

To activate the lockout feature, a series of six program commands to specific addresses with

specific data must be performed. Please refer to the “Command Definition Table” on page 6.

6.0.1

Boot Block Lockout Detection

A software method is available to determine if programming of the boot block section is locked

out. When the device is in the software product identification mode (see Software Product Iden-

tification Entry and Exit sections) a read from address location 00002H will show if programming

the boot block is locked out. If the data on I/O0 is low, the boot block can be programmed; if the

data on I/O0 is high, the program lockout feature has been activated and the block cannot be

programmed. The software product identification exit code should be used to return to standard

operation.

6.1 Product Identification

The product identification mode identifies the device and manufacturer as Atmel. It may be

accessed by hardware or software operation. The hardware operation mode can be used by an

external programmer to identify the correct programming algorithm for the Atmel product.

For details, see “Operating Modes” on page 7 (for hardware operation) or Software Product

Identification. The manufacturer and device code is the same for both modes.

6.2 DATA Polling

The AT49F040A features DATA polling to indicate the end of a program cycle. During a program

cycle an attempted read of the last byte loaded will result in the complement of the loaded data

on I/O7. Once the program cycle has been completed, true data is valid on all outputs and the

next cycle may begin. DATA polling may begin at any time during the program cycle.

6.3 Toggle Bit

In addition to DATA polling the AT49F040A provides another method for determining the end of a

program or erase cycle. During a program or erase operation, successive attempts to read data

from the device will result in I/O6 toggling between one and zero. Once the program cycle has

completed, I/O6 will stop toggling and valid data will be read. Examining the toggle bit may begin

at any time during a program cycle.

6.4 Hardware Data Protection

Hardware features protect against inadvertent programs to the AT49F040A in the following

ways: (a) VCC sense: if VCC is below 3.8V (typical), the program function is inhibited. (b) Program

inhibit: holding any one of OE low, CE high or WE high inhibits program cycles. (c) Noise filter:

pulses of less than 15 ns (typical) on the WE or CE inputs will not initiate a program cycle.

3359C–FLASH–3/05

5

5 Page

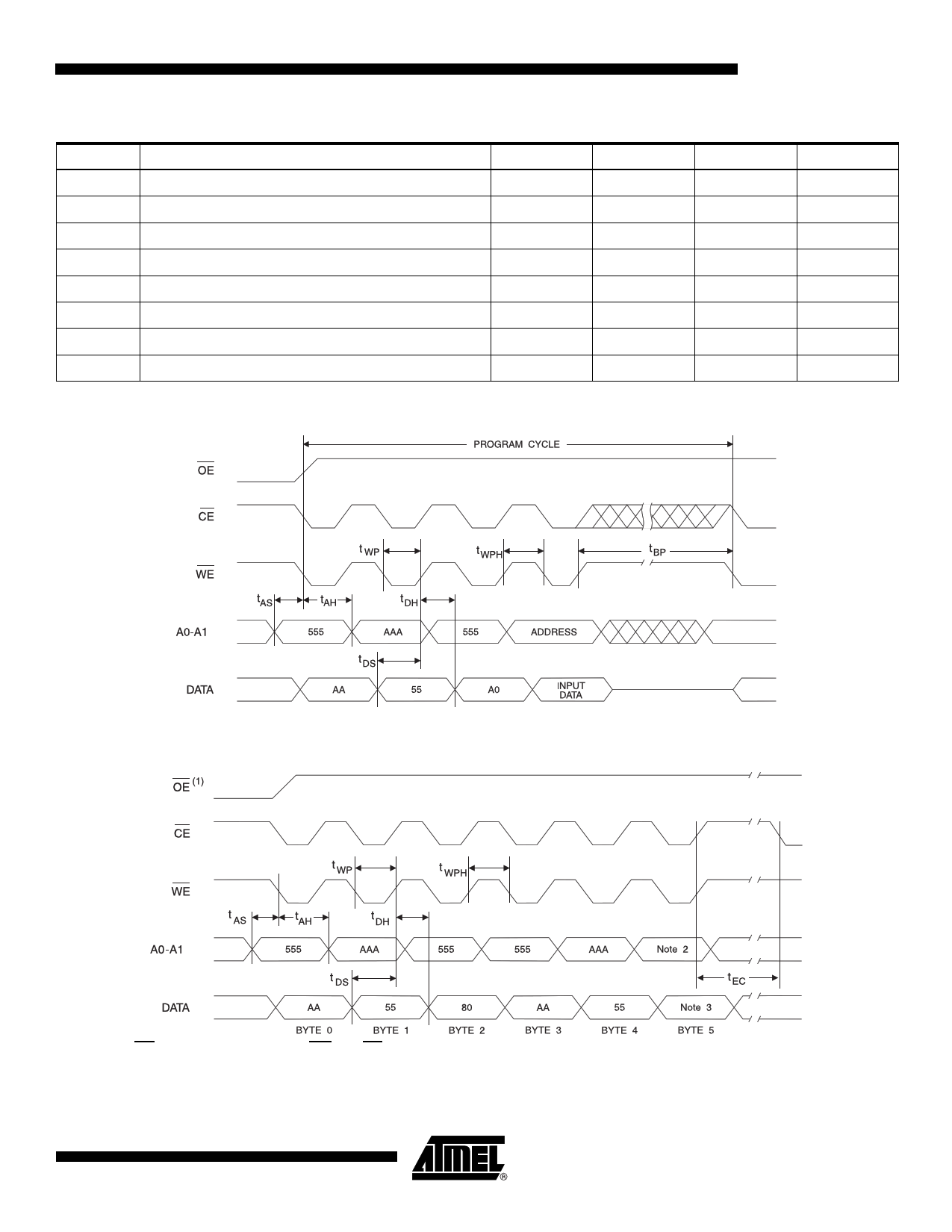

19. Program Cycle Characteristics

Symbol

tBP

tAS

tAH

tDS

tDH

tWP

tWPH

tEC

Parameter

Byte Programming Time

Address Set-up Time

Address Hold Time

Data Set-up Time

Data Hold Time

Write Pulse Width

Write Pulse Width High

Chip Erase Cycle Time

20. Program Cycle Waveforms

AT49F040A

Min Typ Max Units

20 40 µs

0 ns

25 ns

20 ns

0 ns

20 ns

20 ns

12 seconds

8

21. Sector or Chip Erase Cycle Waveforms

8

Notes:

1. OE must be high only when WE and CE are both low.

2. For chip erase, the address should be 555. For sector erase, the address depends on what sector is to be erased.

(See note 4 under “Command Definition Table” on page 6.)

3. For chip erase, the data should be 10H, and for sector erase, the data should be 30H.

3359C–FLASH–3/05

11

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet AT49F040A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT49F040 | 5-volt-only in-system Flash Memory | ATMEL Corporation |

| AT49F040A | 5-volt only in-system reprogrammable Flash memory | ATMEL Corporation |

| AT49F040B | Flash Memory | ATMEL Corporation |

| AT49F040T | 5-volt-only in-system Flash Memory | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |