|

|

PDF CY22381 Data sheet ( Hoja de datos )

| Número de pieza | CY22381 | |

| Descripción | Three-PLL General Purpose Flash Programmable Clock Generator | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CY22381 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

CY22381

CY223811

Three-PLL General Purpose

Flash Programmable Clock Generator

Three-PLL General Purpose Flash Programmable Clock Generator

Features

■ Three integrated phase-locked loops

■ Ultra-wide divide counters (eight-bit Q, eleven-bit P, and

seven-bit post divide)

■ Improved linear crystal load capacitors

■ Flash programmability

■ Field programmability

■ Low-jitter, high-accuracy outputs

■ Power-management options (Shutdown, OE, Suspend)

■ Configurable crystal drive strength

■ Frequency select option through external LVTTL Input

■ 3.3 V operation

■ 8-pin small outline integrated circuit (SOIC) package

(CY22381)

■ 8-pin SOIC package with NiPdAu lead finish (CY223811)

■ CyClocks RT™ support

Functional Description

The CY22381 is the next-generation programmable Flash

programmable clock for use in networking, telecommunication,

datacom, and other general-purpose applications. The CY22381

offers up to three configurable outputs in a 8-pin SOIC, running

off a 3.3 V power supply. The on-chip reference oscillator is

designed to run off an 8–30-MHz crystal, or a 1–166-MHz

external clock signal. The CY22381 has a three PLLs driving 3

programmable output clocks. The output clocks are derived from

the PLL or the reference frequency (REF). Output post dividers

are available for either. The CY223811 is the CY22381 with

NiPdAu lead finish.

For a complete list of related documentation, click here.

Logic Block Diagram

XTALIN

XTALOUT

OSC.

CONFIGURATION

FLASH

SHUTDOWN/OE

FS/SUSPEND

PLL1

11-BIT P

8-BIT Q

PLL2

11-BIT P

8-BIT Q

PLL3

11-BIT P

8-BIT Q

4×3

Crosspoint

Switch

Divider

7-BIT

Divider

7-BIT

Divider

7-BIT

CLKC

CLKB

CLKA

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 38-07012 Rev. *K

• San Jose, CA 95134-1709 • 408-943-2600

Revised November 21, 2014

1 page

CY22381

CY223811

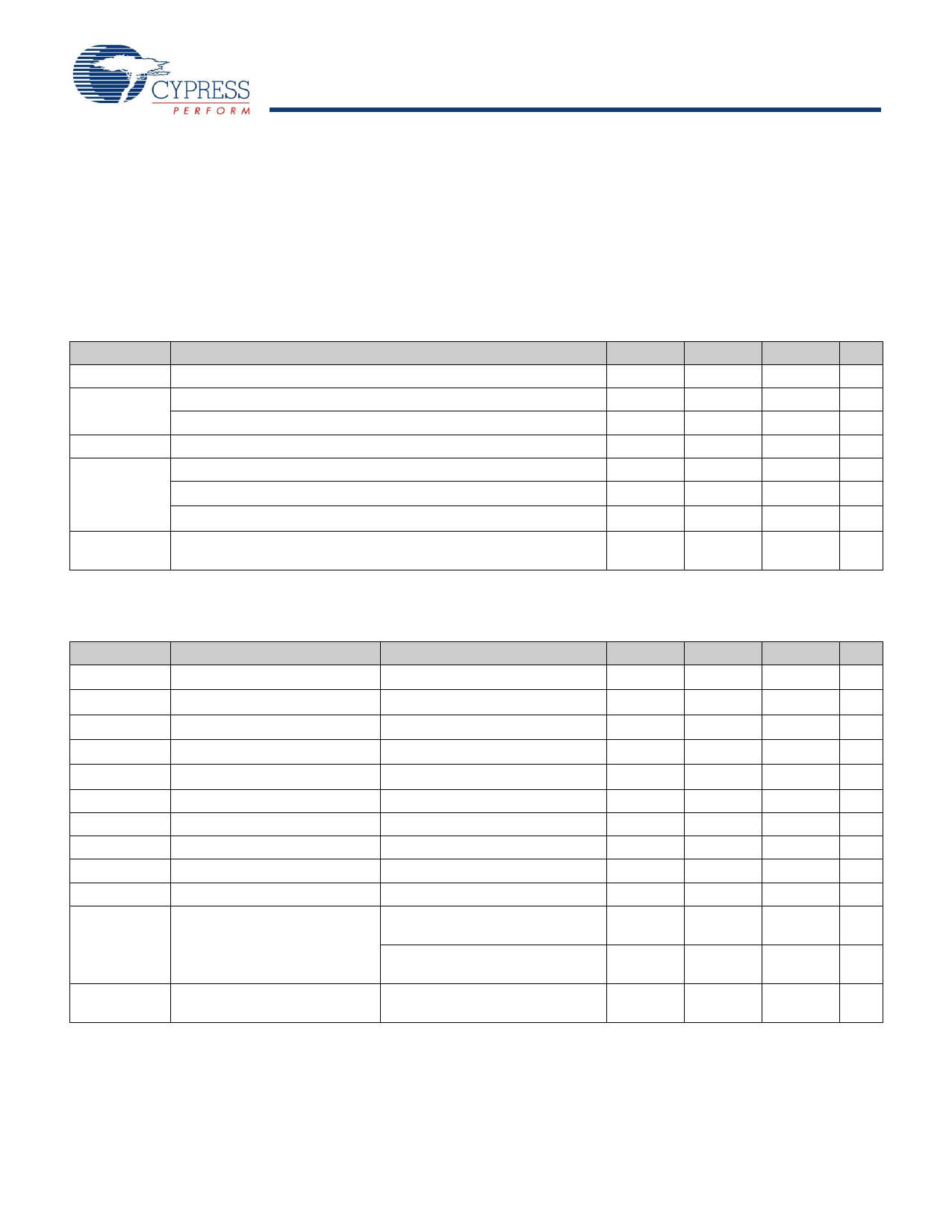

Maximum Ratings

Exceeding maximum ratings may shorten the useful life of the

device. User guidelines are not tested.

Supply voltage .............................................–0.5 V to +7.0 V

DC input voltage ............................–0.5 V to + (VDD + 0.5 V)

Storage temperature .................................... –65 °C +125 °C

Junction temperature ................................................. 125 °C

Data retention at Tj = 125 °C ................................> 10 years

Maximum programming cycles ........................................100

Package power dissipation ...................................... 250 mW

Static discharge voltage

(per MIL-STD-883, Method 3015) .......................... 2000V

Latch up (per JEDEC 17) ................................... ±200 mA

Operating Conditions

Parameter

Description

Min Typ Max Unit

VDD Supply voltage

TA Commercial operating temperature, ambient

Industrial operating temperature, ambient

3.135

3.3

3.465

V

0 – +70 °C

–40 – +85 °C

CLOAD_OUT

fREF

Max. load capacitance

External reference crystal

External reference clock [1], Commercial

– – 15 pF

8 – 30 MHz

1 – 166 MHz

External reference clock [1], Industrial

1 – 150 MHz

tPU Power up time for all VDD's to reach minimum specified voltage (power 0.05 – 500 ms

ramps must be monotonic)

Electrical Characteristics

Parameter

Description

Conditions [2]

Min Typ Max Unit

IOH

Output high current [3]

VOH = VDD – 0.5, VDD = 3.3 V

12 24

– mA

IOL

Output low current [3]

VOL = 0.5 V, VDD = 3.3 V

12 24

– mA

CXTAL_MIN

Crystal load capacitance [3]

Capload at minimum setting

– 6 – pF

CXTAL_MAX

Crystal load capacitance [3]

Capload at maximum setting

– 30 – pF

CIN

Input pin capacitance [3]

Except crystal pins

– 7 – pF

VIH

HIGH-level input voltage

CMOS levels,% of VDD

70%

–

– VDD

VIL

LOW-level input voltage

CMOS levels,% of VDD

–

–

30%

VDD

IIH Input HIGH current

VIN = VDD – 0.3 V

– <1 10 A

IIL Input LOW current

VIN = +0.3 V

– <1 10 A

IOZ

Output leakage current

Three-state outputs

– – 10 A

IDD

Total power supply current

3.3 V Power supply; 3 outputs at

–

35

– mA

50 MHz

3.3 V Power supply; 3 outputs at

–

70

– mA

166 MHz

IDDS

Total power supply current in

shutdown mode

Shutdown active

– 5 20 A

Notes

1. External input reference clock must have a duty cycle between 40% and 60%, measured at VDD/2.

2. Unless otherwise noted, Electrical and Switching Characteristics are guaranteed across these operating conditions.

3. Guaranteed by design, not 100% tested.

Document Number: 38-07012 Rev. *K

Page 5 of 14

5 Page

Package Drawing and Dimensions

Figure 7. 8-pin SOIC (150 Mils) Package Outline, 51-85066

CY22381

CY223811

51-85066 *F

Document Number: 38-07012 Rev. *K

Page 11 of 14

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet CY22381.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CY22381 | Three-PLL General Purpose Flash Programmable Clock Generator | Cypress Semiconductor |

| CY223811 | Three-PLL General Purpose Flash Programmable Clock Generator | Cypress Semiconductor |

| CY22388 | Factory Programmable Quad PLL Clock Generator | Cypress Semiconductor |

| CY22389 | Factory Programmable Quad PLL Clock Generator | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |