|

|

PDF BD9478F Data sheet ( Hoja de datos )

| Número de pieza | BD9478F | |

| Descripción | PWM pulse Generator | |

| Fabricantes | ROHM Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de BD9478F (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

BD9478F

Datasheet

LED Drivers series for LCD Backlights

PWM pulse Generator for

LCD Panels

BD9478F

●General Description

BD9478F is PWM pulse generator for LCD panel. This

IC compares triangle waveform which is generated

inside IC and external DC signal, and generates a

PWM pulse. This PWM pulse is provided to LED driver

and controls LED grayscale. PWM pulse frequency

can be synchronized to external signal frequency

inputted to SYNC terminal. Even if this frequency gets

out of range, it works in the setting frequency, is

protected and it always provides stable PWM pulse to

LED driver.

●Key Specification

Operating power supply voltage range: 4.5V to 5.5V

Free Run frequency:

150Hz (CT=0.01µF)

Operating Current:

Operating temperature range:

℃ ℃2mA (typ.)

-40 to +85

●Applications

LED backlight of monitor, TV, NOTE PC, etc.

●Features

■The signal that the frequency synchronizes with the

■VSYNC signal is output to PWMOUT.

The PWM pulse is generated with the DC signal of a

triangular wave and PDIM generated with the LCT

■capacitor.

When the VSYNC frequency exceeds the stipulated

range, it fixes by a set frequency.

(fSYNC<fPLLtyp*0.35 -> fPLL=0.36*fPLLtyp , fSYNC>

■fPLLtyp*2.75 -> fPLL=2.75*fPLLtyp)

When VSYNC is a no signal input, the self-oscillation is

■operated by set frequency decided on the CT capacitance.

When the pulse signal is input to the terminal EXTPWM,

it shifts automatically to external PWM mode.

●Package

SOP-8:

Pin Pitch:

W(Typ.) D(Typ.) H(Max.)

5.00mm x 6.20mm x 1.71mm

1.27mm

●Typical Application Circuit

CVCC

VIN

PDIM

fVSYNC

1 VCC

CEXTPWM

Connector CPDIM

CVSYNC

2 EXTPWM

3 PDIM

4 VSYNC

PWMOUT 8

PWM signal out

(to LED driver)

GND 7

CLPF1 CLPF2

LPF 6

RLPF2

CT 5

CCT

Figure 1. SOP-8

Figure 2. Typical Application Circuit

○ :Product structure Silicon monolithic integrated circuit

.www.rohm.com

・ ・© 2012 ROHM Co., Ltd. All rights reserved.

TSZ22111 14 001

○This product is not designed protection against radioactive rays

1/12

TSZ02201-0F1F0C100010-1-2

24. Jul.2012 Rev.002

1 page

BD9478F

●Block Diagram

Datasheet

EXTPWM

VCC

GND

Pulse VSYNC

signal

Phase

Comparetor

Frequency lock comparator

+

-

f×2.75

+

-

f×0.35

selector

-

+

f×0.15

LPF

Loop Filter

Voltage

Controlled

Oscillator

PWM comparator

-

+

selector

CT PDIM

DC

signal

PWMOUT

Figure 6. Block Diagram

www.rohm.com

・ ・© 2012 ROHM Co., Ltd. All rights reserved.

TSZ22111 15 001

5/12

TSZ02201-0F1F0C100010-1-2

24. Jul.2012 Rev.002

5 Page

BD9478F

Datasheet

●Operational Notes

1.) Although the quality of this product has been tightly controlled, deterioration or even destruction may occur if the absolute maximum

ratings, such as for applied pressure and operational temperature range, are exceeded. Furthermore, we are unable to assume short

or open mode destruction conditions. If special modes which exceed the absolute maximum ratings are expected, physical safely

precautions such as fuses should be considered.

2.) The IC can destruct from reverse connection of the power supply connector. Precautions, such as inserting a diode between t

he external power supply and IC power terminal, should be taken as protection against reverse connection destruction.

3.) When attaching to the printed substrate, pay special attention to the direction and proper placement of the IC. If the IC is att

ached incorrectly, it may be destroyed.

Destruction can also occur when there is a short, which can be caused by foreign objects entering between outputs or an output and the

power GND.

4.) Because there is a return of current regenerated by back EMF of the external coil, the capacity value should be determined af

ter confirming that there are no problems with characteristics such as capacity loss at low temperatures with electrolysis conde

nsers, for example by placing a condenser between the power supply and GND as a route for the regenerated current.

5.) The potential of the GND pin should be at the minimum potential during all operation status

6.) Heat design should consider power dissipation (Pd) during actual use and margins should be set with plenty of room.

7.) Exercise caution when operating in strong magnet fields, as errors can occur.

8.) When using this IC, it should be configured so that the output Tr should not exceed absolute maximum ratings and ASO. Wit

h CMOS ICs and ICs which have multiple power sources, there is a chance of rush current flowing momentarily, so exercise c

aution with power supply coupling capacity, power supply and width of GND pattern wiring and its layout.

9.) This IC has a built-in Temperature Protection Circuit (TSD circuit). The temperature protection circuit (TSD circuit) is only to cut

off the IC from thermal runaway, and has not been designed to protect or guarantee the IC. Therefore, the user should not

plan to activate this circuit with continued operation in mind.

10.) If a condenser is connected to a pin with low impedance when inspecting the set substrate, stress may be placed on the IC,

so there should be a discharge after each process. Furthermore, when connecting a jig for the inspection process, the power

must first be turned OFF before connection and inspection, and turned OFF again before removal.

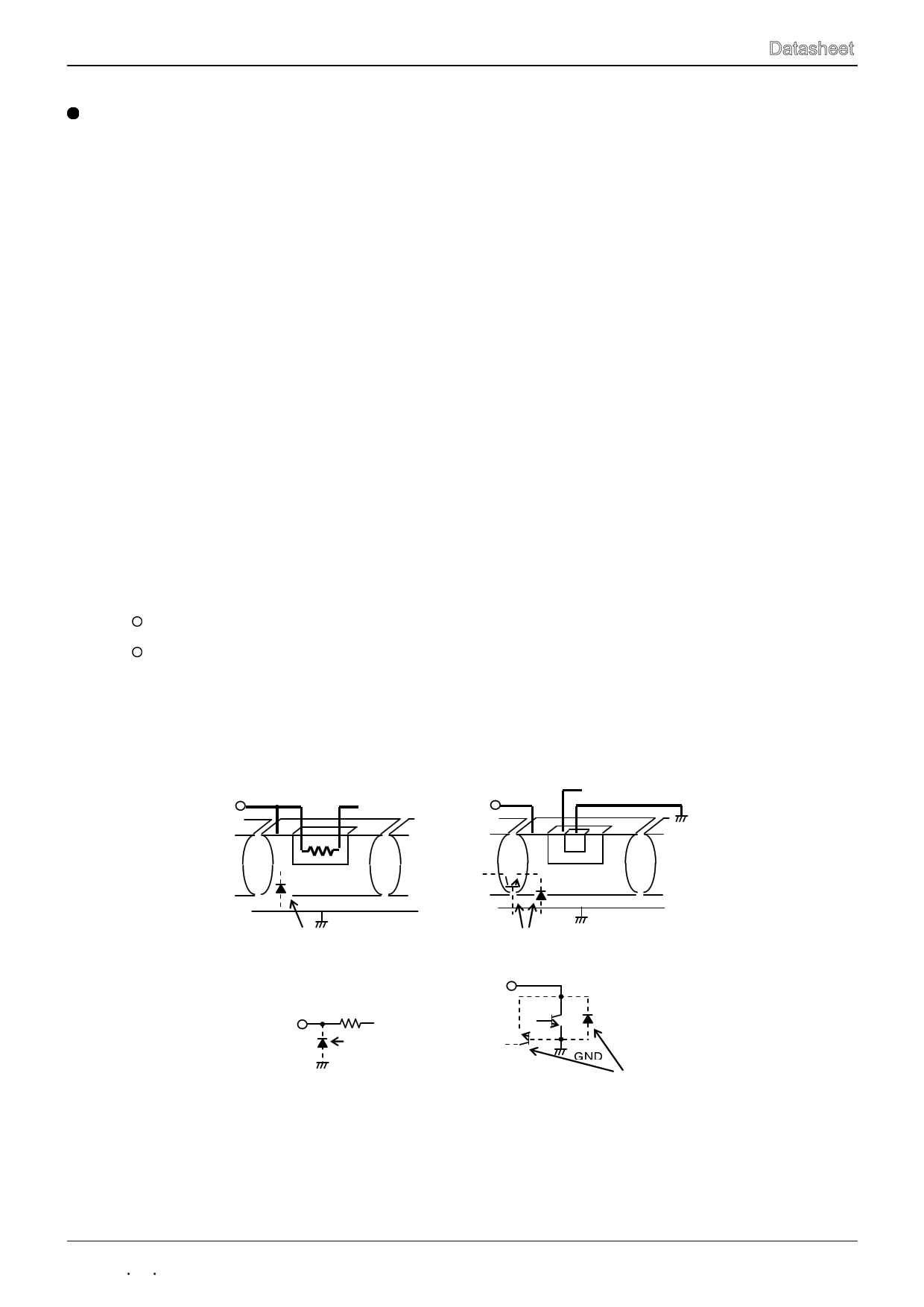

11.) This IC is a monolithic IC, and between each element there is a P+ isolation and P substrate for element separation.

There is a P-N junction formed between this P-layer and each element’s N-layer, which makes up various parasitic elements.

○For example, when resistance and transistor are connected with a terminal as in figure 15:

When GND>(terminal A) at the resistance, or GND>(terminal B) at the transistor (NPN), the P-N junction operates as a parasitic

○diode.

Also, when GND>(terminal B) at the transistor, a parasitic NPN transistor operates by the N-layer of other elements close to the

aforementioned parasitic diode.

With the IC’s configuration, the production of parasitic elements by the relationships of the electrical potentials is inevitable. The operation

of the parasitic elements can also interfere with the circuit operation, leading to malfunction and even destruction. Therefore, uses which

cause the parasitic elements to operate, such as applying voltage to the input terminal which is lower than the GND (P-substrate), should

be avoided.

(Pin A)

Resistor

(Pin B)

Transistor (NPN)

B

C

E

P

N

P

N

P

P substrate

GND

Parasitic element

N

P

N

N

P

N

P substrate

GND

P

N

GND

Parasitic element

(Pin B)

(Pin A)

BC

E

Parasitic element

GND

GND

Adjacent other elements

Parasitic

Figure 17. Example of Simple Structure of Monolithic IC

Status of this document

The Japanese version of this document is formal specification. A customer may use this translation version only for a reference

to help reading the formal version.

If there are any differences in translation version of this document formal version takes priority

www.rohm.com

・ ・© 2012 ROHM Co., Ltd. All rights reserved.

TSZ22111 15 001

11/12

TSZ02201-0F1F0C100010-1-2

24. Jul.2012 Rev.002

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet BD9478F.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| BD9478F | PWM pulse Generator | ROHM Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |