|

|

PDF S6E2HG4G0A Data sheet ( Hoja de datos )

| Número de pieza | S6E2HG4G0A | |

| Descripción | Microcontroller | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de S6E2HG4G0A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

S6E2HG Series

32-bit ARM® Cortex®-M4F

FM4 Microcontroller

Devices in the S6E2HG Series are highly integrated 32-bit microcontrollers with high performance and competitive cost. These

series is based on the ARM Cortex-M4F Processor with on-chip Flash memory and SRAM. The series has peripheral functions such

as Motor Control Timers, ADCs and Communication Interfaces (CAN, UART, CSIO, I2C, LIN).

Features

32-bit ARM Cortex-M4F Core

Processor version: r0p1

Up to 160 MHz Frequency Operation

FPU built-in

Support DSP instruction

Memory Protection Unit (MPU): improves the reliability of an

embedded system

Integrated Nested Vectored Interrupt Controller (NVIC): 1

NMI (non-maskable interrupt) and 128 peripheral interrupts

and 16 priority levels

24-bit System timer (Sys Tick): System timer for OS task

management

On-chip Memories

Flash memory

These series are based on two independent on-chip Flash

memories.

MainFlash memory

• Up to 512 Kbytes

• Built-in Flash Accelerator System with 16 Kbytes trace

buffer memory

• The read access to Flash memory can be achieved

without wait-cycle up to operation frequency of 72 MHz.

Even at the operation frequency more than 72 MHz, an

equivalent access to Flash memory can be obtained by

Flash Accelerator System.

• Security function for code protection

WorkFlash memory

• 32 Kbytes

• Read cycle:

• 6 wait-cycle: the operation frequency more than 120 MHz,

and up to 160 MHz

• 4 wait-cycle: the operation frequency more than 72 MHz,

and up to 120 MHz

• 2 wait-cycle: the operation frequency more than 40 MHz,

and up to 72 MHz

• 0 wait-cycle: the operation frequency up to 40 MHz

• Security function is shared with code protection

SRAM

This is composed of three independent SRAMs (SRAM0,

SRAM1 and SRAM2). SRAM0 is connected to I-code bus or

D-code bus of Cortex-M4F core. SRAM1 and SRAM2 are

connected to System bus of Cortex-M4F core.

SRAM0: Up to 32 Kbytes

SRAM1: Up to 16 Kbytes

SRAM2: Up to 16 Kbytes

External Bus Interface

Supports SRAM, NOR, NAND Flash and SDRAM device

Up to 9 chip selects CS0 to CS8 (CS8 is only for SDRAM)

8-/16-bit Data width

Up to 25-bit Address bit

Supports Address/Data multiplex

Supports external RDY function

Supports scramble function

• Possible to set the validity/invalidity of the scramble

function for the external areas 0x6000_0000 to

0xDFFF_FFFF in 4 Mbytes units.

• Possible to set two kinds of the scramble key

• Note: It is necessary to prepare the dedicated software

library to use the scramble function.

CAN Interface (Max 2 channels)

Compatible with CAN Specification 2.0A/B

Maximum transfer rate: 1 Mbps

Built-in 32 message buffer

Multi-function Serial Interface (Max 8 channels)

64 bytes with FIFO (the FIFO step numbers are variable

depending on the settings of the communication mode or bit

length.)

Operation mode is selectable from the followings for each

channel.

UART

CSIO

LIN

I2C

UART

Full-duplex double buffer

Selection with or without parity supported

Built-in dedicated baud rate generator

External clock available as a serial clock

Cypress Semiconductor Corporation

Document Number: 001-98943 Rev. *A

• 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600

Revised October 8, 2015

1 page

S6E2HG Series

Table of Contents

Features................................................................................................................................................................................... 1

1. Product Lineup............................................................................................................................................................... 7

2. Packages......................................................................................................................................................................... 9

3. Pin Assignment ............................................................................................................................................................ 10

4. Pin Description............................................................................................................................................................. 14

5. I/O Circuit Type............................................................................................................................................................. 43

6. Handling Precautions .................................................................................................................................................. 50

6.1 Precautions for Product Design ................................................................................................................................... 50

6.2 Precautions for Package Mounting.............................................................................................................................. 51

6.3 Precautions for Use Environment ................................................................................................................................ 53

7. Handling Devices ......................................................................................................................................................... 54

8. Block Diagram .............................................................................................................................................................. 57

9. Memory Size ................................................................................................................................................................. 58

10. Memory Map ................................................................................................................................................................. 58

11. Pin Status in Each CPU State...................................................................................................................................... 61

12. Electrical Characteristics ............................................................................................................................................ 68

12.1 Absolute Maximum Ratings......................................................................................................................................... 68

12.2 Recommended Operating Conditions.......................................................................................................................... 69

12.3 DC Characteristics....................................................................................................................................................... 73

12.3.1 Current Rating.............................................................................................................................................................. 73

12.3.2 Pin Characteristics ....................................................................................................................................................... 81

12.4 AC Characteristics....................................................................................................................................................... 83

12.4.1 Main Clock Input Characteristics.................................................................................................................................. 83

12.4.2 Sub Clock Input Characteristics ................................................................................................................................... 84

12.4.3 Built-in CR Oscillation Characteristics.......................................................................................................................... 84

12.4.4 Operating Conditions of Main PLL (In the Case of Using Main Clock for Input Clock of PLL)...................................... 85

12.4.5 Operating Conditions of Main PLL (In the Case of Using Built-in High-speed CR Clock

for Input Clock of Main PLL)......................................................................................................................................... 85

12.4.6 Reset Input Characteristics .......................................................................................................................................... 85

12.4.7 Power-on Reset Timing................................................................................................................................................ 86

12.4.8 GPIO Output Characteristics........................................................................................................................................ 87

12.4.9 External Bus Timing ..................................................................................................................................................... 88

12.4.10 Base Timer Input Timing......................................................................................................................................... 100

12.4.11 CSIO Timing ........................................................................................................................................................... 101

12.4.12 External Input Timing.............................................................................................................................................. 134

12.4.13 Quadrature Position/Revolution Counter Timing .................................................................................................... 135

12.4.14 I2C Timing............................................................................................................................................................... 137

12.4.15 SD Card Interface Timing ....................................................................................................................................... 140

12.4.16 ETM Timing ............................................................................................................................................................ 143

12.4.17 JTAG Timing........................................................................................................................................................... 144

12.5 12-bit A/D Converter.................................................................................................................................................. 145

12.6 12-bit D/A Converter.................................................................................................................................................. 148

12.7 Low-Voltage Detection Characteristics...................................................................................................................... 149

12.7.1 Low-Voltage Detection Reset..................................................................................................................................... 149

12.7.2 Interrupt of Low-Voltage Detection............................................................................................................................. 149

12.8 MainFlash Memory Write/Erase Characteristics........................................................................................................ 150

12.9 WorkFlash Memory Write/Erase Characteristics ....................................................................................................... 150

12.10 Standby Recovery Time ............................................................................................................................................ 151

Document Number: 001-98943 Rev. *A

Page 5 of 161

5 Page

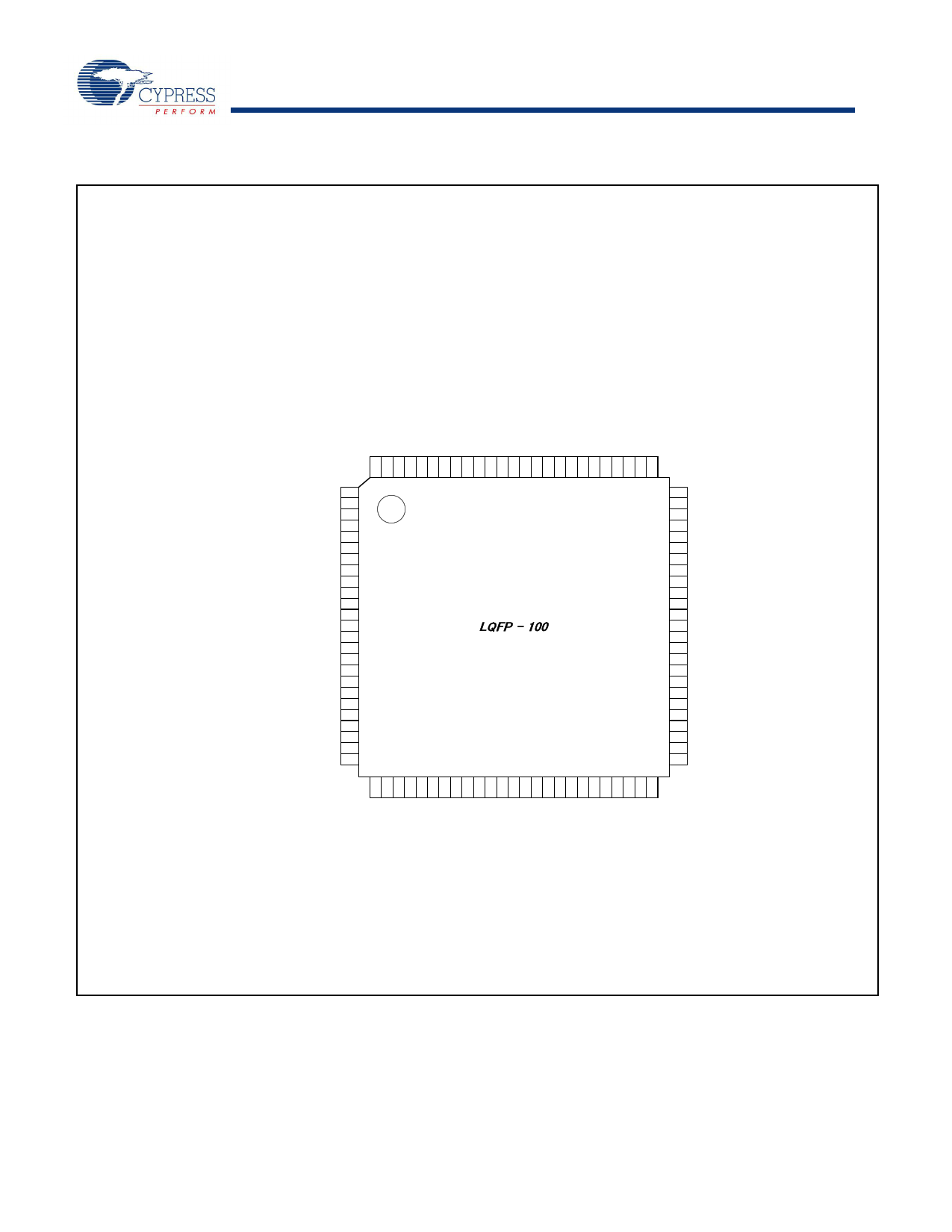

LQI100

(TOP VIEW)

S6E2HG Series

VCC

P50/CTS4_0/RTO10_0/AIN0_2/INT00_0/MADATA00_1

P51/RTS4_0/RTO11_0/BIN0_2/INT01_0/MADATA01_1

P52/SCK4_0/RTO12_0/ZIN0_2/MADATA02_1

P53/SOT4_0/RTO13_0/TIOA1_2/MADATA03_1

P54/SIN4_0/RTO14_0/TIOB1_2/INT02_0/MADATA04_1

P55/ADTG_1/SIN6_0/RTO15_0/INT07_2/MADATA05_1

P56/SOT6_0/DTTI1X_0/INT08_2/MADATA06_1

P30/RTS4_2/RTO25_1/TIOB0_1/INT15_2/WKUP1/MADATA07_1

P31/SIN3_1/DTTI2X_1/TIOB1_1/INT09_2/MADATA08_1

P32/SOT3_1/TIOB2_1/INT10_1/MADATA09_1

P33/ADTG_6/SCK3_1/TIOB3_1/INT04_0/MADATA10_1

P34/TX0_1/FRCK0_0/TIOB4_1/MADATA11_1

P35/RX0_1/IC03_0/TIOB5_1/INT08_1/MADATA12_1

P36/SIN5_2/IC02_0/INT09_1/MADATA13_1

P37/SOT5_2/IC01_0/INT05_2/MADATA14_1

P38/SCK5_2/IC00_0/INT06_2/MADATA15_1

P39/ADTG_2/DTTI0X_0/MCLK_1/RTCCO_2/SUBOUT_2

P3A/RTO00_0/TIOA0_1/AIN0_0/MCKE_1

P3B/RTO01_0/TIOA1_1/BIN0_0/MRASX_1

P3C/RTO02_0/TIOA2_1/ZIN0_0/MCASX_1

P3D/RTO03_0/TIOA3_1/MAD00_1

P3E/RTO04_0/TIOA4_1/MAD01_1

P3F/RTO05_0/TIOA5_1/MAD02_1

VSS

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

LQFP - 100

75 VSS

74 P20/AN18/RTO25_0/AIN1_1/INT05_0/MAD24_1

73 P21/AN17/SIN0_0/RTO24_0/BIN1_1/INT06_1/MAD23_1

72 P22/AN16/SOT0_0/RTO23_0/TIOB7_1/ZIN1_1/CROUT_0

71 P23/AN15/SCK0_0/RTO00_1/TIOA7_1/MAD22_1

70 P1E/AN14/ADTG_5/FRCK0_1/MAD21_1

69 P1D/AN13/RTS4_1/DTTI0X_1/MAD20_1

68 P1C/AN12/CTS4_1/IC03_1/MAD19_1

67 P1B/AN11/SCK4_1/IC02_1/MAD18_1

66 P1A/AN10/SOT4_1/IC01_1/MAD17_1

65 P19/AN09/SIN4_1/IC00_1/INT05_1/MAD16_1

64 P18/AN08/SCK2_2/DTTI2X_0/MAD15_1

63 AVRH

62 AVRL

61 AVSS

60 AVCC

59 P17/AN07/SOT2_2/RTO20_0/AIN2_2/WKUP3/MAD14_1

58 P16/AN06/SIN2_2/RTO21_0/BIN2_2/INT14_1/MAD13_1

57 P15/AN05/SCK0_1/RTO22_0/ZIN2_2/MAD12_1

56 P14/AN04/SOT0_1/IC03_2/MAD11_1

55 P13/AN03/SIN0_1/IC02_2/INT03_1/MAD10_1

54 P12/AN02/SCK1_1/IC01_2/MAD09_1/RTCCO_1/SUBOUT_1

53 P11/AN01/SOT1_1/TX1_2/IC00_2/MAD08_1

52 P10/AN00/SIN1_1/RX1_2/FRCK0_2/INT02_1/MAD07_1

51 VCC

Note:

− The number after the underscore ("_") in pin names such as XXX_1 and XXX_2 indicates the relocated port number. For these

pins, there are multiple pins that provide the same function for the same channel. Use the extended port function register

(EPFR) to select the pin.

Document Number: 001-98943 Rev. *A

Page 11 of 161

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S6E2HG4G0A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S6E2HG4G0A | Microcontroller | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |