|

|

PDF MAX11168 Data sheet ( Hoja de datos )

| Número de pieza | MAX11168 | |

| Descripción | SAR ADC | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX11168 (archivo pdf) en la parte inferior de esta página. Total 27 Páginas | ||

|

No Preview Available !

MAX11168

EVALUATION KIT AVAILABLE

16-Bit, 500ksps, ±5V SAR ADC with

Internal Reference in µMAX

General Description

The MAX11168 is a 16-bit, 500ksps, SAR ADC offering

excellent AC and DC performance with true bipolar input

range, internal reference, and small size. The MAX11168

measures a ±5V (10VP-P) input range while operat-

ing from a single 5V supply. A patented charge-pump

architecture allows direct sampling of high-impedance

sources. The MAX11168 integrates a low drift reference

with internal buffer, saving the cost and space of an exter-

nal reference.

This ADC achieves 92.3dB SNR and -101dB THD. The

MAX11168 guarantees 16-bit no-missing codes and ±0.75

LSB INL (typ).

The MAX11168 communicates using an SPI-compatible

serial interface at 2.5V, 3V, 3.3V, or 5V logic. The serial

interface can be used to daisy-chain multiple ADCs for mul-

tichannel applications and provides a busy indicator option

for simplified system synchronization and timing.

The MAX11168 is offered in a 10-pin, 3mm x 5mm,

µMAXM package and is specified over the -40°C to +85°C

temperature range.

Applications

●● Industrial Process Control

●● Data Acquisition Systems

●● Medical Instrumentation

●● Automatic Test Equipment

Selector Guide and Ordering Information appear at end of

data sheet.

Typical Operating Circuit

VDD

(5V)

1µF

VOVDD

(2.3V TO 5V)

1µF

MAX9632

±5V

10Ω

4.7nF

AIN+

AIN-

REF

10µF

16-BIT ADC

INTERFACE AND

CONTROL

MAX11168

REF

BUF

INTERNAL

REFERENCE

SCLK

DIN

DOUT

CNVST

GND

HOST

CONTROLLER

Benefits and Features

●● High DC/AC Accuracy Improves Measurement

Quality

• 16-Bit Resolution with No Missing Codes

• 500ksps Throughput Rates Without Pipeline Delay/

Latency

• 92.3dB SNR and -101dB THD at 10kHz

• 0.5 LSBRMS Input-Referred Noise

• ±0.2 LSB DNL (typ) and ±0.75 LSB INL (typ)

●● Highly Integrated ADC Saves Cost and Space

• ±7ppm/°C Internal Reference

• Internal Reference Buffer

• ±5V Bipolar Analog Input Range

●● Wide Supply Range and Low Power Simplify

Power-Supply Design

• 5V Analog Supply

• 2.3V to 5V Digital Supply

• 37.6mW Power Consumption at 500ksps

• 10µA in Shutdown Mode

●● Multi-Industry Standard Serial Interface and Small

Package Reduce Size

• SPI/QSPI™/MICROWIRE®/DSP-Compatible Serial

Interface

• 3mm x 5mm Tiny 10-Pin µMAX Package

µMAX is a registered trademark of Maxim Integrated Products, Inc.

QSPI is a trademark of Motorola, Inc.

MICROWIRE is a registered trademark of National

Semiconductor Corporation.

For related parts and recommended products to use with this part, refer

to www.maximintegrated.com/MAX11168.related.

16-Bit to 18-Bit SAR ADC Family

16 BIT/

250ksps

±5V Input MAX11167

Internal REF MAX11169

16 BIT/

500ksps

MAX11166

MAX11168

18 BIT/

500ksps

MAX11156

MAX11158

+5V Input MAX11165

Internal REF MAX11161

MAX11164

MAX11160

MAX11154

MAX11150

+5V Input

External REF

MAX11163

MAX11162

MAX11152

19-7396; Rev 2; 1/15

1 page

MAX11168

16-Bit, 500ksps, ±5V SAR ADC with

Internal Reference in µMAX

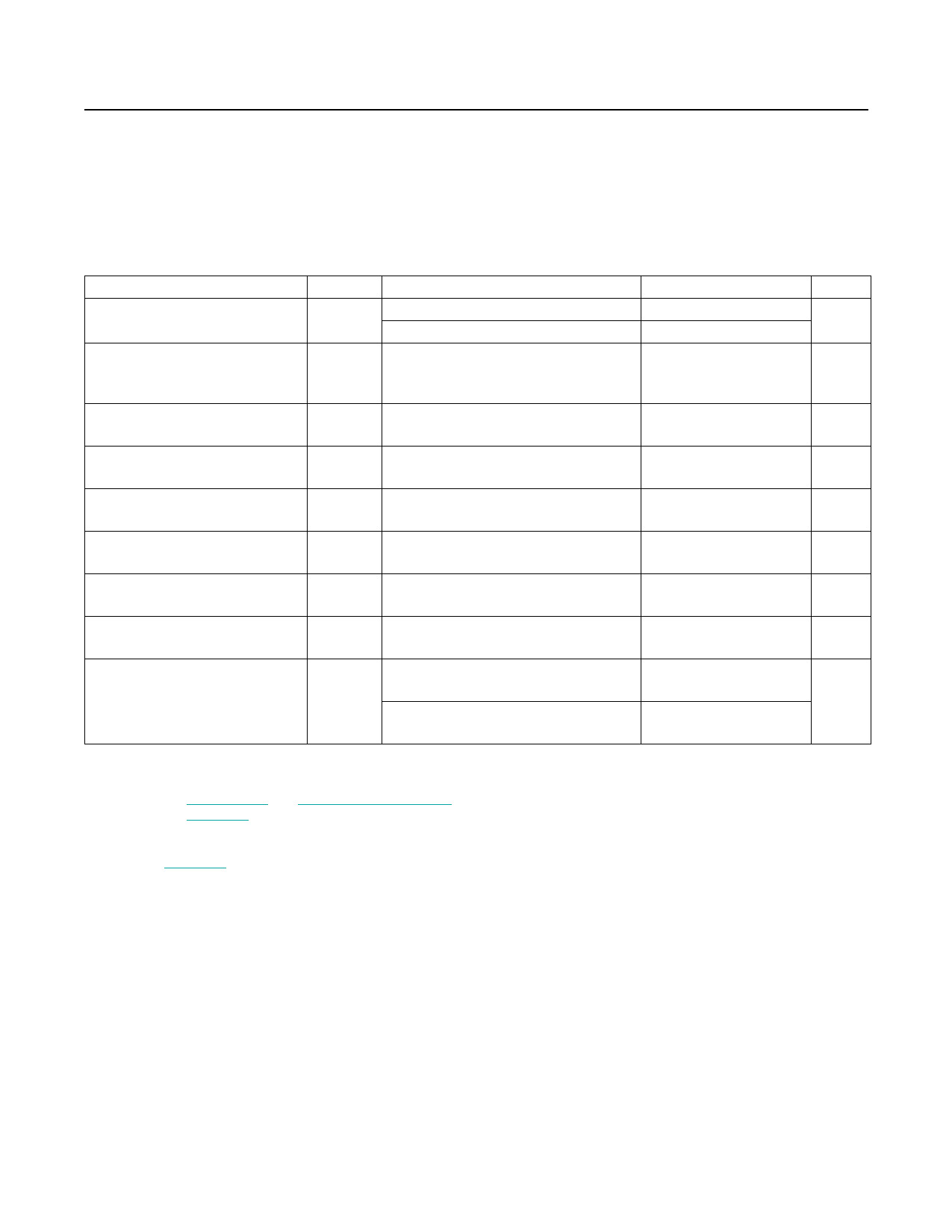

Electrical Characteristics (continued)

(VDD = 4.75V to 5.25V, VOVDD = 2.3V to 5.25V, fSAMPLE = 500kHz; TA = TMIN to TMAX, unless otherwise noted. Typical values are

at TA = +25°C.) (Note 2)

PARAMETER

CNVST Low to SDO D15 MSB Valid

(CS Mode)

CNVST High or SDI High or Last

SCLK Falling Edge to SDO High

Impedance

SYMBOL

tEN

tDIS

CONDITIONS

VOVDD > 2.7V

VOVDD < 2.7V

CS mode

MIN TYP MAX UNITS

14

ns

17

20 ns

SDI Valid Setup Time from CNVST

Rising Edge

tSSDISCK 4-wire CS mode

5 ns

SDI Valid Hold Time from SCLK

Rising Edge

tHSDISCK 4-wire CS mode

0 ns

SCLK Valid Setup Time from CNVST

Rising Edge

tSSCKCNV

Daisy-chain mode

5 ns

SCLK Valid Hold Time from CNVST

Rising Edge

tHSCKCNV Daisy-chain mode

5 ns

SDI Valid Setup Time from SCLK

Falling Edge

tSSDISCK Daisy-chain mode

5 ns

SDI Valid Hold Time from SCLK

Falling Edge

tHSDISCK Daisy-chain mode

0 ns

SDI High to SDO High

tDSDOSDI

Daisy-chain mode with busy indicator,

VOVDD > 4.5V

Daisy-chain mode with busy indicator,

VOVDD > 2.3V

15

ns

26

Note 2: Maximum and minimum limits are fully production tested over specified supply voltage range and at a temperature of +25°C

and +85°C. Limits below +25°C are guaranteed by design and device characterization. Typical values are not guaranteed.

Note 3: See the Analog Inputs and Overvoltage Input Clamps sections.

Note 4: See the Definitions section.

Note 5: Defined as the change in positive full-scale code transition caused by a ±5% variation in the VDD supply voltage.

Note 6: 10kHz sine wave input, -0.1dB below full scale.

Note 7: See Definitions section.

Note 8: fIN1 ~ 9.4kHz, fIN2 ~ 10.7kHz, Each tone at -6.1dB below full scale.

Note 9: CLOAD = 65pF on SDO.

www.maximintegrated.com

Maxim Integrated │ 5

5 Page

MAX11168

Pin Configuration

16-Bit, 500ksps, ±5V SAR ADC with

Internal Reference in µMAX

TOP VIEW

REF

VDD

AIN+

AIN-

GND

1+

2

3 MAX11168

4

5

10

9

8

7

6

µMAX

OVDD

SDI

SCLK

SDO

CNVST

Pin Description

PIN NAME

FUNCTION

1

REF

Internal Reference Bypass. Bypass to GND in close proximity with a X5R or X7R 10μF 16V chip. See the

Layout, Grounding, and Bypassing section.

2

VDD

Analog Power Supply. Bypass VDD to GND with a 0.1µF capacitor as close as possible to each device and

one 10µF capacitor per board.

3 AIN+ Positive Analog Input

4 AIN- Negative Analog Input. Connect AIN- to the analog ground plane or to a remote sense ground.

5 GND Power-Supply Ground

Conversion Start Input. The rising edge of CNVST initiates the conversions and selects the interface mode:

6 CNVST daisy-chain or CS. In CS mode, either SDI or CNVST can enable the serial output signals when low. If SDI or

CNVST is low when the conversion is completed, the busy indicator feature is enabled..

7 SDO Serial Data Output. SDO transitions on the falling edge of SCLK.

8 SCLK Serial Clock Input. Clocks data out of the serial interface when the device is selected.

Serial Data Input and Mode Select Input. Daisy-chain mode is selected if SDI is low during the CNVST rising

edge. In this mode, SDI is used as a data input to daisy-chain the conversion results of two or more ADCs

9 SDI onto a single SDO line. CS mode is selected if SDI is high during the CNVST rising edge. In this mode, either

SDI or CNVST can enable the serial output signals when low. If SDI or CNVST is low when the conversion is

completed, the busy indicator feature is enabled.

10

OVDD

Digital Power Supply. OVDD can range from 2.3V to VDD. Bypass OVDD to GND with a 0.1µF capacitor for

each device and one 10µF per board.

www.maximintegrated.com

Maxim Integrated │ 11

11 Page | ||

| Páginas | Total 27 Páginas | |

| PDF Descargar | [ Datasheet MAX11168.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX1116 | (MAX1115 / MAX1116) Single-Supply / Low-Power / Serial 8-Bit ADCs | Maxim Integrated |

| MAX11160 | SAR ADC | Maxim Integrated |

| MAX11161 | SAR ADC | Maxim Integrated |

| MAX11162 | SAR ADC | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |