|

|

PDF AD9824 Data sheet ( Hoja de datos )

| Número de pieza | AD9824 | |

| Descripción | Complete 14-Bit 30 MSPS CCD Signal Processor | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD9824 (archivo pdf) en la parte inferior de esta página. Total 25 Páginas | ||

|

No Preview Available !

a

FEATURES

14-Bit 30 MSPS A/D Converter

30 MSPS Correlated Double Sampler (CDS)

4 dB ؎ 6 dB 6-Bit Pixel Gain Amplifier (PxGA®)

2 dB to 36 dB 10-Bit Variable Gain Amplifier (VGA)

Low Noise Clamp Circuits

Analog Preblanking Function

Auxiliary Inputs with VGA and Input Clamp

3-Wire Serial Digital Interface

3 V Single-Supply Operation

Low Power: 153 mW @ 3 V Supply

Space-Saving 48-Lead LFCSP Package

APPLICATIONS

High Performance Digital Still Cameras

Industrial/Scientific Imaging

Complete 14-Bit 30 MSPS

CCD Signal Processor

AD9824

PRODUCT DESCRIPTION

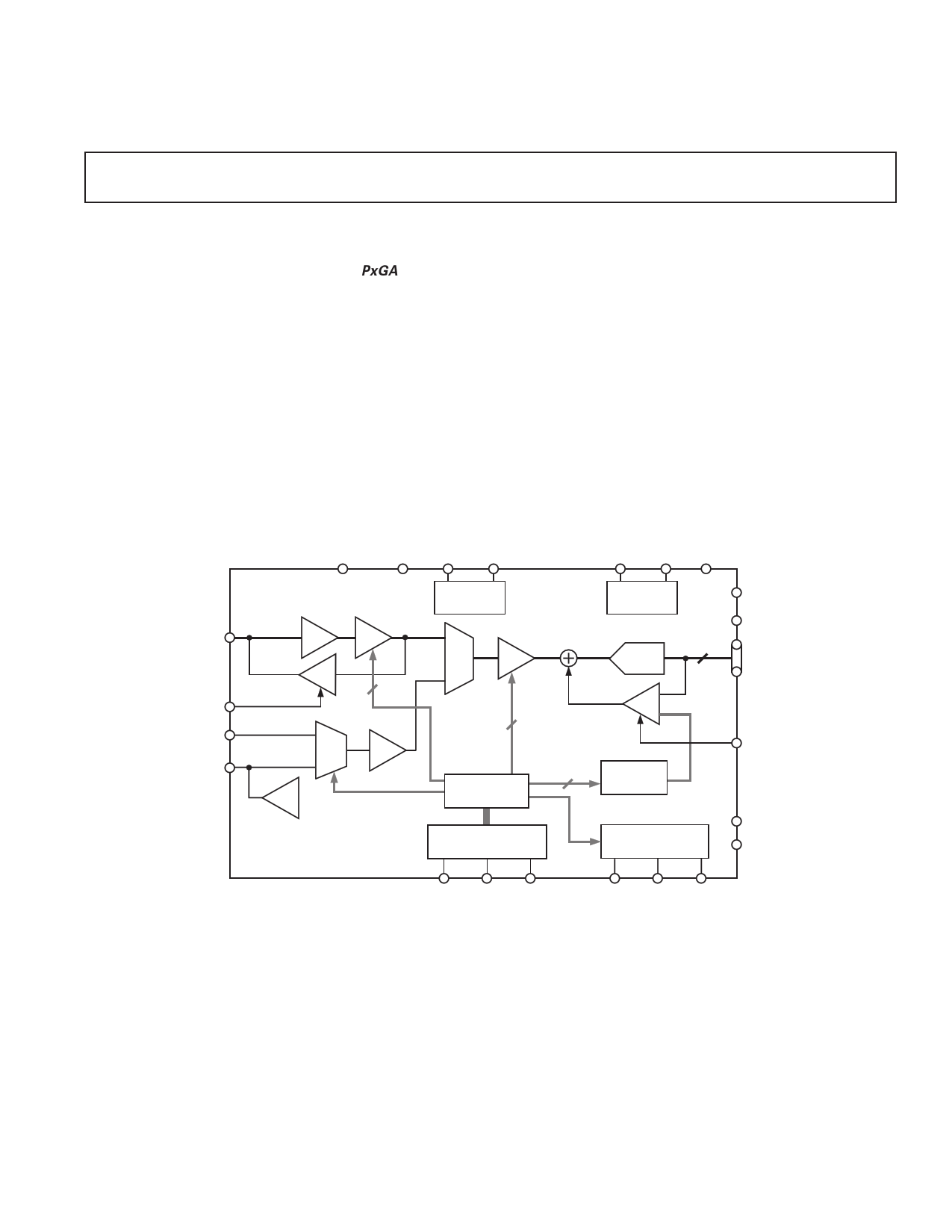

The AD9824 is a complete analog signal processor for CCD

applications. It features a 30 MHz single-channel architecture

designed to sample and condition the outputs of interlaced and

progressive scan area CCD arrays. The AD9824’s signal chain

consists of an input clamp, a correlated double sampler (CDS),

PxGA, a digitally controlled VGA, a black level clamp, and a

14-bit A/D converter. Additional input modes are also pro-

vided for processing analog video signals.

The internal registers are programmed through a 3-wire

serial digital interface. Programmable features include gain

adjustment, black level adjustment, input configuration, and

power-down modes.

The AD9824 operates from a single 3 V power supply, typically

dissipates 153 mW, and is packaged in a 48-lead LFCSP.

CCDIN

CLPDM

AUX1IN

AUX2IN

FUNCTIONAL BLOCK DIAGRAM

AVDD

AVSS

HD

VD

VRT

VRB PBLK

4dB ؎ 6dB

CDS

PxGA

CLP

6

2:1

MUX

BUF

CLP

AD9824

COLOR

STEERING

2:1

MUX

2dB~36dB

VGA

BAND GAP

REFERENCE

ADC

DRVDD

DRVSS

14 DOUT

10

CONTROL

REGISTERS

DIGITAL

INTERFACE

CLP

8 BLK CLAMP

LEVEL

INTERNAL

TIMING

CLPOB

DVDD

DVSS

SL SCK SDATA

SHP SHD DATACLK

PxGA is a registered trademark of Analog Devices, Inc.

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2002

1 page

AD9824–SPECIFICATIONS

AUX1-MODE SPECIFICATIONS (TMIN to TMAX, AVDD = DVDD = 3.0 V, fDATACLK = 30 MHz, unless otherwise noted.)

Parameter

Min

Typ

Max

Unit

POWER CONSUMPTION

120 mW

MAXIMUM CLOCK RATE

30

MHz

INPUT BUFFER

Gain

Max Input Range

0

1.0

dB

V p-p

VGA

Max Output Range

Gain Control Resolution

Gain (Selected Using VGA Gain Register)

Min Gain

Max Gain

2.0

1023

0

36

V p-p

Steps

dB

dB

Specifications subject to change without notice.

AUX2-MODE SPECIFICATIONS (TMIN to TMAX, AVDD = DVDD = 3.0 V, fDATACLK = 30 MHz, unless otherwise noted.)

Parameter

Min

Typ

Max

Unit

POWER CONSUMPTION

120 mW

MAXIMUM CLOCK RATE

30

MHz

INPUT BUFFER

(Same as AUX1-MODE)

VGA

Max Output Range

Gain Control Resolution

Gain (Selected Using VGA Gain Register)

Min Gain

Max Gain

2.0

512

0

18

V p-p

Steps

dB

dB

ACTIVE CLAMP

Clamp Level Resolution

Clamp Level (Measured at ADC Output)

Min Clamp Level

Max Clamp Level

256

0

1020

Steps

LSB

LSB

Specifications subject to change without notice.

–4– REV. 0

5 Page

AD9824

PIXEL GAIN AMPLIFIER (PxGA) TIMING

VD FRAME N

FRAME N+1

0101...

2323...

0101...

0101...

2323...

0101...

HD

LINE 0

LINE 1

LINE 2

LINE M–1

LINE M

LINE 0

LINE 1

LINE 2

LINE M–1

*0 = GAIN0, 1 = GAIN1, 2 = GAIN2, 3 = GAIN3

Figure 8. PxGA Mode 1 (Mosaic Separate) Frame/Line Gain Register Sequence

LINE M

5 PIXEL MIN

VD

HD

3ns MIN

3ns MIN

SHP

PxGA GAIN

GAINX

GAIN0

GAIN1 GAIN0

GAINX

NOTES

1. MINIMUM PULSEWIDTH FOR HD AND VD IS 5 PIXEL CYCLES.

2. BOTH VD AND HD ARE INTERNALLY UPDATED AT SHP RISING EDGES. MINIMUM SETUP TIME IS 3 ns.

3. EVERY HD RISING EDGE WITH A PREVIOUS VD RISING EDGE WILL RESET TO 0101.

4. EVERY HD RISING EDGE WITHOUT A PREVIOUS VD RISING EDGE WILL ALTERNATE BETWEEN 0101... AND 2323.

Figure 9. PxGA Mode 1 (Mosaic Separate) Detailed Timing

GAIN2

GAIN3

VD EVEN FIELD

ODD FIELD

0101...

2323...

0101...

0101...

2323...

0101...

HD

LINE 0

LINE 1

LINE 2

LINE M–1

LINE M

LINE 0

LINE 1

LINE 2

LINE M–1

*0 = GAIN0, 1 = GAIN1, 2 = GAIN2, 3 = GAIN3

Figure 10. PxGA Mode 2 (Interlace) Frame/Line Gain Register Sequence

LINE M

VD

5 PIXEL MIN

HD

3ns MIN

3ns MIN

SHP

PxGA

GAIN

GAINX GAIN0

GAIN1

GAIN0

GAINX

NOTES

1. BOTH VD AND HD ARE INTERNALLY UPDATED AT SHP RISING EDGES.

2. EVERY HD RISING EDGE WITH A PREVIOUS VD RISING OR FALLING EDGE WILL RESET TO 0101.

3. EVERY HD RISING EDGE WITHOUT A PREVIOUS VD RISING EDGE WILL ALTERNATE BETWEEN 0101... AND 2323.

Figure 11. PxGA Mode 2 (Interlace) Detailed Timing

GAIN2

GAIN3

–10–

REV. 0

11 Page | ||

| Páginas | Total 25 Páginas | |

| PDF Descargar | [ Datasheet AD9824.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD9821 | Complete 12-Bit 40 MSPS Imaging Signal Processor | Analog Devices |

| AD9822 | Complete 14-Bit CCD/CIS Signal Processor | Analog Devices |

| AD9823 | Correlated Double Sampler (CDS) | Analog Devices |

| AD9824 | Complete 14-Bit 30 MSPS CCD Signal Processor | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |