|

|

PDF 843S1333D Data sheet ( Hoja de datos )

| Número de pieza | 843S1333D | |

| Descripción | Crystal-to-3.3V LVPECL Clock Synthesizer | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 843S1333D (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

Crystal-to-3.3V LVPECL Clock

Synthesizer

843S1333D

Data Sheet

General Description

The 843S1333D is a high frequency clock generator. The

843S1333D uses an external 20MHz crystal to synthesize

1333.33MHz. The 843S1333D has excellent cycle-to-cycle and

RMS period jitter performance.

The 843S1333D operates at 3.3V operating supply and is available

in a fully RoHS compliant 8-lead TSSOP package.

Features

• One differential LVPECL output

• Crystal oscillator interface designed for 18pF, 20MHz parallel

resonant crystal

• Cycle-to-Cycle Jitter: 14ps (maximum)

• Period Jitter, RMS: 2.6ps (maximum)

• Output Duty Cycle: 48 – 52%

• Full 3.3V supply mode

• 0°C to 70°C ambient operating temperature

• Available in lead-free (RoHS 6) package

Table 1. Frequency Table

Crystal Frequency (MHz)

20

Multiplier Value

66.67

Output Frequency (MHz)

1333.33

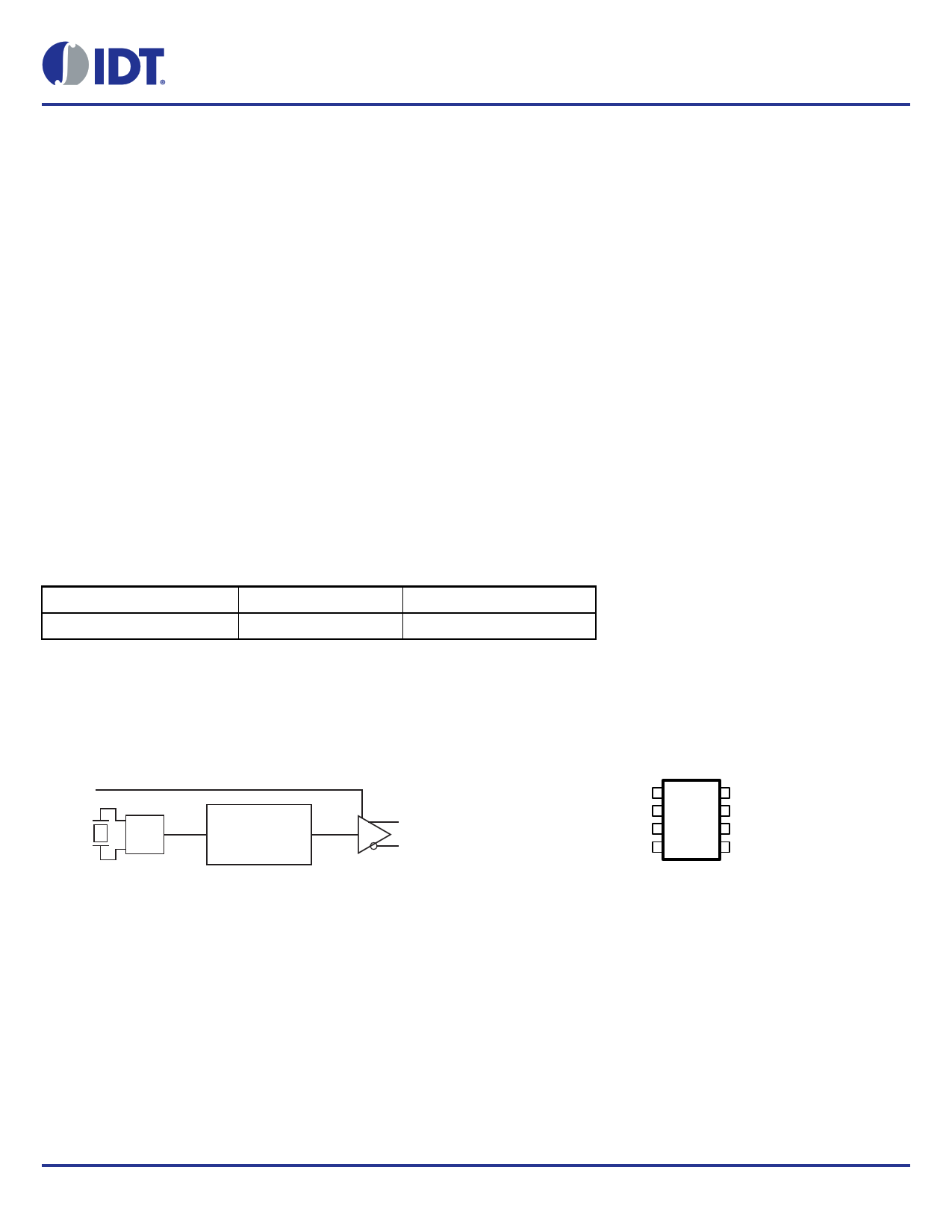

Block Diagram

OE Pullup

20MHz

XTAL_IN

OSC

XTAL_OUT

PLL Multiplier

(x66.67)

Q

nQ

Pin Assignment

VCCA

VEE

XTAL_OUT

XTAL_IN

1

2

3

4

8 VCC

7Q

6 nQ

5 OE

843S1333D

8 Lead TSSOP

4.40mm x 3.0mm x 0.925mm package body

G Package

Top View

©2015 Integrated Device Technology, Inc

1

Revision A December 2, 2015

1 page

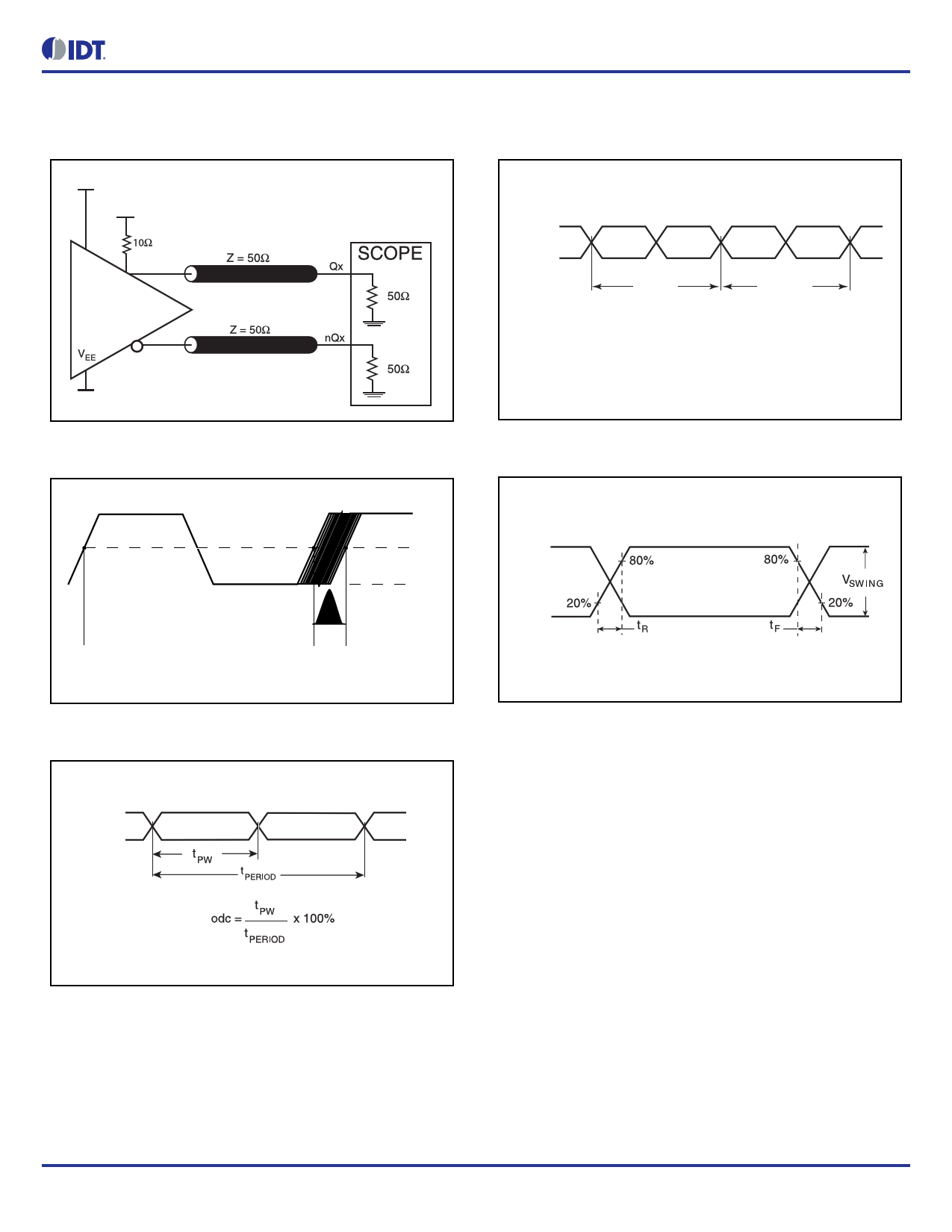

Parameter Measurement Information

2V

2V

VCC

VCCA

843S1333D Data Sheet

nQ

Q

tcycle n

tcycle n+1

| |tjit(cc) = tcycle n – tcycle n+1

1000 Cycles

-1.3V±0.165V

3.3V LVPECL Output Load AC Test Circuit

Cycle-to-Cycle Jitter

VOH

VREF

1σ contains 68.26% of all measurements

2σ contains 95.4% of all measurements

3σ contains 99.73% of all measurements

4σ contains 99.99366% of all measurements

6σ contains (100-1.973x10-7)% of all measurements

Reference Point

(Trigger Edge)

Histogram

Mean Period

(First edge after trigger)

VOL

RMS Period Jitter

nQ

Q

Output Rise/Fall Time

nQ

Q

Output Duty Cycle/Pulse Width/Period

©2015 Integrated Device Technology, Inc

5

Revision A December 2, 2015

5 Page

3. Calculations and Equations.

The purpose of this section is to calculate the power dissipation for the LVPECL output pair.

LVPECL output driver circuit and termination are shown in Figure 6.

VCC

843S1333D Data Sheet

Q1

VOUT

RL

VCC - 2V

Figure 6. LVPECL Driver Circuit and Termination

To calculate worst case power dissipation into the load, use the following equations which assume a 50 load, and a termination voltage of

VCC – 2V.

• For logic high, VOUT = VOH_MAX = VCC_MAX – 0.8V

(VCC_MAX – VOH_MAX) = 0.8V

• For logic low, VOUT = VOL_MAX = VCC_MAX – 1.6V

(VCC_MAX – VOL_MAX) = 1.6V

Pd_H is power dissipation when the output drives high.

Pd_L is the power dissipation when the output drives low.

Pd_H = [(VOH_MAX – (VCC_MAX – 2V))/RL] * (VCC_MAX – VOH_MAX) = [(2V – (VCC_MAX – VOH_MAX))/RL] * (VCC_MAX – VOH_MAX) =

[(2V – 0.8V)/50] * 0.8V = 19.2mW

Pd_L = [(VOL_MAX – (VCC_MAX – 2V))/RL] * (VCC_MAX – VOL_MAX) = [(2V – (VCC_MAX – VOL_MAX))/RL] * (VCC_MAX – VOL_MAX) =

[(2V – 1.6V)/50] * 1.6V = 12.8mW

Total Power Dissipation per output pair = Pd_H + Pd_L = 32mW

©2015 Integrated Device Technology, Inc

11

Revision A December 2, 2015

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet 843S1333D.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 843S1333D | Crystal-to-3.3V LVPECL Clock Synthesizer | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |