|

|

PDF MG69L331 Data sheet ( Hoja de datos )

| Número de pieza | MG69L331 | |

| Descripción | 8-Bit Micro-Controller | |

| Fabricantes | Megawin | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MG69L331 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

笙泉科技股份有限公司

Megawin Technology Co., Ltd.

Version: 2.0

MG69L331

Data Sheet

8-Bit Micro-Controller with

IR function

This document information is the intellectual property of Megawin Technology.

Megawin Technology Co., Ltd. 2011 All right reserved.

QP-7300-03D

1/28

Version 2.0

1 page

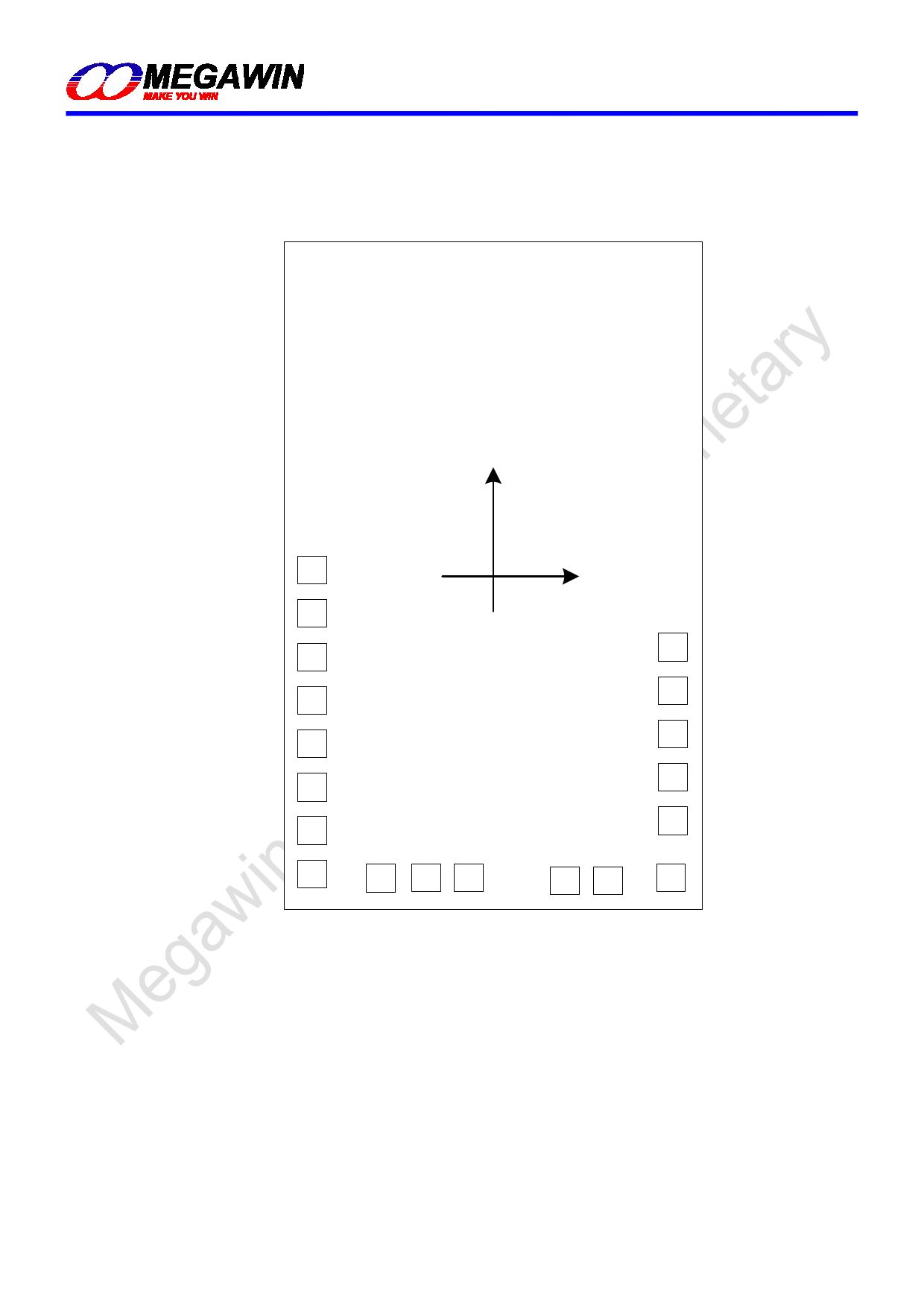

3 Pin Configurations

3.1 Pad Assignment

MG69L331 Datasheet

Version 2.0

P0.6

P0.5

P0.4

P0.3

P0.2

P0.1

P0.0

OSCI/P2.0

1

2

3

4

5

6

7

8

(0,0)

9 10 11

12 13

19 P0.7

18 P1.0

17 P1.1

16 P1.2

15 P1.3

14 P1.4

Figure 3-1 Pad Assignment

This document information is the intellectual property of Megawin Technology.

Megawin Technology Co., Ltd. 2011 All right reserved.

QP-7300-03D

5/28

5 Page

MG69L331 Datasheet

Version 2.0

7 Interrupt

The MG69L331A provides 6 interrupt sources: P0, P1, IRI, TM0, TM1 and divider. Each of the Interrupt sources

can be individually enabled or disabled by setting or clearing the corresponding bit in the IRQen. Six interrupts

share the interrupt vector FFFEH/FFFFH.

Examples:

DIV interrupt: When IRQen.DIVen = 1 and DIVevt = 1.

P0 interrupt: When IRQen.P0en = 1 and P0evt = 1.

TM0 interrupt: IRQen.TM0en = 1 and TM0evt = 1.

Interrupt Vectors

Vector Address

FFFCH, FFFDH

“

“

FFFEH, FFFFH

“

“

“

“

“

Item

RESET

WDT

LVR

P0

P1

IRI

DIV

TM0

TM1

Flag

None

WDTirq

None

P0irq

P1irq

IRIirq

DIVirq

TM0irq

TM1irq

Properties

Ext.

Int.

Ext.

Ext.

Ext.

Ext.

Int.

Int.

Int.

Memo

Initial reset

Watch dog reset

Low voltage reset

Port P0 interrupt vector

Port P1 interrupt vector

IRI interrupt vector

Divider carry out interrupt

TM0 underflow interrupt

TM1 underflow interrupt

IRQen .TM1en

TM1evt

IRQen .TM0en

TM0evt

IRQen.P1en

P1evt

IRQen.P0en

P0evt

IRQen .DIVen

DIVevt

IRQen .IRIen

IRIevt

Interrupt Architecture

Interrupt

(to CPU )

7.1 Interrupt Register

IRQ enable flag

Address Name Bit 7 Bit 6 Bit 5 Bit 4

Bit 3

Bit 2 Bit 1 Bit 0

00E2H IRQen IRI

-

-

DIV

TM0

TM1

P1

P0

Programmer can enable or disable the ability of triggering IRQ through this register.

0: Disable (default "0" at initialization)

1: Enable

P0 (or P1): Falling edge occurs at port 0 (or port 1) input mode

TM1 (or TM0): Timer1 (or Timer 0) underflow occurred.

DIV: DIV interrupts frequency occurred

IRI: Edge occurs at IR pin in input mode

RW

This document information is the intellectual property of Megawin Technology.

Megawin Technology Co., Ltd. 2011 All right reserved.

QP-7300-03D

11/28

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet MG69L331.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MG69L331 | 8-Bit Micro-Controller | Megawin |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |