|

|

PDF CS2000-OTP Data sheet ( Hoja de datos )

| Número de pieza | CS2000-OTP | |

| Descripción | Fractional-N Clock Synthesizer & Clock Multiplier | |

| Fabricantes | Cirrus Logic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CS2000-OTP (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CS2000-OTP

Fractional-N Clock Synthesizer & Clock Multiplier

Features

Delta-Sigma Fractional-N Frequency Synthesis

– Generates a Low Jitter 6 - 75 MHz Clock

from an 8 - 75 MHz Reference Clock

Clock Multiplier / Jitter Reduction

– Generates a Low Jitter 6 - 75 MHz Clock

from a Jittery 50 Hz to 30 MHz Clock

Source

Highly Accurate PLL Multiplication Factor

– Maximum Error Less Than 1 PPM in High-

Resolution Mode

One-Time Programmability

– Configurable Hardware Control Pins

– Configurable Auxiliary Output

Flexible Sourcing of Reference Clock

– External Oscillator or Clock Source

– Supports Inexpensive Local Crystal

Minimal Board Space Required

– No External Analog Loop-filter

Components

General Description

The CS2000-OTP is an extremely versatile system

clocking device that utilizes a programmable phase lock

loop. The CS2000-OTP is based on a hybrid analog-

digital PLL architecture comprised of a unique combina-

tion of a Delta-Sigma Fractional-N Frequency

Synthesizer and a Digital PLL. This architecture allows

for both frequency synthesis/clock generation from a

stable reference clock as well as generation of a low-jit-

ter clock relative to an external noisy synchronization

clock with frequencies as low as 50 Hz. The CS2000-

OTP has many configuration options which are set once

prior to runtime. At runtime there are three hardware

configuration pins available for mode and feature

selection.

The CS2000-OTP is available in a 10-pin MSOP pack-

age in Commercial (-10°C to +70°C) grade. Customer

development kits are also available for custom device

prototyping, small production programming, and device

evaluation. Please see “Ordering Information” on

page 29 for complete details.

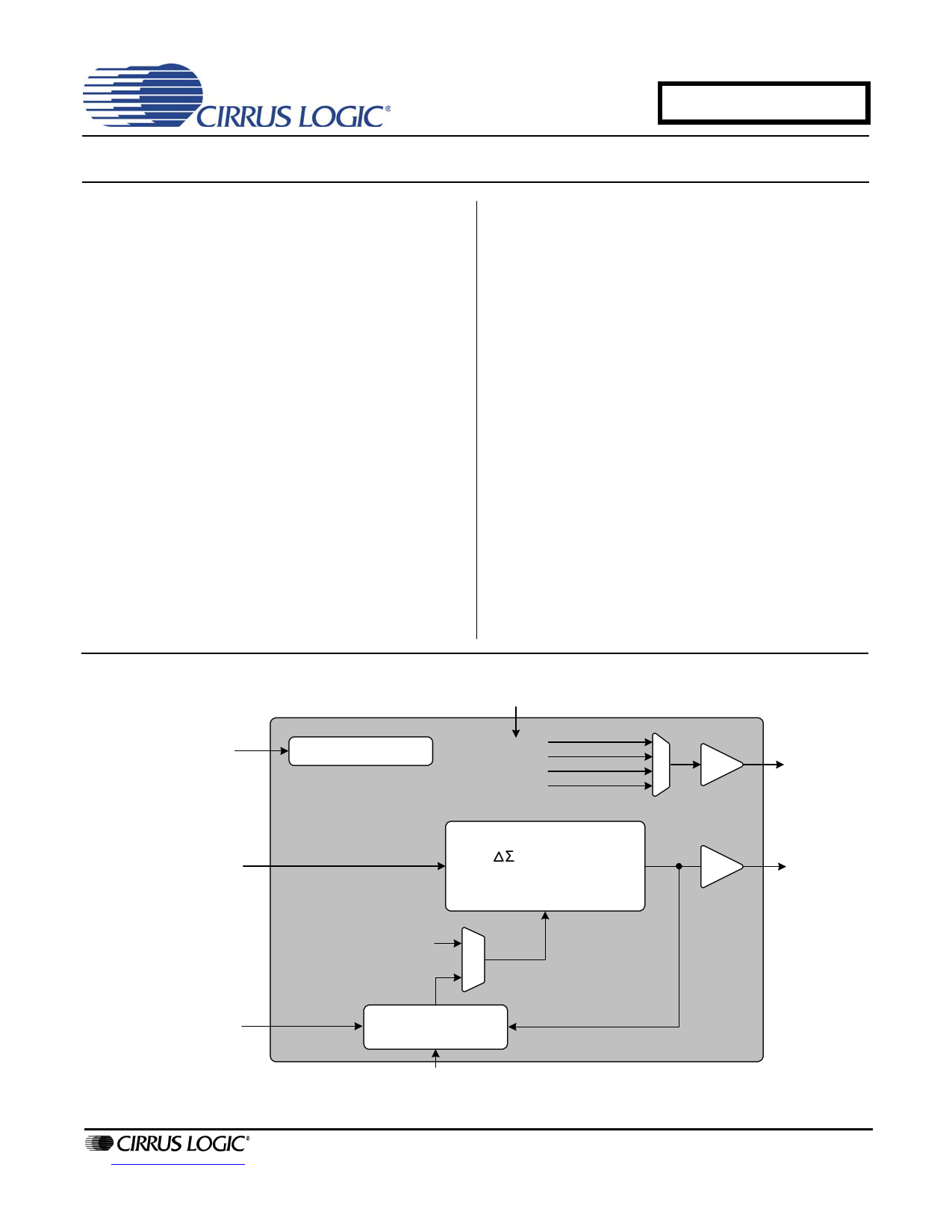

Hardware Control

Hardware Configuration

3.3 V

Timing Reference

Frequency Reference

PLL Output

Lock Indicator

Auxiliary

Output

8 MHz to 75 MHz

Low-Jitter Timing Reference

50 Hz to 30 MHz

Frequency Reference

http://www.cirrus.com

Fractional-N

Frequency Synthesizer

Output to Input

Clock Ratio

N

Digital PLL & Fractional

N Logic

Output to Input

Clock Ratio

Copyright Cirrus Logic, Inc. 2009

(All Rights Reserved)

6 to 75 MHz

PLL Output

AUG '09

DS758F1

1 page

2. TYPICAL CONNECTION DIAGRAM

CS2000-OTP

System Microcontroller

Frequency Reference

0.1 µF

1 µF

+3.3 V

VD

M2

M1

M0

CS2000-OTP

CLK_IN

CLK_OUT

1 XTI/REF_CLK

or

2 XTO

AUX_OUT

GND

To circuitry which requires

a low-jitter clock

To other circuitry or

Microcontroller

Low-Jitter

Timing Reference

1

N.C. x

Crystal

40 pF 40 pF

or

2

REF_CLK

XTO

XTI

XTO

DS758F1

Figure 1. Typical Connection Diagram

5

5 Page

5. APPLICATIONS

CS2000-OTP

5.1 One Time Programmability

The one time programmable (OTP) circuitry in the CS2000-OTP allows for pre-configuration of the device

prior to use in a system. There are two types of parameters that are used for device pre-configuration: modal

and global. The modal parameters are features which, when grouped together, create a modal configuration

set (see Figure 17 on page 22). Up to four modal configuration sets can be permanently stored and then

dynamically selected using the M[1:0] mode select pins (see Table 1). The global parameters are the re-

maining configuration settings which do not change with the mode select pins. The modal and global pa-

rameters can be pre-set at the factory or user programmed using the customer development kit, CDK2000;

Please see “Programming Information” on page 27 for more details.

Parameter Type

Modal

Global

M[1:0] pins = 00

Configuration Set 0

Ratio 0

M[1:0] pins = 01 M[1:0] pins = 10

Configuration Set 1

Ratio 1

Configuration Set 2

Ratio 2

Configuration settings set once for all modes.

M[1:0] pins = 11

Configuration Set 3

Ratio 3

Table 1. Modal and Global Configuration

5.2 Timing Reference Clock Input

The low jitter timing reference clock (RefClk) can be provided by either an external reference clock or an

external crystal in conjunction with the internal oscillator. In order to maintain a stable and low-jitter PLL out-

put the timing reference clock must also be stable and low-jitter; the quality of the timing reference clock

directly affects the performance of the PLL and hence the quality of the PLL output.

5.2.1

Internal Timing Reference Clock Divider

The Internal Timing Reference Clock (SysClk) is limited to a lower maximum frequency than that allowed

on the XTI/REF_CLK pin. The CS2000-OTP supports the wider external frequency range by offering an

internal divider for RefClk. The RefClkDiv[1:0] global parameter should be configured such that SysClk,

the divided RefClk, then falls within the valid range as indicated in “AC Electrical Characteristics” on

page 7.

XTI/REF_CLK

Timing Reference Clock

8

MHz

<

RefClk

<

50 MHz (XTI)

58 MHz (REF_CLK)

Timing Reference

Clock Divider

÷1

÷2

÷4

Internal Timing

Reference Clock

8 MHz < SysClk < 14 MHz

Fractional-N

Frequency

Synthesizer

PLL Output

RefClkDiv[1:0]

Figure 8. Internal Timing Reference Clock Divider

N

It should be noted that the maximum allowable input frequency of the XTI/REF_CLK pin is dependent

upon its configuration as either a crystal connection or external clock input. See the “AC Electrical Char-

acteristics” on page 7 for more details.

For the lowest possible output jitter, attention should be paid to the absolute frequency of the Timing Ref-

erence Clock relative to the PLL Output frequency (CLK_OUT). To minimize output jitter, the Timing Ref-

erence Clock frequency should be chosen such that fRefClk is at least +/-15 kHz from fCLK_OUT*N/32

where N is an integer. Figure 9 shows the effect of varying the RefClk frequency around fCLK_OUT*N/32.

It should be noted that there will be a jitter null at the zero point when N = 32 (not shown in Figure 9). An

DS758F1

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CS2000-OTP.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CS2000-OTP | Fractional-N Clock Synthesizer & Clock Multiplier | Cirrus Logic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |