|

|

PDF S29AS016J Data sheet ( Hoja de datos )

| Número de pieza | S29AS016J | |

| Descripción | Boot Sector Flash | |

| Fabricantes | Cypress Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de S29AS016J (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

S29AS016J

16 Mbit (2 M x 8-Bit/1 M x 16-Bit), 1.8 V

Boot Sector Flash

Distinctive Characteristics

Architectural Advantages

Single Power Supply Operation

– Full voltage range: 1.65 to 1.95 volt read and write operations for

battery-powered applications

Manufactured on 110 nm Process Technology

– Backward compatible with 0.32 µm Am29SL160C device

Secured Silicon Sector region

– 128-word/256-byte sector for permanent, secure identification

through an 8-word/16-byte random Electronic Serial Number,

accessible through a command sequence

– May be programmed and locked at the factory or by the customer

Flexible Sector Architecture

– Eight 8 Kbyte and thirty-one 64 Kbyte sectors (byte mode)

– Eight 4 Kword, and thirty-one 32 Kword sectors (word mode)

Sector Group Protection Features

– A hardware method of locking a sector to prevent any program or

erase operations within that sector

– Sectors can be locked in-system or via programming equipment

– Temporary Sector Group Unprotect feature allows code changes

in previously locked sectors

Unlock Bypass Program Command

– Reduces overall programming time when issuing multiple

program command sequences

Top or Bottom Boot Block Configurations Available

Compatibility with JEDEC standards

– Pinout and software compatible with single-power supply Flash

– Superior inadvertent write protection

Performance Characteristics

High Performance

– Access times as fast as 70 ns

– Industrial temperature range (-40°C to +85°C)

– Automotive In-Cabin temperature range (-40°C to +105°C)

– Word programming time as fast as 6 µs (typical)

Ultra Low Power Consumption (typical values at 5 MHz)

– 15 µA Automatic Sleep mode current

– 8 µA standby mode current

– 8 mA read current

– 20 mA program/erase current

Cycling Endurance: 1,000,000 cycles per sector typical

Data Retention: 20 years typical

Package Options

48-ball Fine-Pitch BGA, 8.15 mm x 6.15 mm

48-ball Fine-Pitch BGA, 6.0 mm x 4.0 mm

48-pin TSOP

Software Features

CFI (Common Flash Interface) Compliant

– Provides device-specific information to the system, allowing host

software to easily reconfigure for different Flash devices

Erase Suspend/Erase Resume

– Suspends an erase operation to read data from, or program data

to, a sector that is not being erased, then resumes the erase

operation

Data# Polling and Toggle Bits

– Provides a software method of detecting program or erase

operation completion

Hardware Features

Ready/Busy# Pin (RY/BY#)

– Provides a hardware method of detecting program or erase cycle

completion

Hardware Reset Pin (RESET#)

– Hardware method to reset the device to reading array data

WP# input pin

– Write protect (WP#) function allows protection of two outermost

boot sectors (boot sector models only), regardless of sector group

protect status

Cypress Semiconductor Corporation • 198 Champion Court

Document Number: 002-01122 Rev.*K

• San Jose, CA 95134-1709 • 408-943-2600

Revised December 09, 2015

1 page

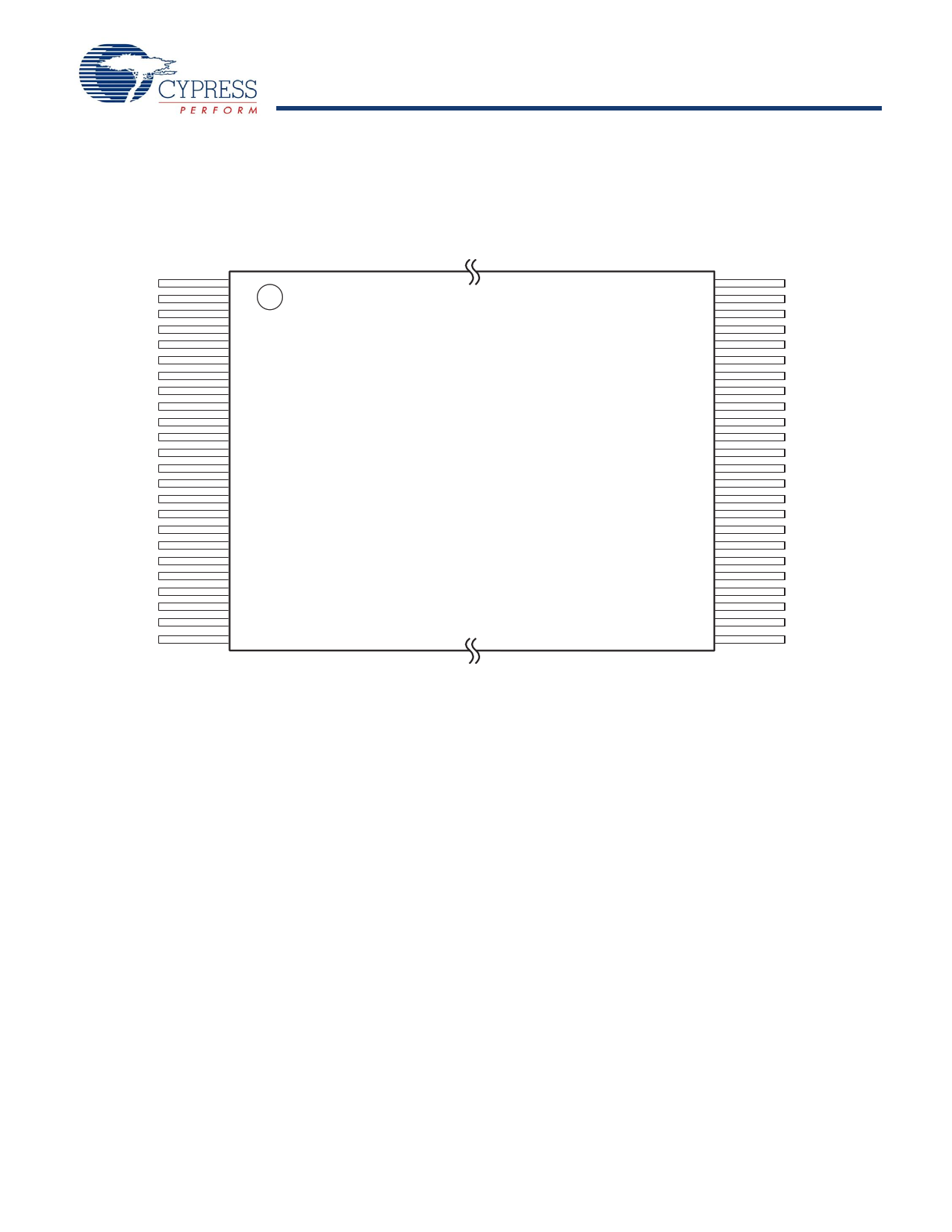

3. Connection Diagrams

3.1 Standard TSOP

A15

A14

A13

A12

A11

A10

A9

A8

A19

NC

WE#

RESET#

NC

WP#

RY/BY#

A18

A17

A7

A6

A5

A4

A3

A2

A1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Standard TSOP

S29AS016J

48 A16

47 BYTE#

46 VSS

45 DQ15/A-1

44 DQ7

43 DQ14

42 DQ6

41 DQ13

40 DQ5

39 DQ12

38 DQ4

37 VCC

36 DQ11

35 DQ3

34 DQ10

33 DQ2

32 DQ9

31 DQ1

30 DQ8

29 DQ0

28 OE#

27 VSS

26 CE#

25 A0

Document Number: 002-01122 Rev.*K

Page 5 of 55

5 Page

S29AS016J

7.6 Automatic Sleep Mode

The automatic sleep mode minimizes Flash device energy consumption. The device automatically enables this mode when

addresses remain stable for tACC + 30 ns. The automatic sleep mode is independent of the CE#, WE#, and OE# control signals.

Standard address access timings provide new data when addresses are changed. While in sleep mode, output data is latched and

always available to the system. ICC5 in the DC Characteristics on page 36 represents the automatic sleep mode current

specification.

7.7 RESET#: Hardware Reset Pin

The RESET# pin provides a hardware method of resetting the device to reading array data. When the system drives the RESET#

pin to VIL for at least a period of tRP, the device immediately terminates any operation in progress, tristates all data output pins, and

ignores all read/write attempts for the duration of the RESET# pulse. The device also resets the internal state machine to reading

array data. The operation that was interrupted should be reinitiated once the device is ready to accept another command sequence,

to ensure data integrity.

Current is reduced for the duration of the RESET# pulse. When RESET# is held at VSS±0.2 V, the device draws CMOS standby

current (ICC4). If RESET# is held at VIL but not within VSS±0.2 V, the standby current will be greater.

The RESET# pin may be tied to the system reset circuitry. A system reset would thus also reset the Flash memory, enabling the

system to read the boot-up firmware from the Flash memory. Note that the CE# pin should only go to VIL after RESET# has gone to

VIH. Keeping CE# at VIL from power up through the first read could cause the first read to retrieve erroneous data.

If RESET# is asserted during a program or erase operation, the RY/BY# pin remains a 0 (busy) until the internal reset operation is

complete, which requires a time of tREADY (during Embedded Algorithms). The system can thus monitor RY/BY# to determine

whether the reset operation is complete. If RESET# is asserted when a program or erase operation is not executing (RY/BY# pin is

1), the reset operation is completed within a time of tREADY (not during Embedded Algorithms). The system can read data tRH after

the RESET# pin returns to VIH.

Refer to the tables in AC Characteristics on page 38 for RESET# parameters and to Figure 18.2 on page 40 for the timing diagram.

If VID (9.0 V – 11.0 V) is applied to the RESET# pin, the device will enter the Temporary Sector Group Unprotect mode. See

Temporary Sector Group Unprotect on page 18 for more details on this feature.

7.8 Output Disable Mode

When the OE# input is at VIH, output from the device is disabled. The output pins are placed in the high impedance state.

7.9 Autoselect Mode

The autoselect mode provides manufacturer and device identification, sector group protection verification, and Secured Silicon

Sector status through identifier codes output on DQ7–DQ0. This mode is primarily intended for programming equipment to

automatically match a device to be programmed with its corresponding programming algorithm. However, the autoselect codes can

also be accessed in-system through the command register.

When using programming equipment, the autoselect mode requires VID (9.0 V to 11.0 V) on address pin A9. Address pins A6, A3,

A2, A1, and A0 must be as shown in Table . In addition, when verifying sector group protection, the sector address must appear on

the appropriate highest order address bits (see Table on page 12 and Table on page 14). Table shows the remaining address bits

that are don’t care. When all necessary bits have been set as required, the programming equipment may then read the

corresponding identifier code on DQ7-DQ0.

To access the autoselect codes in-system, the host system can issue the autoselect command via the command register, as shown

in Table on page 28. This method does not require VID. See Command Definitions on page 23 for details on using the autoselect

mode.

Document Number: 002-01122 Rev.*K

Page 11 of 55

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet S29AS016J.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S29AS016J | Boot Sector Flash | Cypress Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |