|

|

PDF MPC8347E Data sheet ( Hoja de datos )

| Número de pieza | MPC8347E | |

| Descripción | PowerQUICC II integrated host processor | |

| Fabricantes | Freescale Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de MPC8347E (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Freescale Semiconductor

Technical Data

Document Number: MPC8347EEC

Rev. 11, 02/2009

MPC8347E PowerQUICC™ II Pro

Integrated Host Processor Hardware

Specifications

The MPC8347E PowerQUICC™ II Pro is a next generation

PowerQUICC II integrated host processor. The MPC8347E

contains a PowerPC™ processor core built on Power

Architecture™ technology with system logic for

networking, storage, and general-purpose embedded

applications. For functional characteristics of the processor,

refer to the MPC8349E PowerQUICC™ II Pro Integrated

Host Processor Family Reference Manual.

To locate published errata or updates for this document, refer

to the MPC8347E product summary page on our website

listed on the back cover of this document or, contact your

local Freescale sales office.

NOTE

The information in this document is accurate for

revision 1.1 silicon and earlier. For information on

revision 3.0 silicon and later versions (for orderable

part numbers ending in A or B), see the

MPC8347EA PowerQUICC™ II Pro Integrated

Host Processor Hardware Specifications.

See Section 23.1, “Part Numbers Fully Addressed

by This Document,” for silicon revision level

determination.

Contents

1. Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2. Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . 7

3. Power Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 10

4. Clock Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . 12

5. RESET Initialization . . . . . . . . . . . . . . . . . . . . . . . . . 13

6. DDR SDRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

7. DUART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

8. Ethernet: Three-Speed Ethernet, MII Management . 22

9. USB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

10. Local Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

11. JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

12. I2C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

13. PCI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

14. Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

15. GPIO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

16. IPIC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

17. SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

18. Package and Pin Listings . . . . . . . . . . . . . . . . . . . . . 55

19. Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

20. Thermal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

21. System Design Information . . . . . . . . . . . . . . . . . . . 91

22. Document Revision History . . . . . . . . . . . . . . . . . . . 95

23. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . 98

© Freescale Semiconductor, Inc., 2005–2009. All rights reserved.

1 page

Overview

– Enhanced host controller interface (EHCI) compatible

– Complies with USB Specification Rev. 2.0

— High-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operations

— Direct connection to a high-speed device without an external hub

— External PHY with serial and low-pin count (ULPI) interfaces

• Local bus controller (LBC)

— Multiplexed 32-bit address and data operating at up to 133 MHz

— Four chip selects support four external slaves

— Up to eight-beat burst transfers

— 32-, 16-, and 8-bit port sizes controlled by an on-chip memory controller

— Three protocol engines on a per chip select basis:

– General-purpose chip select machine (GPCM)

– Three user-programmable machines (UPMs)

– Dedicated single data rate SDRAM controller

— Parity support

— Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

• Programmable interrupt controller (PIC)

— Functional and programming compatibility with the MPC8260 interrupt controller

— Support for 8 external and 35 internal discrete interrupt sources

— Support for 1 external (optional) and 7 internal machine checkstop interrupt sources

— Programmable highest priority request

— Four groups of interrupts with programmable priority

— External and internal interrupts directed to host processor

— Redirects interrupts to external INTA pin in core disable mode.

— Unique vector number for each interrupt source

• Dual industry-standard I2C interfaces

— Two-wire interface

— Multiple master support

— Master or slave I2C mode support

— On-chip digital filtering rejects spikes on the bus

— System initialization data optionally loaded from I2C-1 EPROM by boot sequencer embedded

hardware

• DMA controller

— Four independent virtual channels

— Concurrent execution across multiple channels with programmable bandwidth control

— All channels accessible to local core and remote PCI masters

— Misaligned transfer capability

MPC8347E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 11

Freescale Semiconductor

5

5 Page

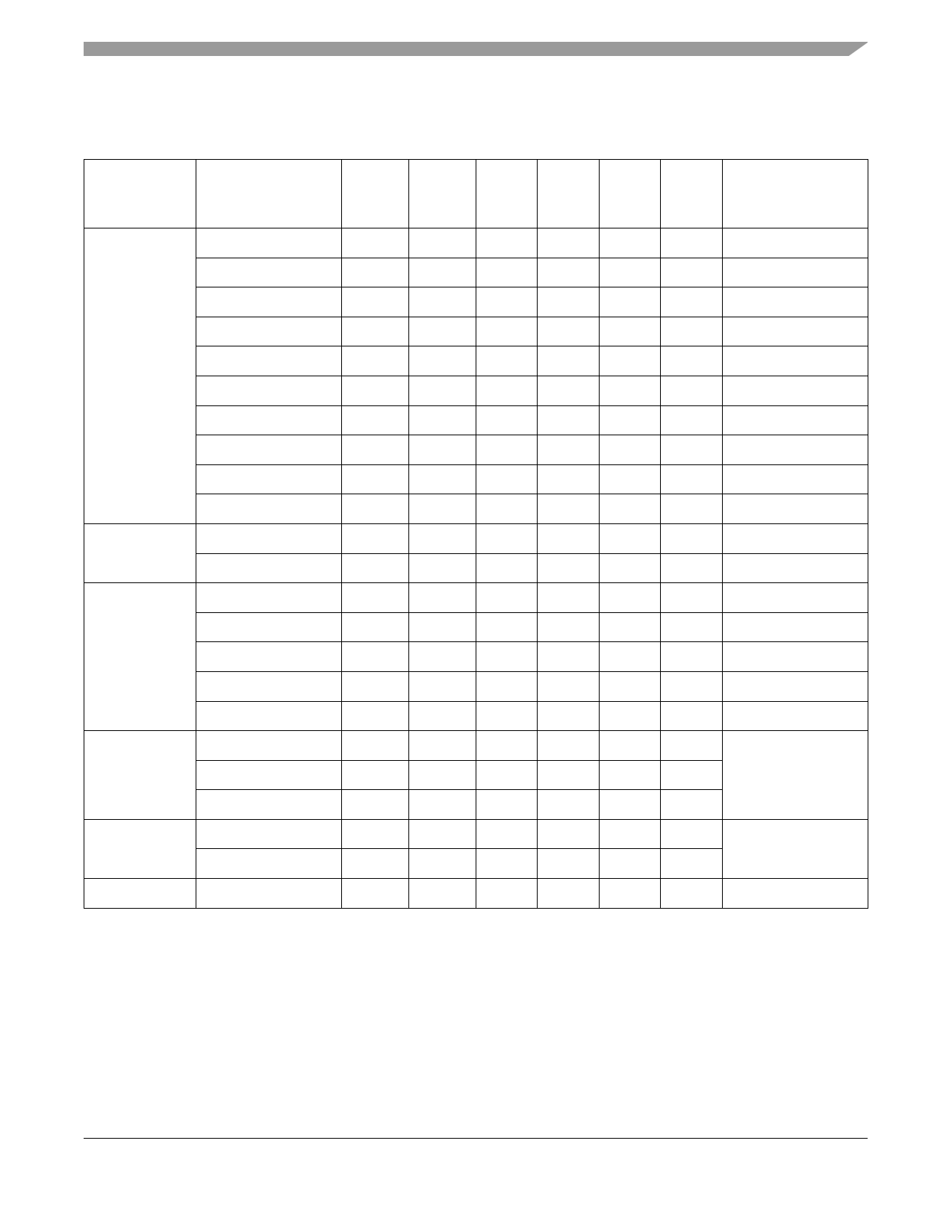

Power Characteristics

Table 5 shows the estimated typical I/O power dissipation for MPC8347E.

Table 5. MPC8347E Typical I/O Power Dissipation

Interface

Parameter

DDR I/O

65% utilization

2.5 V

Rs = 20 Ω

Rt = 50 Ω

2 pair of clocks

200 MHz, 32 bits

200 MHz, 64 bits

266 MHz, 32 bits

266 MHz, 64 bits

300 MHz,1 32 bits

300 MHz,1 64 bits

333 MHz,1 32 bits

333 MHz,1 64 bits

400 MHz,1 32 bits

400 MHz,1 64 bits

PCI I/O

load = 30 pF

33 MHz, 32 bits

66 MHz, 32 bits

Local bus I/O

load = 25 pF

167 MHz, 32 bits

133 MHz, 32 bits

83 MHz, 32 bits

66 MHz, 32 bits

50 MHz, 32 bits

TSEC I/O

load = 25 pF

MII

GMII or TBI

RGMII or RTBI

USB

12 MHz

480 MHz

Other I/O

1 TBGA package only.

DDR2

GVDD

(1.8 V)

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

DDR1

GVDD

(2.5 V)

OVDD LVDD LVDD

(3.3 V) (3.3 V) (2.5 V)

0.42 — — —

0.55 — — —

0.5 — — —

0.66 — — —

0.54 — — —

0.7 — — —

0.58 — — —

0.76 — — —

— ———

— ———

— 0.04 —

—

— 0.07 —

—

— 0.34 —

—

— 0.27 —

—

— 0.17 —

—

— 0.14 —

—

— 0.11 —

—

— — 0.01 —

— — 0.06 —

— — — 0.04

— 0.01 —

—

— 0.2 — —

— 0.01 —

—

Unit

Comments

W—

W—

W—

W—

W—

W—

W—

W—

—

—

W—

W—

W—

W—

W—

W—

W—

W Multiply by number of

interfaces used.

W

W

W Multiply by 2 if using

2 ports.

W

W—

MPC8347E PowerQUICC™ II Pro Integrated Host Processor Hardware Specifications, Rev. 11

Freescale Semiconductor

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet MPC8347E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MPC8347E | PowerQUICC II integrated host processor | Freescale Semiconductor |

| MPC8347EA | Integrated Host Processor Hardware Spec | Motorola Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |