|

|

PDF CB45000 Data sheet ( Hoja de datos )

| Número de pieza | CB45000 | |

| Descripción | HCMOS6 STANDARD CELLS | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CB45000 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

® CB45000 SERIES

HCMOS6 STANDARD CELLS

FEATURES

s 0.35 micron 5 layer metal HCMOS6 process,

retrograde well technology, low resistance

salicided active areas and polysilicide gates.

s 3.3 V optimized transistor with 5 V I/O inter-

face capability

s 2 - input NAND delay of 160 ps (typ) with

fanout = 2.

s Broad I/O functionality including Low Voltage

CMOS, Low Voltage TTL and LVDS. Driving

capability to ISA, EISA, PCI, MCA, and SCSI

interface levels

s High drive I/O; capability of sinking up to 24

mA with slew rate control, current spike sup-

pression and impedance matching.

s Generators to support Single Port RAM,

Dual Port RAM, and ROM with BIST options.

s DRAM integration in ASIC methodology

s Extensive embedded function library includ-

ing ST DSP and micro cores, third party

micros and Synopsys synthetic libraries.

s Fully independent power and ground config-

urations for inputs, core and outputs.

s I/O ring capability up to 1000 pads.

s Latchup trigger current > +/- 500 mA.

ESD protection > +/- 4000 volts typical value

s Oscillators for wide frequency spectrum.

s Broad range of 500+ SSI cells

s Design For Test features including IEEE

1149.1 JTAG Boundary Scan architecture.

s Cadence, Mentor and Synopsys based

design systems with interfaces from multiple

workstations.

s Broad ceramic and plastic package range.

ROM

DSP

DPRAM

ST20

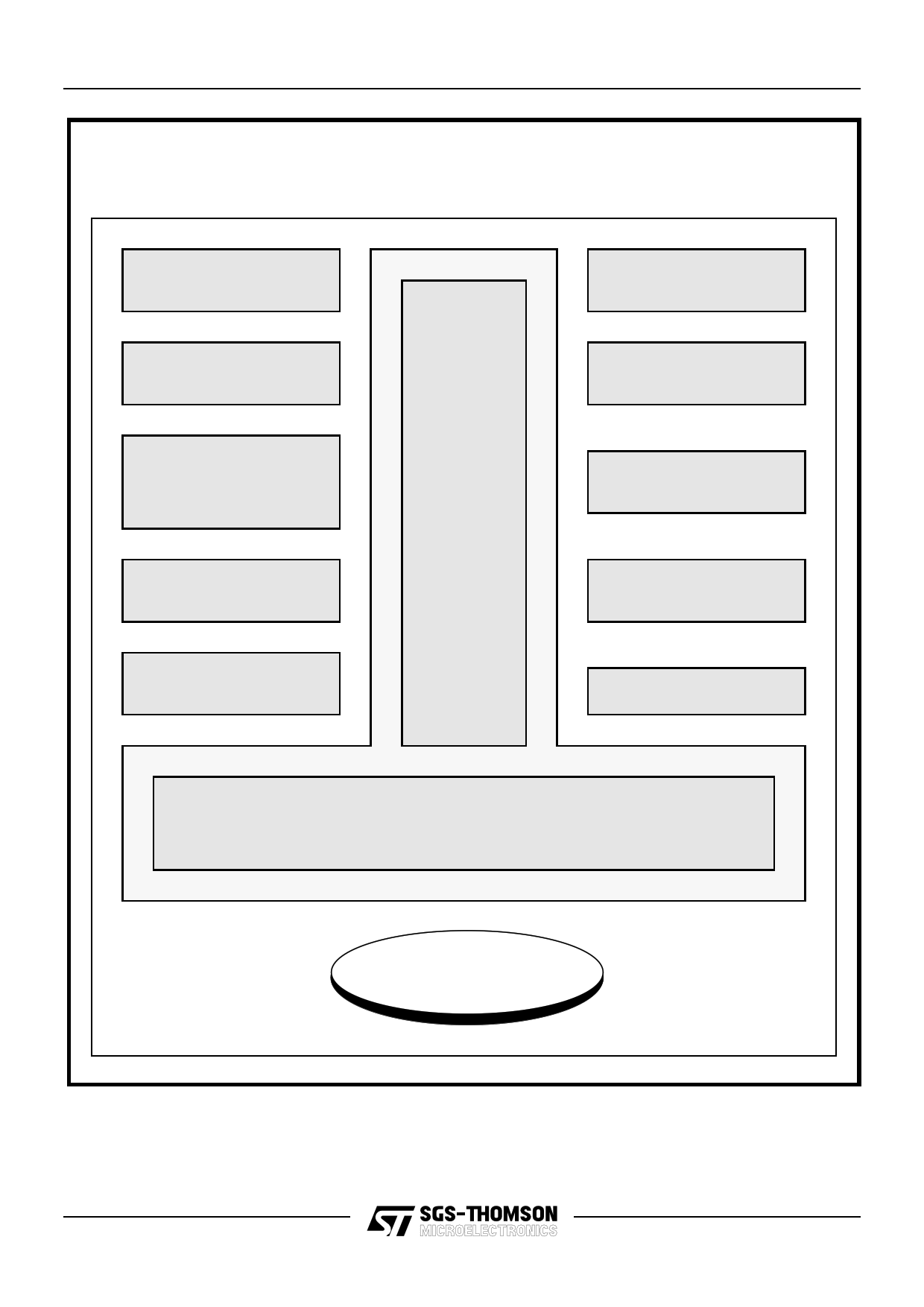

CB45000 Super-Integration

Cost Effective Product

s Architecture Partitioning

s Trouble free integration

s Application Specific

Your Product is Unique

s User specified cell integration

s Design Confidentiality

s IP fully re-usable

March 1998

1/16

1 page

CB45000 SERIES

Table 2 Voltage Multipliers

VDD

2.7

3.0

3.3

3.6

KV

1.20

1.11

1.00

0.94

I/O BUFFER LIBRARY

The CB45000 does not use traditional I/O cell

design; SGS-THOMSON was one of the pioneers

of the emerging “Flexible I/O” approach and the

CB45000 features variable bonding and a flexible

output transistor scheme based on a predefined

set of I/O transistor subcells.

These subcells can be quickly configured using

metallization layers to conform to a variety of I/O

specifications whilst maintaining optimal ESD

protection levels and latch-up prevention

characteristics.

The I/O circuitry also includes subcells of

specialized transistors that are used to form the

slew rate control sections of each I/O line.

Current spike suppression logic ensures that

conducting transistors are turned off before the

opposing set are turned on.

The bond pad itself is variable in terms of pitch

and size and even supports staggered bonding

methodologies. This is becoming far more

Figure 3

Flexible IO Buffer Technology

EDGE OF DIE

GUARDRING

Programmable pad locations allows

one IO cell library to be used for both

staggered and linear bonding.

EDGE OF DIE

GUARDRING

ESD CLAMP

STRUCTURES

ESD CLAMP

STRUCTURES

ESD CLAMP

STRUCTURES

OUTPUT

DRIVE

TRANSISTORS

OUTPUT

DRIVE

TRANSISTORS

OUTPUT

DRIVE

TRANSISTORS

DIODES

LOGIC CIRCUITS

TEST INTERFACE

SLEW CONTROL

DIODES

LOGIC CIRCUITS

TEST INTERFACE

SLEW CONTROL

DIE CORE

DIODES

LOGIC CIRCUITS

TEST INTERFACE

SLEW CONTROL

®

ESD CLAMP

STRUCTURES

ESD CLAMP

STRUCTURES

ESD CLAMP

STRUCTURES

OUTPUT

DRIVE

TRANSISTORS

OUTPUT

DRIVE

TRANSISTORS

OUTPUT

DRIVE

TRANSISTORS

DIODES

LOGIC CIRCUITS

TEST INTERFACE

SLEW CONTROL

DIODES

LOGIC CIRCUITS

TEST INTERFACE

SLEW CONTROL

DIE CORE

DIODES

LOGIC CIRCUITS

TEST INTERFACE

SLEW CONTROL

5/16

5 Page

Figure 8

SGS-THOMSON Layout Driven Design Flow

HARDWARE DESCRIPTION

LANGUAGE

VHDL / VERILOG

LOGIC SYNTHESIS

SCAN INSERTION

GATE LEVEL SIMULATION

VERILOG / MENTOR

TIMING ANALYSIS

FORMAL PROOF

ACCELERATION

HW / SW EMULATION

FAULT ANALYSIS

TSSI / IDDQ

CB45000 SERIES

FUNCTIONAL

SIMULATION

VHDL / VERILOG

SCHEMATIC CAPTURE

CADENCE

MENTOR

DELAY EVALUATION

RC BACK-ANNOTATION

POWER ESTIMATION

POWER ANALYSIS

CLOCK TREE SYNTHESIS

LAYOUT

SILICON

11/16

®

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet CB45000.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CB45000 | HCMOS6 STANDARD CELLS | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |