|

|

PDF AT80F51-16PC Data sheet ( Hoja de datos )

| Número de pieza | AT80F51-16PC | |

| Descripción | 8-Bit Microcontroller with 4K Bytes QuickFlash Memory | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT80F51-16PC (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

Features

• Compatible with MCS-51™ Products

• 4K Bytes of Factory Programmable QuickFlash™ Memory

• Fully Static Operation: 0 Hz to 20 MHz

• Three-Level Program Memory Lock

• 128 x 8-Bit Internal RAM

• 32 Programmable I/O Lines

• Two 16-Bit Timer/Counters

• Six Interrupt Sources

• Programmable Serial Channel

• Low Power Idle and Power Down Modes

Description

The AT80F51 is a low-power, high-performance CMOS 8-bit microcomputer with 4K

bytes of QuickFlash Memory. The device is manufactured using Atmel’s high density

nonvolatile memory technology and is compatible with the industry standard MCS-

51™ instruction set and pinout. The on-chip QuickFlash allows custom codes to be

quickly programmed in the factory. By combining a versatile 8-bit CPU with Quick-

Flash on a monolithic chip, the Atmel AT80F51 is a powerful microcomputer which

provides a highly flexible and cost effective solution to many embedded control appli-

cations.

(continued)

Pin Configurations

TQFP

INDEX

CORNER

P1.5

P1.6

P1.7

RST

(RXD) P3.0

NC

(TXD) P3.1

(INT0) P3.2

(INT1) P3.3

(T0) P3.4

(T1) P3.5

4

44

34

24

14

03

93

83

73

6

3

3

5

4

1 33

2 32

3 31

4 30

5 29

6 28

7 27

8 26

9 25

10 24

11 23

1

21

31

41

51

61

71

1

8

9

2

02

12

2

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

EA

NC

ALE

PSEN

P2.7 (A15)

P2.6 (A14)

P2.5 (A13)

PDIP

P1.0

P1.1

P1.2

P1.3

P1.4

P1.5

P1.6

P1.7

RST

(RXD) P3.0

(TXD) P3.1

(INT0) P3.2

(INT1) P3.3

(T0) P3.4

(T1) P3.5

(WR) P3.6

(RD) P3.7

X TA L 2

X TA L 1

GND

1 40

2 39

3 38

4 37

5 36

6 35

7 34

8 33

9 32

10 31

11 30

12 29

13 28

14 27

15 26

16 25

17 24

18 23

19 22

20 21

PLCC

VCC

P0.0 (AD0)

P0.1 (AD1)

P0.2 (AD2)

P0.3 (AD3)

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

EA

ALE

PSEN

P2.7 (A15)

P2.6 (A14)

P2.5 (A13)

P2.4 (A12)

P2.3 (A11)

P2.2 (A10)

P2.1 (A9)

P2.0 (A8)

INDEX

CORNER

(RXD)

(TXD)

(INT0)

(INT1)

(T0)

(T1)

P1.5

P1.6

P1.7

RST

P3.0

NC

P3.1

P3.2

P3.3

P3.4

P3.5

6 4 2 44 42 40

7 5 3 1 43 4139

8 38

9 37

10 36

11 35

12 34

13 33

14 32

15 31

16 30

11781 92 02 12 22 32 42 52 62 72289

P0.4 (AD4)

P0.5 (AD5)

P0.6 (AD6)

P0.7 (AD7)

EA

NC

ALE

PSEN

P2.7 (A15)

P2.6 (A14)

P2.5 (A13)

8-Bit

Microcontroller

with 4K Bytes

QuickFlash™

Memory

AT80F51

0979A-A–12/97

3-3

1 page

AT80F51

nated. The only exit from power down is a hardware reset.

Reset redefines the SFRs but does not change the on-chip

RAM. The reset should not be activated before VCC is

restored to its normal operating level and must be held

active long enough to allow the oscillator to restart and sta-

bilize.

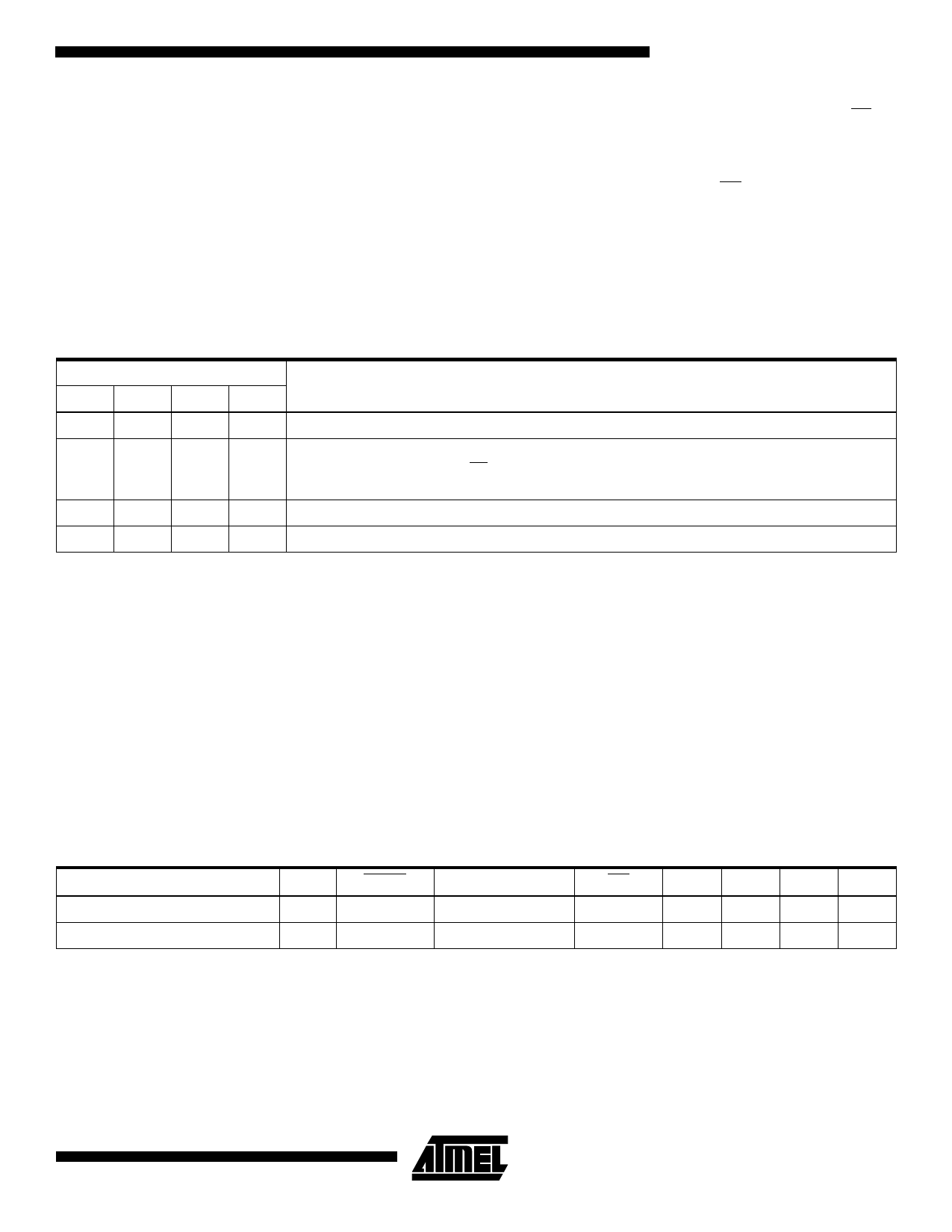

Program Memory Lock Bits

On the chip are three lock bits which can be left unpro-

grammed (U) or can be programmed (P) to obtain the addi-

tional features listed in the table below:

Lock Bit Protection Modes

When lock bit 1 is programmed, the logic level at the EA pin

is sampled and latched during reset. If the device is pow-

ered up without a reset, the latch initializes to a random

value, and holds that value until reset is activated. It is nec-

essary that the latched value of EA be in agreement with

the current logic level at that pin in order for the device to

function properly.

Program Lock Bits

LB1 LB2 LB3

1 UUU

2 PUU

3 PPU

4PPP

Protection Type

No program lock features.

MOVC instructions executed from external program memory are disabled from fetching code

bytes from internal memory, EA is sampled and latched on reset, and further programming of the

QuickFlash is disabled.

Same as mode 2, also verify is disabled.

Same as mode 3, also external execution is disabled.

Programming/Verifying the QuickFlash

The AT80F51 can only be programmed by Atmel. Cus-

tomer codes should be submitted in duplicate on a floppy

disk or uploaded to Atmel’s bulletin board or Web site. The

code should be in the Intel Hex format. The desired states

of the Lock Bits should be specified. Once programmed,

the code memory and Lock Bits cannot be erased or repro-

grammed.

Please consult the factory or Atmel’s representatives for

details on submitting custom codes.

Program Verify: If lock bits LB1 and LB2 have not been

programmed, the programmed code data can be read back

via the address and data lines for verification. The lock bits

QuickFlash Verification Modes

cannot be verified directly. Verification of the lock bits is

achieved by observing that their features are enabled.

Reading the Signature Bytes: The signature bytes are

read by the same procedure as a normal verification of

locations 030H, 031H, and 032H, except that P3.6 and

P3.7 must be pulled to a logic low. The values returned are

as follows.

(030H) = 1EH indicates manufactured by Atmel

(031H) = 80H indicates QuickFlash

(032H) = 01H indicates AT80F51

Mode

Read Code Data

Read Signature Byte

RST

H

H

PSEN

L

L

ALE

H

H

EA P2.6 P2.7 P3.6 P3.7

H L LHH

H LLLL

3-7

5 Page

AT80F51

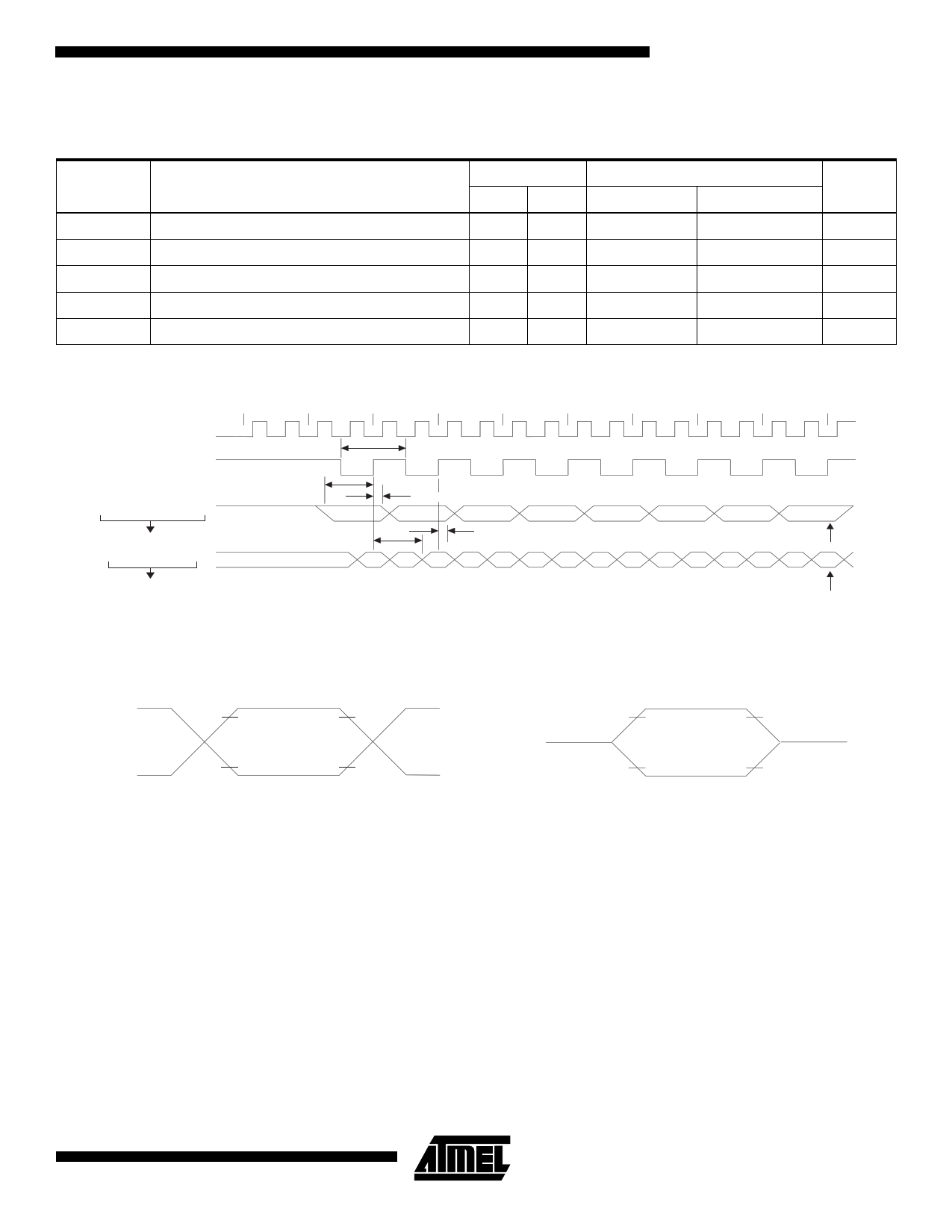

Serial Port Timing: Shift Register Mode Test Conditions

(VCC = 5.0 V ± 20%; Load Capacitance = 80 pF)

Symbol

Parameter

12 MHz Osc

Variable Oscillator

Min Max

Min

Max

tXLXL

tQVXH

tXHQX

tXHDX

tXHDV

Serial Port Clock Cycle Time

Output Data Setup to Clock Rising Edge

Output Data Hold After Clock Rising Edge

Input Data Hold After Clock Rising Edge

Clock Rising Edge to Input Data Valid

1.0 12tCLCL

700 10tCLCL-133

50 2tCLCL-117

00

700

10tCLCL-133

Units

µs

ns

ns

ns

ns

Shift Register Mode Timing Waveforms

INSTRUCTION

ALE

CLOCK

WRITE TO SBUF

OUTPUT DATA

CLEAR RI

INPUT DATA

012345678

tQVXH

0

tXHDV

VALID

tXLXL

tXHQX

1

VALID

2

tXHDX

VALID

3

VALID

4

VALID

5

VALID

67

SET TI

VALID

VALID

SET RI

AC Testing Input/Output Waveforms(1) Float Waveforms(1)

VCC - 0.5V

0.45V

0.2 VCC + 0.9V

TEST POINTS

0.2 VCC - 0.1V

VLOAD

V

+

LOAD

0.1V

V LOAD - 0.1V

Timing Reference

Points

V OL - 0.1V

V OL + 0.1V

Note:

1. AC Inputs during testing are driven at VCC - 0.5V for Note:

a logic 1 and 0.45V for a logic 0. Timing measure-

ments are made at VIH min. for a logic 1 and VIL

max. for a logic 0.

1. For timing purposes, a port pin is no longer floating

when a 100 mV change from load voltage occurs. A

port pin begins to float when 100 mV change from

the loaded VOH/VOL level occurs.

3-13

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet AT80F51-16PC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT80F51-16PC | 8-Bit Microcontroller with 4K Bytes QuickFlash Memory | ATMEL Corporation |

| AT80F51-16PI | 8-Bit Microcontroller with 4K Bytes QuickFlash Memory | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |