|

|

PDF AT45DB321B-CC Data sheet ( Hoja de datos )

| Número de pieza | AT45DB321B-CC | |

| Descripción | 32-megabit 2.7-volt Only DataFlash | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT45DB321B-CC (archivo pdf) en la parte inferior de esta página. Total 32 Páginas | ||

|

No Preview Available !

Features

• Single 2.7V - 3.6V Supply

• Serial Peripheral Interface (SPI) Compatible

• 20 MHz Max Clock Frequency

• Page Program Operation

– Single Cycle Reprogram (Erase and Program)

– 8192 Pages (528 Bytes/Page) Main Memory

• Supports Page and Block Erase Operations

• Two 528-byte SRAM Data Buffers – Allows Receiving of Data

while Reprogramming of Nonvolatile Memory

• Continuous Read Capability through Entire Array

– Ideal for Code Shadowing Applications

• Low Power Dissipation

– 4 mA Active Read Current Typical

– 2 µA CMOS Standby Current Typical

• Hardware Data Protection Feature

• 100% Compatible to AT45DB321

• 5.0V-tolerant Inputs: SI, SCK, CS, RESET and WP Pins

• Commercial and Industrial Temperature Ranges

Description

The AT45DB321B is a 2.7-volt only, serial interface Flash memory ideally suited for

a wide variety of digital voice-, image-, program code- and data-storage applications.

Its 34,603,008 bits of memory are organized as 8192 pages of 528 bytes each. In

addition to the main memor y, the AT45DB321B also contains two SRAM

data buffers of 528 bytes each. The buffers allow receiving of data while a page in the

main memory is being reprogrammed, as well as reading or writing a continuous data

Pin Configurations

Pin Name Function

CS Chip Select

SCK

Serial Clock

SI Serial Input

SO Serial Output

WP Hardware Page Write Protect Pin

RESET

Chip Reset

RDY/BUSY Ready/Busy

CBGA Top View through Package

12345

A

NC NC NC NC

B

NC NC NC NC NC

C

NC NC NC NC NC

D

NC SCK GND VCC NC

E

NC CS RDY/BSY WP NC

F

NC SO SI RESET NC

G

NC NC NC NC NC

H

NC NC NC NC NC

J

NC NC NC NC NC

32-megabit

2.7-volt Only

DataFlash®

AT45DB321B

SOIC

GND

NC

NC

CS

SCK

SI

SO

NC

NC

NC

NC

NC

NC

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

28 VCC

27 NC

26 NC

25 WP

24 RESET

23 RDY/BUSY

22 NC

21 NC

20 NC

19 NC

18 NC

17 NC

16 NC

15 NC

TSOP Top View

Type 1

RDY/BUSY

RESET

WP

NC

NC

NC

VCC

GND

NC

NC

NC

NC

CS

SCK

SI

SO

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

32 NC

31 NC

30 NC

29 NC

28 NC

27 NC

26 NC

25 NC

24 NC

23 NC

22 NC

21 NC

20 NC

19 NC

18 NC

17 NC

Note:

DataFlash Card(1)

7654321

1. See AT45DCB004 Datasheet

Rev. 2223D–DFLASH–10/02

1

1 page

Program and Erase

Commands

2223D–DFLASH–10/02

AT45DB321B

loaded into the device. After the last bit of the opcode is shifted in, the eight bits of the

status register, starting with the MSB (bit 7), will be shifted out on the SO pin during the

next eight clock cycles. The five most significant bits of the status register will contain

device information, while the remaining three least-significant bits are reserved for future

use and will have undefined values. After bit 0 of the status register has been shifted

out, the sequence will repeat itself (as long as CS remains low and SCK is being tog-

gled) starting again with bit 7. The data in the status register is constantly updated, so

each repeating sequence will output new data.

Status Register Format

Bit 7

RDY/BUSY

Bit 6

COMP

Bit 5

1

Bit 4

1

Bit 3

0

Bit 2

1

Bit 1

X

Bit 0

X

Ready/Busy status is indicated using bit 7 of the status register. If bit 7 is a 1, then the

device is not busy and is ready to accept the next command. If bit 7 is a 0, then the

device is in a busy state. The user can continuously poll bit 7 of the status register by

stopping SCK at a low level once bit 7 has been output. The status of bit 7 will continue

to be output on the SO pin, and once the device is no longer busy, the state of SO will

change from 0 to 1. There are eight operations which can cause the device to be in a

busy state: Main Memory Page to Buffer Transfer, Main Memory Page to Buffer Com-

pare, Buffer to Main Memory Page Program with Built-in Erase, Buffer to Main Memory

Page Program without Built-in Erase, Page Erase, Block Erase, Main Memory Page

Program, and Auto Page Rewrite.

The result of the most recent Main Memory Page to Buffer Compare operation is indi-

cated using bit 6 of the status register. If bit 6 is a 0, then the data in the main memory

page matches the data in the buffer. If bit 6 is a 1, then at least one bit of the data in the

main memory page does not match the data in the buffer.

The device density is indicated using bits 5, 4, 3 and 2 of the status register. For the

AT45DB321B, the four bits are 1, 1, 0 and 1. The decimal value of these four binary bits

does not equate to the device density; the four bits represent a combinational code

relating to differing densities of Serial DataFlash devices, allowing a total of sixteen dif-

ferent density configurations.

BUFFER WRITE: Data can be shifted in from the SI pin into either buffer 1 or buffer 2.

To load data into either buffer, an 8-bit opcode, 84H for buffer 1 or 87H for buffer 2, must

be followed by 14 don’t care bits and ten address bits (BFA9 - BFA0). The ten address

bits specify the first byte in the buffer to be written. The data is entered following the

address bits. If the end of the data buffer is reached, the device will wrap around back to

the beginning of the buffer. Data will continue to be loaded into the buffer until a low-to-

high transition is detected on the CS pin.

BUFFER TO MAIN MEMORY PAGE PROGRAM WITH BUILT-IN ERASE: Data written

into either buffer 1 or buffer 2 can be programmed into the main memory. To start the

operation, an 8-bit opcode, 83H for buffer 1 or 86H for buffer 2, must be followed by one

reserved bit, 13 address bits (PA12 - PA0) that specify the page in the main memory to

be written, and ten additional don’t care bits. When a low-to-high transition occurs on the

CS pin, the part will first erase the selected page in main memory to all 1s and then pro-

gram the data stored in the buffer into the specified page in the main memory. Both the

erase and the programming of the page are internally self-timed and should take place

in a maximum time of tEP. During this time, the status register will indicate that the part is

busy.

5

5 Page

AT45DB321B

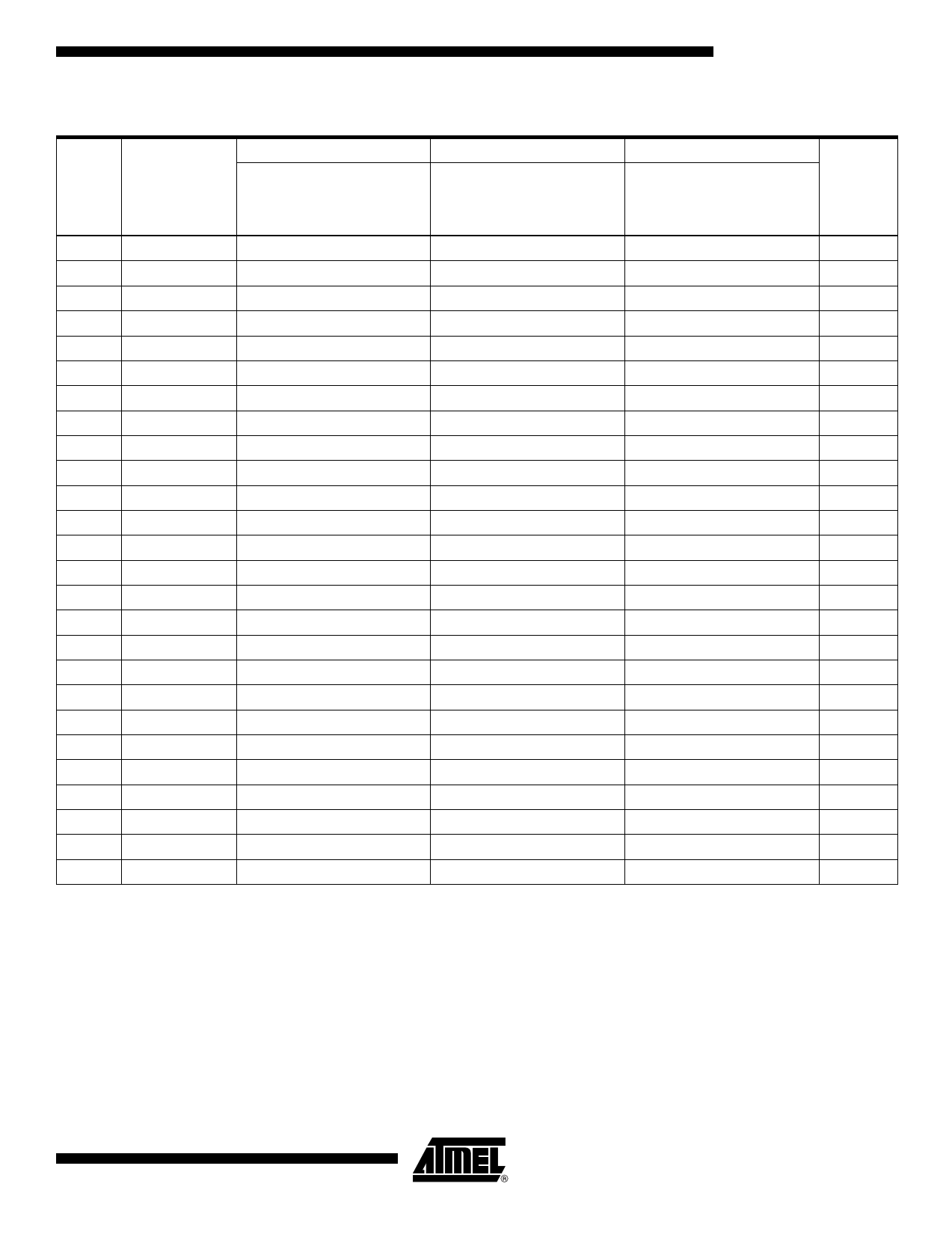

Table 4. Detailed Bit-level Addressing Sequence

Address Byte

Address Byte

Address Byte

Opcode

Opcode

Additional

Don’t Care

Bytes

Required

50H 0 1 0 1 0 0 0 0 r P P P P P P P P P P x x x x x x x x x x x x x

N/A

52H 0 1 0 1 0 0 1 0 r P P P P P P P P P P P P P B B B B B B B B B B 4 Bytes

53H 0 1 0 1 0 0 1 1 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

54H 0 1 0 1 0 1 0 0 x x x x x x x x x x x x x x B B B B B B B B B B

1 Byte

55H 0 1 0 1 0 1 0 1 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

56H 0 1 0 1 0 1 1 0 x x x x x x x x x x x x x x B B B B B B B B B B

1 Byte

57H 0 1 0 1 0 1 1 1

N/A

N/A

N/A N/A

58H 0 1 0 1 1 0 0 0 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

59H 0 1 0 1 1 0 0 1 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

60H 0 1 1 0 0 0 0 0 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

61H 0 1 1 0 0 0 0 1 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

68H 0 1 1 0 1 0 0 0 r P P P P P P P P P P P P P B B B B B B B B B B 4 Bytes

81H 1 0 0 0 0 0 0 1 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

82H 1 0 0 0 0 0 1 0 r P P P P P P P P P P P P P B B B B B B B B B B

N/A

83H 1 0 0 0 0 0 1 1 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

84H 1 0 0 0 0 1 0 0 x x x x x x x x x x x x x x B B B B B B B B B B

N/A

85H 1 0 0 0 0 1 0 1 r P P P P P P P P P P P P P B B B B B B B B B B

N/A

86H 1 0 0 0 0 1 1 0 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

87H 1 0 0 0 0 1 1 1 x x x x x x x x x x x x x x B B B B B B B B B B

N/A

88H 1 0 0 0 1 0 0 0 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

89H 1 0 0 0 1 0 0 1 r P P P P P P P P P P P P P x x x x x x x x x x

N/A

D2H 1 1 0 1 0 0 1 0 r P P P P P P P P P P P P P B B B B B B B B B B 4 Bytes

D4H 1 1 0 1 0 1 0 0 x x x x x x x x x x x x x x B B B B B B B B B B

1 Byte

D6H 1 1 0 1 0 1 1 0 x x x x x x x x x x x x x x B B B B B B B B B B

1 Byte

D7H 1 1 0 1 0 1 1 1

N/A

N/A

N/A N/A

E8H 1 1 1 0 1 0 0 0 r P P P P P P P P P P P P P B B B B B B B B B B

Note:

r = Reserved Bit

P = Page Address Bit

B = Byte/Buffer Address Bit

x = Don’t Care

4 Bytes

2223D–DFLASH–10/02

11

11 Page | ||

| Páginas | Total 32 Páginas | |

| PDF Descargar | [ Datasheet AT45DB321B-CC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT45DB321B-CC | 32-megabit 2.7-volt Only DataFlash | ATMEL Corporation |

| AT45DB321B-CI | 32-megabit 2.7-volt Only DataFlash | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |