|

|

PDF ADV7152 Data sheet ( Hoja de datos )

| Número de pieza | ADV7152 | |

| Descripción | CMOS 220 MHz True-Color Graphics Triple 10-Bit Video RAM-DAC | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADV7152 (archivo pdf) en la parte inferior de esta página. Total 32 Páginas | ||

|

No Preview Available !

a

CMOS 220 MHz True-Color Graphics

Triple 10-Bit Video RAM-DAC

ADV7152

FEATURES

APPLICATIONS

220 MHz, 24-Bit (30-Bit Gamma Corrected) True Color

High Resolution, True Color Graphics

Triple 10-Bit “Gamma Correcting” D/A Converters

Professional Color Prepress Imaging

Triple 256 ؋ 10 (256 ؋ 30) Color Palette RAM

On-Chip Clock Control Circuit

GENERAL DESCRIPTION

Palette Priority Select Registers

The ADV7152 (ADV®) is a complete analog output, Video

RS-343A/RS-170 Compatible Analog Outputs

RAM-DAC on a single CMOS monolithic chip. The part is spe-

TTL Compatible Digital Inputs

cifically designed for use in high performance, color graphics

Standard MPU l/O Interface

workstations. The ADV7152 integrates a number of graphic

10-Bit Parallel Structure

functions onto one device allowing 24-bit direct True-Color op-

8+2 Byte Structure

eration at the maximum screen update rate of 220 MHz. The

Programmable Pixel Port: 24-Bit and 8-Bit (Pseudo)

ADV7152 implements 30-bit True Color in 24-bit frame buffer

Pixel Data Serializer

designs. The part also supports other modes, including 15-bit

Multiplexed Pixel Input Ports; 1:1, 2:1

True Color and 8-bit Pseudo or Indexed Color. Either the Red,

+5 V CMOS Monolithic Construction

Green or Blue input pixel ports can be used for Pseudo Color.

100-Lead Plastic Quad Flatpack (QFP)

Thermally Enhanced to Achieve JC < 1.0؇C/W

The device consists of three, high speed, 10-bit, video D/A con-

verters (RGB), three 256 ϫ 10 (one 256 ϫ 30) color look-up

MODES OF OPERATION

tables, palette priority selects, a pixel input data multiplexer/

24-Bit True Color (30-Bit Gamma Corrected)

serializer and a clock generator/divider circuit. The ADV7152

@ 220 MHz

implements 1:1 and 2:1 pixel data multiplexing. The onboard

@ 170 MHz

palette priority select inputs enable multiple palette devices to

@ 135 MHz

be connected together for use in multipalette and window

@ 110 MHz

(Continued on page 10)

@ 85 MHz

8-Bit Pseudo Color

ADV is a registered trademark of Analog Devices, Inc.

15-Bit True Color

FUNCTIONAL BLOCK DIAGRAM

VAA

256-COLOR/GAMMA

PALETTE RAM

ADV7152

RED (R0–R7),

GREEN (G0–G7),

BLUE (B0–B7)

COLOR DATA

A

B

PALETTE

SELECTS

(PS0, PS1)

LOADIN

LOADOUT

PRGCKOUT

SCKIN

SCKOUT

SYNC

BLANK

CLOCK

CLOCK

24

P 48

I

X

24 E

MUX

2:1

L

P

O

4

R

T

4

MUX

2:1

8

8

8

2

CLOCK CONTROL

CLOCK DIVIDE

&

SYNCHRONIZATION

CIRCUIT

÷32, ÷16, ÷8, ÷4, ÷2

ADDRESS

REGISTER

ADDR

(A0-–A15)

MODE

REGISTER

(MR1)

ECL TO CMOS

RED

256 x 10

GREEN

256 x 10

10

10

BLUE

256 x 10

10

10-BIT

RED DAC

10-BIT

GREEN DAC

10-BIT

BLUE DAC

CONTROL REGISTERS

PIXEL MASK

REGISTER

TEST

REGISTERS

COMMAND

REGISTERS

(CR1-CR3)

ID

REGISTER

REVISION

REGISTER

SYNC

OUTPUT

DATA TO

PALETTES

VOLTAGE

REFERENCE

CIRCUIT

30 COLOR REGISTERS

RED

GREEN

BLUE

REGISTER REGISTER REGISTER

MPU PORT

10 (8+2)

IOR

IOR

IOG

IOG

IOB

IOB

IPLL

SYNCOUT

VREF

RSET

COMP

REV. B

CE R/W C0 C1

D9 – D0

GND

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700

Fax: 617/326-8703

1 page

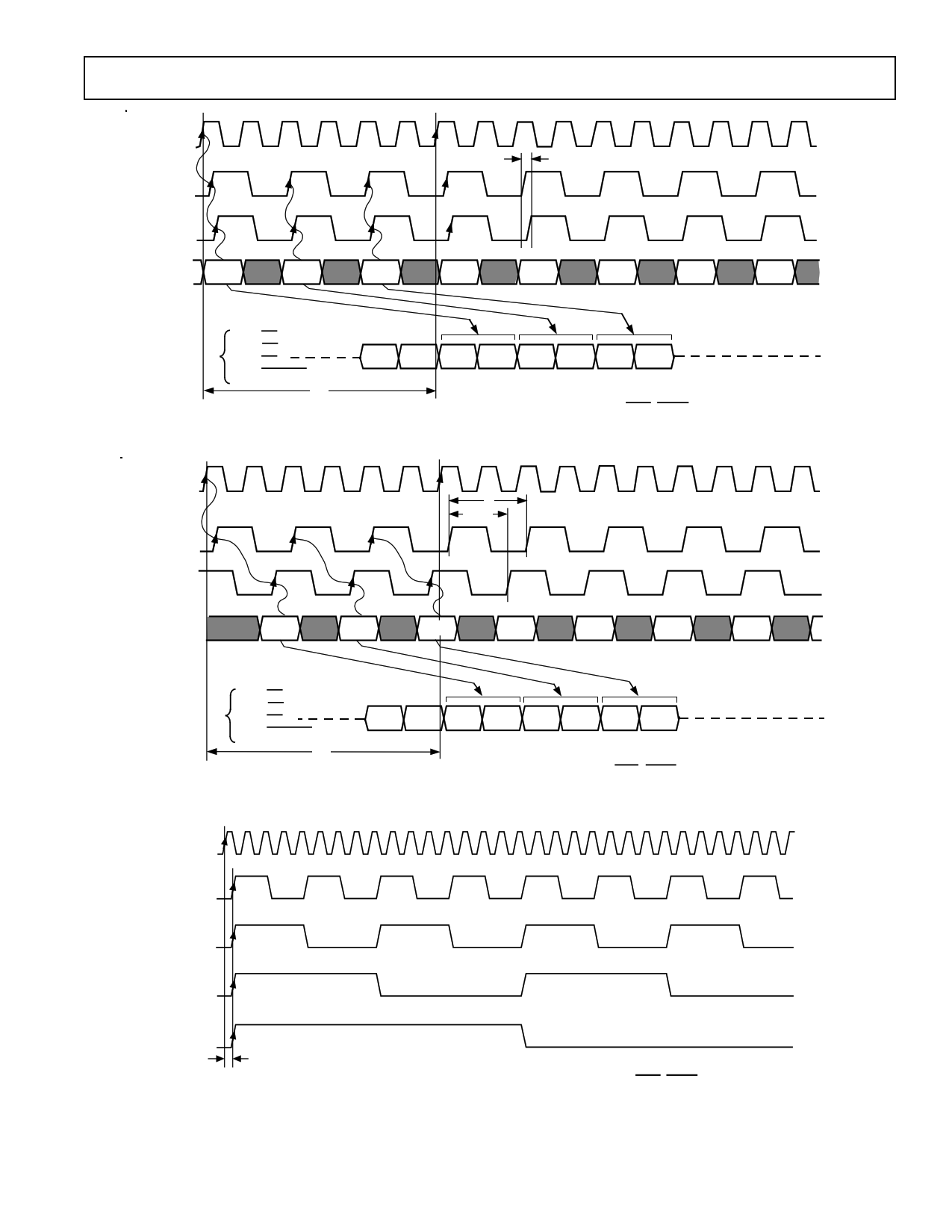

ADV7152

CLOCK

LOADOUT

t10

LOADIN

PIXEL INPUT

DATA*

ANALOG

OUTPUT

DATA

AN BN

AN+1BN+1

AN+2BN+2

DIGITAL INPUT TO ANALOG OUTPUT PIPELINE

IOR, IOR

IOG, IOG

IOB, IOB

IPLL, SYNCOUT

AN-1

BN-1

AN

BN

AN+1

BN+1

AN+2

BN+2

tPD

*INCLUDES PIXEL DATA (R0–R7, G0–G7, B0–B7); PALETTE SELECT INPUTS (PS0-PS1); SYNC; BLANK

Figure 4. Pixel Input to Analog Output Pipeline with Minimum LOADOUT to LOADIN Delay (2:1 Multiplex Mode)

CLOCK

LOADOUT

τ

τ- t11

LOADIN

PIXEL INPUT

DATA*

ANALOG

OUTPUT

DATA

AN BN

AN+1BN+1

AN+2BN+2

DIGITAL INPUT TO ANALOG OUTPUT PIPELINE

IOR, IOR

IOG, IOG

IOB, IOB

IPLL, SYNCOUT

AN-1

BN-1

AN

BN

AN+1

BN+1 AN+2

BN+2

tPD

*INCLUDES PIXEL DATA (R0–R7, G0–G7, B0–B7); PALETTE SELECT INPUTS (PS0–PS1); SYNC; BLANK

Figure 5. Pixel Input to Analog Output Pipeline with Maximum LOADOUT to LOADIN Delay (2:1 Multiplex Mode)

CLOCK

PRGCKOUT

(CLOCK/4)

PRGCKOUT

(CLOCK/8)

PRGCKOUT

(CLOCK/16)

PRGCKOUT

(CLOCK/32)

t12

*INLCUDES PIXEL DATA (R0-R7, G0-G7, B0-B7); PALETTE SELECT INPUTS (PS0-PS1); SYNC; BLANK

Figure 6. Pixel Clock Input vs. Programmable Clock Output (PRGCKOUT)

REV. B

–5–

5 Page

ADV7152

Color data is latched into the parts pixel port on every rising

edge of LOADIN (see Timing Waveform, Figure 3). The

required frequency of LOADIN is determined by the multiplex

rate, where

fLOADIN = fCLOCK/2

fLOADIN = fCLOCK

2:1 Multiplex Mode

1:1 Multiplex Mode

Other pixel data signals latched into the device by LOADIN

include SYNC, BLANK and PS0–PS1.

Internally, data is pipelined through the part by the differential

pixel clock inputs, CLOCK and CLOCK. The LOADIN con-

trol signal needs only have a frequency synchronous relationship

to the pixel CLOCK (see “Pipeline Delay & Onboard Calibra-

tion” section). A completely phase independent LOADIN signal

can be used with the ADV7152, allowing the CLOCK to occur

anywhere during the LOADIN cycle.

Alternatively, the LOADOUT signal of the ADV7152 can be

used. LOADOUT can be connected either directly or indirectly

to LOADIN. Its frequency is automatically set to the correct

LOADIN requirement.

resultant pixel or dot clock rate of 100 MHz. As mentioned in

the previous section, the ADV7152 supports a number of color

data formats in 2:1 and 1:1 multiplex modes.

In 1:1 multiplex mode, the ADV7152 is clocked using the

LOADIN signal. This means that there is no requirement for

differential ECL inputs on CLOCK and CLOCK. The pixel

clock is connected directly to LOADIN. (Note: The ECL

CLOCK can still be used to generate LOADOUT PRGCKOUT,

etc.)

VIDEO MEMORY/

FRAME BUFFER

VRAM (BANK A) 50MHz

24

VRAM (BANK B) 50MHz

24

ADV7152

A

24

MULTIPLEXER

B

100MHz

(2 x 50MHz)

SYNC, BLANK

The BLANK and SYNC video control signals drive the analog

outputs to the blanking and SYNC levels respectively. These

signals are latched into the part on the rising edge of LOADIN.

The SYNC information is encoded onto the IOG analog signal

when bit CR22 of Command Register 2 is set to a Logic “1.”

The SYNC input is ignored if CR22 is set to “0.”

SYNCOUT

In some applications where it is not permissible to encode

SYNC on green (IOG), SYNCOUT can be used as a separate

TTL digital SYNC output. This has the advantage over an inde-

pendent (of the ADV7150) SYNC in that it does not necessitate

knowing the absolute pipeline delay of the part. This allows

complete independence between LOADIN/Pixel Data and

CLOCK. The SYNC input is connected to the device as normal

with Bit CR22 of Command Register 2 set to “0” thereby pre-

venting SYNC from being encoded onto IOG. Bit CR12 of

Command Register 1 is set to “1,” enabling SYNCOUT. The

output signal generates a TTL SYNCOUT with correct pipeline

delay that is capable of directly driving the composite SYNC

signal of a computer monitor.

PS0–PS1 (Palette Priority Select Inputs)

These pixel port select inputs determine whether or not the de-

vice is selected. These controls effectively determine whether the

devices RGB analog outputs are turned-on or shut down. When

the analog outputs are shut down, IOR, IOG and IOB are

forced to 0 mA regardless of the state of the pixel and control

data inputs. This state is determined on a pixel by pixel basis as

the PS0–PS1 inputs are multiplexed in exactly the same format

as the pixel port color data. These controls allow for switching

between multiple palette devices (see Appendix 4). If the values

of PS0 and PSI match the values programmed into bits MR16

and MR17 of the Mode Register, then the device is selected, if

there is no match the device is effectively shut down.

Multiplexing

The onboard multiplexers of the ADV7152 eliminate the need

for external data serializer circuits. Multiple video memory de-

vices can be connected, in parallel, directly to the device. Fig-

ure 11 shows two memory banks of 50 MHz memory connected

to the ADV7152, running in 2:1 multiplex mode, giving a

Figure 11. Direct Interfacing of Video Memory to

ADV7152

CLOCK CONTROL CIRCUIT

The ADV7152 has an integrated Clock Control Circuit (Figure

12). This circuit is capable of both generating the ADV7152’s

internal clocking signals as well as external graphics subsystem

clocking signals. Total system synchronization can be attained

by using the parts output clocking signals to drive the control-

ling graphics processor’s master clock as well as the video frame

buffers shift clock signals.

CLOCK, CLOCK Inputs

The Clock Control Circuit is driven by the pixel clock inputs,

CLOCK and CLOCK. These inputs can be driven by a differ-

ential ECL oscillator running from a +5 V supply.

CLOCK

CLOCK

ECL

TO

TTL

PRGCKOUT

LOADOUT

SCKOUT

BLANK

SYNC

SCKIN

DIVIDE BY N

(÷ N)

DIVIDE BY M

(÷ M)

LATCH

ENABLE

LOADIN

ADV7152

TO COLOR DATA

MULTIPLEXER

M IS A FUNCTION OF MULTIPLEX RATE

M = 2 IN 2:1 MULTIPLEX MODE

M = 1 IN 1:1 MULTIPLEX MODE

N IS INDEPENDENTLY

PROGRAMMABLE

N= (4, 8, 16, 32)

Figure 12. Clock Control Circuit of the ADV7152

REV. B

–11–

11 Page | ||

| Páginas | Total 32 Páginas | |

| PDF Descargar | [ Datasheet ADV7152.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADV7150 | CMOS 220 MHz True-Color Graphics Triple 10-Bit Video RAM-DAC | Analog Devices |

| ADV7151 | CMOS 220 MHz Pseudo-Color Graphics Triple 10-Bit Video RAM-DAC | Analog Devices |

| ADV7152 | CMOS 220 MHz True-Color Graphics Triple 10-Bit Video RAM-DAC | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |