|

|

PDF ADP3806JRU-126 Data sheet ( Hoja de datos )

| Número de pieza | ADP3806JRU-126 | |

| Descripción | High-Frequency Switch Mode Li-Ion Battery Charger | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ADP3806JRU-126 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

a

FEATURES

Li-Ion Battery Charger

Three Battery Voltage Options

Selectable 12.525 V/16.700 V

Selectable 12.600 V/16.800 V

Adjustable

High End-of-Charge Voltage Accuracy

؎0.4% @ 25؇C

؎0.6% @ 5؇C to 55ЊC

؎0.7% @ 0؇C to 85؇C

Programmable Charge Current with Rail-to-Rail

Sensing

System Current Sense with Reverse Input Protection

Softstart Charge Current

Undervoltage Lockout

Bootstrapped Synchronous Drive for External NMOS

Programmable Oscillator Frequency

Oscillator SYNC Pin

Low Current Flag

Trickle Charge

APPLICATIONS

Portable Computers

Fast Chargers

High-Frequency Switch Mode

Li-Ion Battery Charger

ADP3806

GENERAL DESCRIPTION

The ADP3806 is a complete Li-Ion battery-charging IC. The

device combines high output voltage accuracy with constant

current control to simplify the implementation of Constant-

Current, Constant-Voltage (CCCV) chargers. The ADP3806 is

available in three options. The ADP3806-12.6 guarantees the

final battery voltage be selected to 12.6 V or 16.8 V ± 0.6%, the

ADP3806-12.5 guarantees 12.525 V/16.7 V ± 0.6% and the

ADP3806 is adjustable using two external resistors to set the

battery voltage. The current sense amplifier has rail-to-rail

inputs to accurately operate under low drop out and short circuit

conditions. The charge current is programmable with a dc

voltage on ISET. A second differential amplifier senses the system

current across an external sense resistor and outputs a linear

voltage on the ISYS pin. The bootstrapped synchronous driver

allows the use of two NMOS transistors for lower system cost.

BSTREG

SD

LC

FUNCTIONAL BLOCK DIAGRAM

VCC BST DRVH SW DRVL PGND

CS+ CS–

SYS+ SYS–

ISYS

VREF + VREG

UVLO

BIAS

BOOTSTRAPPED

SYNCHRONOUS

DRIVER

SD

VREF

IN DRVLSD DRVLSD

–+

–+

+

LOGIC

CONTROL

–

+–

AMP1

VTH

–

gm1

+

ADP3806

OSCILLATOR

–

gm2

+

VREF

–+

AMP2

2.5V

–

+

SELECT

12.6/16.8

LIMIT

ISET

BAT

AGND

REG REF SYNC

CT

COMP

BATSEL

REV. 0

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2001

1 page

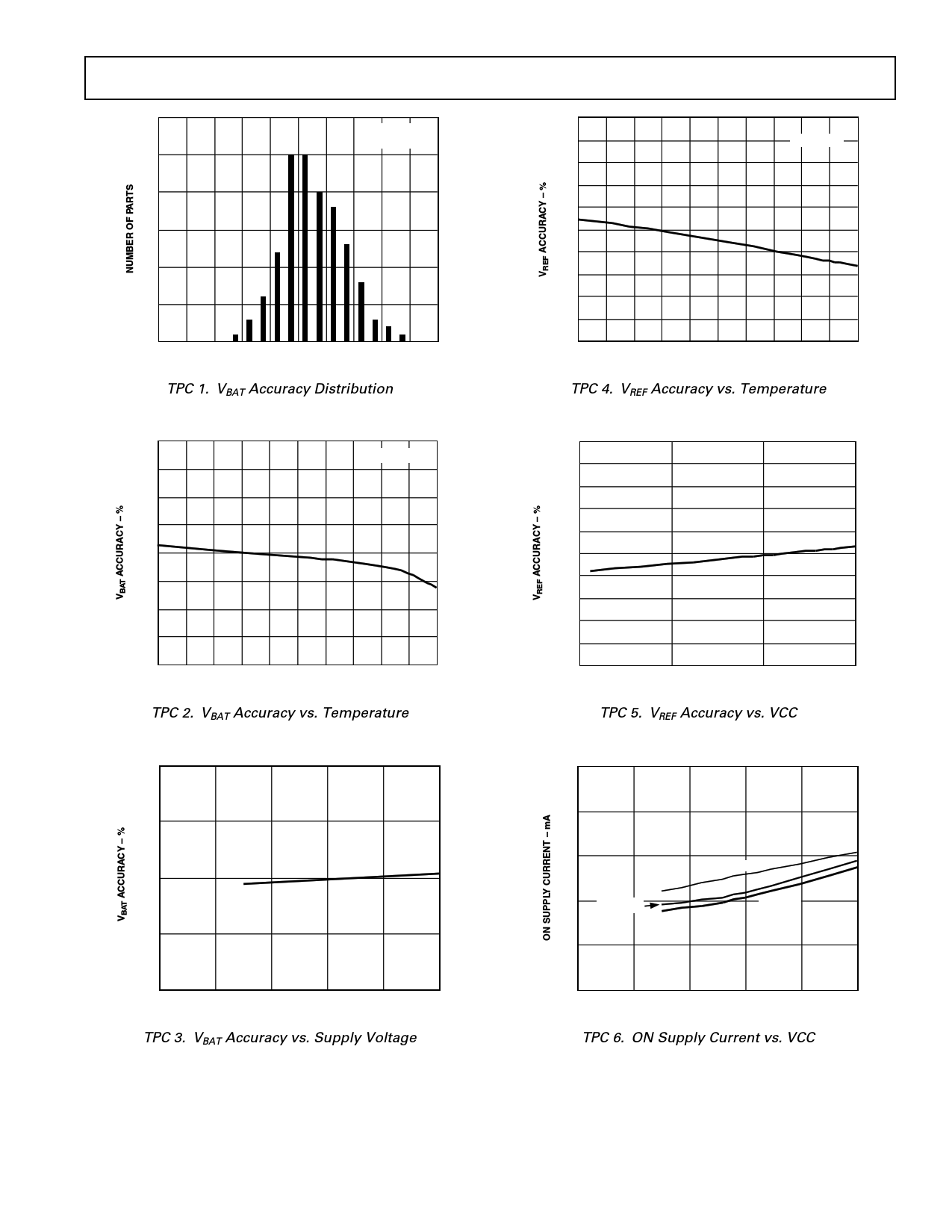

Typical Performance Characteristics–ADP3806

30

VCC = 16V

TA = 25؇C

25

20

15

10

5

0

–0.5 –0.4 –0.3 –0.2 –0.1 0.0 0.1 0.2 0.3 0.4

VBAT ACCURACY – %

TPC 1. VBAT Accuracy Distribution

0.5

0.5

0.4 VCC = 16V

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

–0.4

–0.5

0

20 40

60

TEMPERATURE – ؇C

80

100

TPC 4. VREF Accuracy vs. Temperature

0.4

VCC = 16V

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

–0.4

0

20 40 60

TEMPERATURE – ؇C

80

TPC 2. VBAT Accuracy vs. Temperature

100

0.10

0.08

0.06

0.04

0.02

0

–0.02

–0.04

–0.06

–0.08

–0.10

5

TA = 25؇C

10 15

VCC – V

TPC 5. VREF Accuracy vs. VCC

20

0.10

0.05

TA = 25؇C

0

–0.05

–0.10

10 12 14 16 18 20

VCC – V

TPC 3. VBAT Accuracy vs. Supply Voltage

6.0

NO LOADS

5.6

5.2

4.8 TA = 25؇C

4.4

TA = 100؇C

TA = 0؇C

4.0

10 12 14 16 18

VCC – V

TPC 6. ON Supply Current vs. VCC

20

REV. 0

–5–

5 Page

ADP3806

Shutdown

A high impedance CMOS logic input is provided to turn off

the ADP3806. When the voltage on SD is less than 0.8 V, the

ADP3806 is placed in low power shutdown. With the exception

of the system current sense amplifier, AMP2, all other circuitry

is turned off. The reference and regulators are pulled to ground

during shutdown and all switching is stopped. During this state,

the supply current is less than 5 µA. Also, the BAT, CS+, CS–,

and SW pins go to high impedance to minimize current drain

from the battery.

UVLO

Under-Voltage Lock-Out, UVLO, is included in the ADP3806

to ensure proper start-up. As VCC rises above 1 V, the refer-

ence and regulators will track VCC until they reach their final

voltages. However, the rest of the circuitry is held off by the

UVLO comparator. The UVLO comparator monitors both

regulators to ensure that they are above 5 V before turning on

the main charger circuitry. This occurs when VCC reaches 6 V.

Monitoring the regulator outputs makes sure that the charger

circuitry and driver stage have sufficient voltage to operate nor-

mally. The UVLO comparator includes 300 mV of hysteresis to

prevent oscillations near the threshold.

Startup Sequence

During a startup from either SD going high or VCC exceed-

ing the UVLO threshold, the ADP3806 initiates a soft-start

sequence. The soft-start timing is set by the compensation

capacitor at the COMP pin and an internal 40 µA source. Ini-

tially, both DRVH and DRVL are held low until VCOMP reaches

1 V. This delay time is set by:

tDELAY

=

CCOMP × 1V

40 µA

(4)

For a 0.22 µF COMP capacitor, tDELAY is 5 ms. After this initial

delay, the duty cycle is very low and then ramps up to its final value

with the same ramp rate given for tDELAY. For example, if VIN is

16 V and the battery is 10 V when charging is started, the duty cycle

will be approximately 65%, corresponding to a VCOMP of ~2 V. The

time for the duty cycle to ramp from 0% at VCOMP = 1 V to 65%

at VCOMP = 2 V is approximately 5 ms. Because the charge current

is equal to zero at first, DRVLSD is active and DRVL will not turn

on. However, if the BST cap is discharged, DRVL will be forced

on for a minimum ON time of 200 ns each clock period until the

BST cap is charged to greater than 4 V. Typically the BST cap is

charged in 5 to 10 clock cycles.

Loop Feed Forward

As the startup sequence discussion shows, the response time at

COMP is slowed by the large compensation capacitor. To speed

up the response, two comparators can quickly feed forward

around the normal control loop and pull the COMP node down

to limit any over shoot in either short circuit or overvoltage

conditions. The overvoltage comparator has a trip point set to

20% higher than the final battery voltage. The overcurrent com-

parator threshold is set to 180 mV across the CS pins, which

is 15% above the maximum programmable threshold. When

these comparators are tripped, a normal soft-start sequence is

initiated. The overvoltage comparator is valuable when the

battery is removed during charging. In this case, the current in

the inductor causes the output voltage to spike up, and the

comparator limits the maximum voltage. Neither of these com-

parators affect the loop under normal charging conditions.

APPLICATION INFORMATION

Design Procedure

Please refer to Figure 1, the typical application circuit, for the

following description. The design follows that of a buck con-

verter. With Li-Ion cells it is important to have a regulator with

accurate output voltage control.

Battery Voltage Settings: The ADP3806 has three options for

voltage selection:

1. 12.525 V/16.7 V as selectable fixed voltages.

2. 12.6 V/16.8 V as selectable fixed voltages.

3. Adjustable.

When using the fixed versions, R11 should be a short or 0 Ω

wire jumper and R12 should be an open circuit. When using

the adjustable version, the following equation gives the ratio

of the two resistors:

R11

R12

=

VBAT

2.5

–

1

(5)

Often 0.1% resistors are required to maintain the overall accu-

racy budget in the design.

Inductor Selection: Usually the inductor is chosen based on the

assumption that the inductor ripple current is ± 15% of the

maximum output dc current at maximum input voltage. As long

as the inductor used has a value close to this, the system should

work fine. The final choice affects the trade-offs between cost,

size, and efficiency. For example, the lower the inductance, the

size is smaller but ripple current is higher. This situation, if taken

too far, will lead to higher ac losses in the core and the windings.

Conversely, a higher inductance results in lower ripple current

and smaller output filter capacitors, but the transient response

will be slower. With these considerations the required induc-

tance can be found from:

L1

=

VIN ,

MAX – VBAT

∆I

× DMIN

× TS

(6)

where the maximum input voltage VIN, MAX is used with the

minimum duty ratio DMIN. The duty ratio is defined as the ratio

of the output voltage to the input voltage, VBAT/VIN. The ripple

current is found from:

∆I = 0.3 × IBAT , MAX

(7)

the maximum peak-to-peak ripple is 30%, that is 0.3, and maxi-

mum battery current, IBAT, MAX is used.

For example, with VIN, MAX = 19 V, VBAT = 12.6 V, IBAT, MAX =

3A, and TS = 4 µs, the value of L1 is calculated as 18.9 µH.

Choosing the closest standard value gives L1 = 22 µH.

Output Capacitor Selection: An output capacitor is needed

in the charger circuit to absorb the switching frequency ripple

current and smooth the output voltage. The RMS value of the

output ripple current is given by:

( )IRMS = VIN, MAX D 1 – D

fL1 12

(8)

The maximum value occurs when the duty cycle is 0.5. Thus:

I RMS _ MAX

= 0.072VIN , MAX

fL1

(9)

REV. 0

–11–

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet ADP3806JRU-126.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ADP3806JRU-125 | High-Frequency Switch Mode Li-Ion Battery Charger | Analog Devices |

| ADP3806JRU-126 | High-Frequency Switch Mode Li-Ion Battery Charger | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |