|

|

PDF AD1837 Data sheet ( Hoja de datos )

| Número de pieza | AD1837 | |

| Descripción | 2 ADC/ 8 DAC/ 96 kHz/ 24-Bit Codec | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AD1837 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

2 ADC, 8 DAC,

96 kHz, 24-Bit ⌺-⌬ Codec

AD1837

FEATURES

5 V Stereo Audio System with 3.3 V Tolerant

Digital Interface

Supports up to 96 kHz Sample Rates

192 kHz Sample Rate Available on One DAC

Supports 16-/20-/24-Bit Word Lengths

Multibit ⌺-⌬ Modulators with

Perfect Differential Linearity Restoration for

Reduced Idle Tones and Noise Floor

Data Directed Scrambling DACs—Least

Sensitive to Jitter

Single-Ended Outputs

ADCs: –95 dB THD + N, 105 dB SNR and

Dynamic Range

DACs: –92 dB THD + N, 108 dB SNR and

Dynamic Range

On-Chip Volume Controls per Channel with

1024-Step Linear Scale

DAC and ADC Software Controllable Clickless Mutes

Digital De-emphasis Processing

Supports 256 ؋ fS, 512 ؋ fS, and 768 ؋ fS Master Mode

Clocks

Power-Down Mode Plus Soft Power-Down Mode

Flexible Serial Data Port with Right-Justified, Left-

Justified, I2S Compatible, and DSP Serial Port Modes

TDM Interface Mode Supports 8 In/8 Out Using a

Single SHARC® SPORT

52-Lead MQFP Plastic Package

APPLICATIONS

DVD Video and Audio Players

Home Theater Systems

Automotive Audio Systems

Audio/Visual Receivers

Digital Audio Effects Processors

PRODUCT OVERVIEW

The AD1837 is a high performance single-chip codec featuring

four stereo DACs and one stereo ADC. Each DAC comprises a

high performance digital interpolation filter, a multibit ⌺-⌬

modulator featuring Analog Devices’ patented technology, and

a continuous-time voltage out analog section. Each DAC has

independent volume control and clickless mute functions. The

ADC comprises two 24-bit conversion channels with multibit

⌺-⌬ modulators and decimation filters.

The AD1837 also contains an on-chip reference with a nominal

value of 2.25 V.

The AD1837 contains a flexible serial interface that allows for

glueless connection to a variety of DSP chips, AES/EBU receiv-

ers, and sample rate converters. The AD1837 can be configured

in left-justified, right-justified, I2S, or DSP compatible serial

modes. Control of the AD1837 is achieved by means of an SPI

compatible serial port. While the AD1837 can be operated from

a single 5 V supply, it also features a separate supply pin for its

digital interface that allows the device to be interfaced to other

devices using 3.3 V power supplies.

The AD1837 is available in a 52-lead MQFP package and is

specified for the industrial temperature range of –40ºC to +85ºC.

FUNCTIONAL BLOCK DIAGRAM

DVDD DVDD ODVDD ALRCLK ABCLK ASDATA CCLK CLATCH CIN COUT MCLK PD/RST M/S AVDD AVDD

REV. B

DLRCLK

DBCLK

DSDATA1

DSDATA2

DSDATA3

DSDATA4

ADCLP

ADCLN

ADCRP

ADCRN

⌺-⌬

ADC

⌺-⌬

ADC

AD1837

SERIAL DATA

I/O PORT

DIGITAL

FILTER

DIGITAL

FILTER

CONTROL PORT

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

VOLUME

CLOCK

DIGITAL

FILTER

DIGITAL

FILTER

DIGITAL

FILTER

DIGITAL

FILTER

DGND DGND AGND AGND AGND AGND

⌺-⌬

DAC

⌺-⌬

DAC

⌺-⌬

DAC

⌺-⌬

DAC

VREF

OUTL1

OUTR1

OUTL2

OUTR2

OUTL3

OUTR3

OUTL4

OUTR4

FILTD

FILTR

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties that

may result from its use. No license is granted by implication or otherwise

under any patent or patent rights of Analog Devices. Trademarks and

registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700

www.analog.com

Fax: 781/326-8703 © 2003 Analog Devices, Inc. All rights reserved.

1 page

Parameter

TDM256 MODE (Master)

tTBD

tFSD

tTABDD

tTDDS

tTDDH

BCLK Delay

FSTDM Delay

ASDATA Delay

DSDATA1 Setup

DSDATA1 Hold

TDM256 MODE (Slave)

fAB

tTBCH

tTBCL

tTFS

tTFH

tTBDD

tTDDS

tTDDH

BCLK Frequency

BCLK High

BCLK Low

FSTDM Setup

FSTDM Hold

ASDATA Delay

DSDATA1 Setup

DSDATA1 Hold

AUXILIARY INTERFACE

tAXDS

tAXDH

fABP

Slave Mode

AAUXDATA Setup

AAUXDATA Hold

AUXBCLK Frequency

tAXBH

tAXBL

tAXLS

tAXLH

Master Mode

AUXBCLK High

AUXBCLK Low

AUXLRCLK Setup

AUXLRCLK Hold

tAUXBCLK

tAUXLRCLK

AUXLRCLK Delay

AUXLRCLK Delay

Specifications subject to change without notice.

Min Max

20

5

10

15

15

256 ϫ fS

15

15

10

10

15

15

10

10

10

64 ϫ fS

15

15

10

10

15

15

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

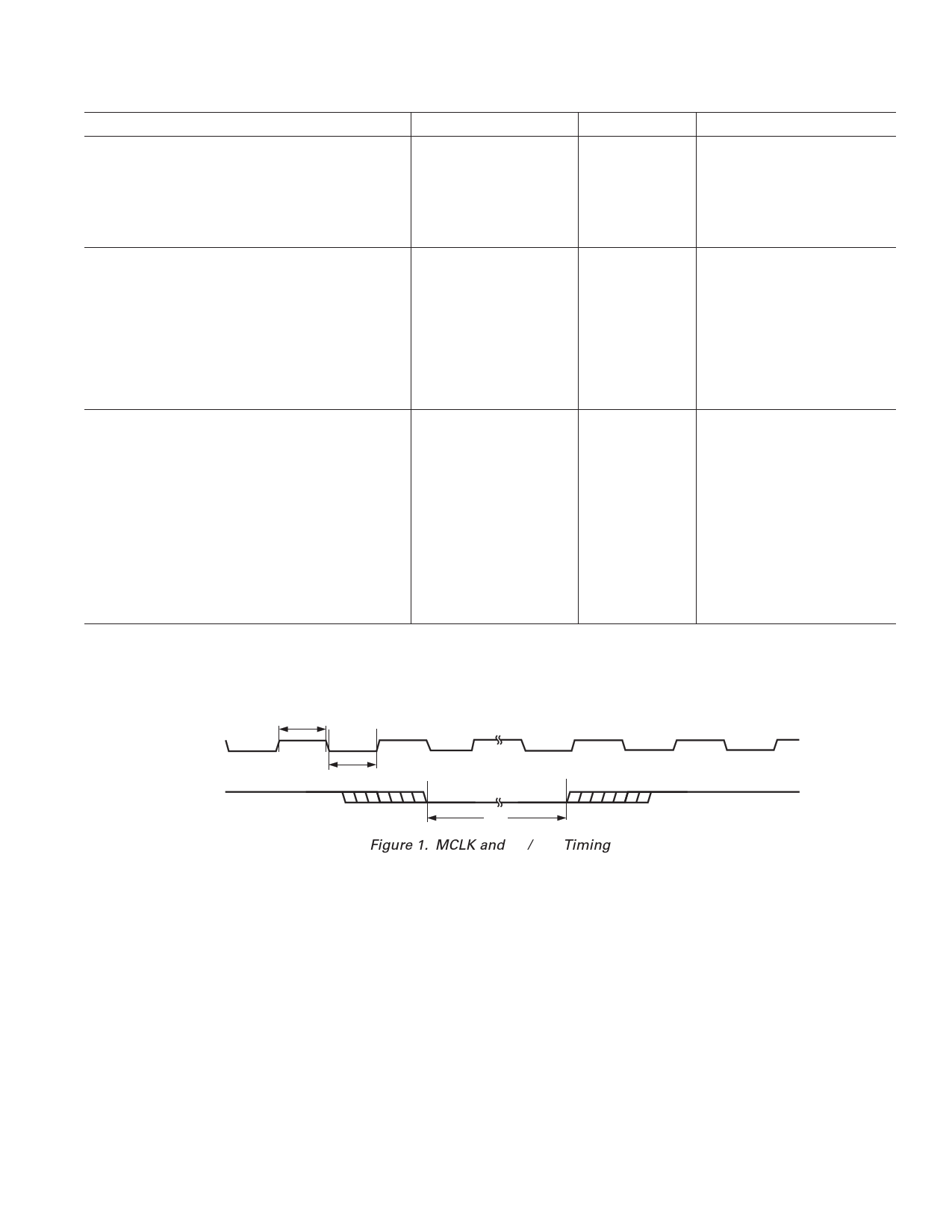

MCLK

PD/RST

tMH

tML

tPDR

Figure 1. MCLK and PD/RST Timing

AD1837

Comments

From MCLK Rising

From BCLK Rising

From BCLK Rising

To BCLK Falling

From BCLK Falling

To BCLK Falling

From BCLK Falling

From BCLK Rising

To BCLK Falling

From BCLK Falling

To AUXBCLK Rising

From AUXBCLK Rising

To AUXBCLK Rising

From AUXBCLK Rising

From MCLK Rising

From AUXBCLK Falling

REV. B

–5–

5 Page

AD1837

FUNCTIONAL OVERVIEW

ADCs

There are two ADC channels in the AD1837, configured as a

stereo pair. Each ADC has fully differential inputs. The ADC

section can operate at a sample rate of up to 96 kHz. The ADCs

include on-board digital decimation filters with 120 dB stop-band

attenuation and linear phase response, operating at an over-

sampling ratio of 128 (for 48 kHz operation) or 64 (for 96 kHz

operation).

ADC peak level information for each ADC may be read from

the ADC Peak 0 and ADC Peak 1 registers. The data is supplied

as a 6-bit word with a maximum range of 0 dB to –63 dB and a

resolution of 1 dB. The registers will hold peak information until

read; after reading, the registers are reset so that new peak

information can be acquired. Refer to the register description

for details on the format. The two ADC channels have a common

serial bit clock and a left-right framing clock. The clock signals

are all synchronous with the sample rate.

The ADC digital pins, ABCLK and ALRCLK, can be set to

operate as inputs or outputs by connecting the M/S pin to

ODVDD or DGND, respectively. When the pins are set as

outputs, the AD1837 will generate the timing signals. When

the pins are set as inputs, the timing must be generated by the

external audio controller.

DACs

The AD1837 has eight DAC channels arranged as four inde-

pendent stereo pairs, with eight single-ended analog outputs for

improved noise and distortion performance. Each channel has

its own independently programmable attenuator, adjustable in

1024 linear steps. Digital inputs are supplied through four serial

data input pins (one for each stereo pair) and a common frame

(DLRCLK) and bit (DBLCK) clock. Alternatively, one of the

“packed data” modes may be used to access all eight channels

on a single TDM data pin. A stereo replicate feature is included

where the DAC data sent to the first DAC pair is also sent to the

other DACs in the part. The AD1837 can accept DAC data at a

sample rate of 192 kHz on DAC 1 only. The stereo replicate fea-

ture can then be used to copy the audio data to the other DACs.

Each of the output pins sits at a dc level of VREF and swings

± 1.4 V for a 0 dB digital input signal. A single op amp third

order external low-pass filter is recommended to remove high

frequency noise present on the output pins. Note that the use of

op amps with low slew rate or low bandwidth may cause high

frequency noise and tones to fold down into the audio band;

care should be exercised in selecting these components.

The FILTD pin should be connected to an external grounded

capacitor. This pin is used to reduce the noise of the internal

DAC bias circuitry, thereby reducing the DAC output noise. In

some cases, this capacitor may be eliminated with little effect

on performance.

DAC and ADC Coding

The DAC and ADC output data stream is in a twos complement

encoded format. The word width can be selected from 16-bit,

20-bit, or 24-bit. The coding scheme is detailed in Table I.

Table I. Coding Scheme

Code

01111......1111

00000......0000

10000......0000

Level

+FS

0 (Ref Level)

–FS

Clock Signals

The DAC and ADC engines in the AD1837 are designed to

operate from a 24.576 MHz internal master clock (IMCLK).

This clock is used to generate 48 kHz and 96 kHz sampling on

the ADC and 48 kHz, 96 kHz, and 192 kHz on the DAC,

although the 192 kHz option is available only on one DAC pair.

The stereo replicate feature can be used to copy this DAC data

to the other DACs if required.

To facilitate the use of different MCLK values, the AD1837

provides a clock scaling feature. The MCLK scaler can be

programmed via the SPI port to scale the MCLK by a factor of

1 (pass through), 2 (doubling), or 2/3. The default setting of

the MCLK scaler is 2, which will generate 48 kHz sampling

from a 12.288 MHz MCLK. Additional sample rates can be

achieved by changing the MCLK value. For example, the CD

standard sampling frequency of 44.1 kHz can be achieved using

an 11.2896 kHz MCLK. Figure 2 shows the internal configura-

tion of the clock scaler and converter engines.

DAC INPUT 48kHz/96kHz/192kHz

INTERPOLATION

FILTER

DAC ENGINE

⌺-⌬

MODULATOR

MCLK

12.288MHz

CLOCK SCALING

؋1

؋2

؋ 2/3

IMCLK = 24.576MHz

ADC OUTPUT

48kHz/96kHz

OPTIONAL

HPF

ADC ENGINE

DECIMATOR/

FILTER

DAC

⌺-⌬

MODULATOR

Figure 2. Modulator Clocking Scheme

ANALOG

OUTPUT

ANALOG

INPUT

REV. B

–11–

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet AD1837.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AD1833 | Multichannel 24-Bit/ 192 kHz/ DAC | Analog Devices |

| AD1833A | 24-Bit/ 192 kHz/ DAC | Analog Devices |

| AD1835 | 2 ADC/ 8 DAC/ 96 kHz/ 24-Bit Codec | Analog Devices |

| AD1835A | Codecs | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |