|

|

PDF A8351601-40 Data sheet ( Hoja de datos )

| Número de pieza | A8351601-40 | |

| Descripción | Bar Code Reader | |

| Fabricantes | AMIC Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de A8351601-40 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

A8351601 Series

Bar Code Reader

Document Title

Bar Code Reader

Revision History

Rev. No.

0.0

0.1

0.2

0.3

0.4

0.5

0.6

1.0

History

Initial issue

Change document title from “Bar Code Reader” to

“8 Bit Microcontroller”

Error correction:

(1) Delete single-step operation description

(2) Delete “the only exit from power down is a hardware

reset” on page 32

Modify 44L QFP package outline drawing and dimensions

Modify PWM function

(1) Add PWM3 delay control bits D0, D1 and D2

(2) Add PWM4 output control bit PWM1.7

Error correction:

Delete Functional Description

Change document title from “8 Bit Microcontroller” to

“Bar Code Reader”

Modify AC, DC Electrical Characteristics:

Add 3V ± 10% condition

SFR Map address has some typewriting errors

Modify DC and AC Electrical Characteristics

Final version release

Issue Date

June 5, 2000

June 22, 2000

Remark

Preliminary

November 15, 2000

January 17, 2001

June 6, 2001

October 16, 2001

February 19, 2002

July 12, 2002

Final

(July, 2002, Version 1.0)

AMIC Technology, Inc.

1 page

A8351601 Series

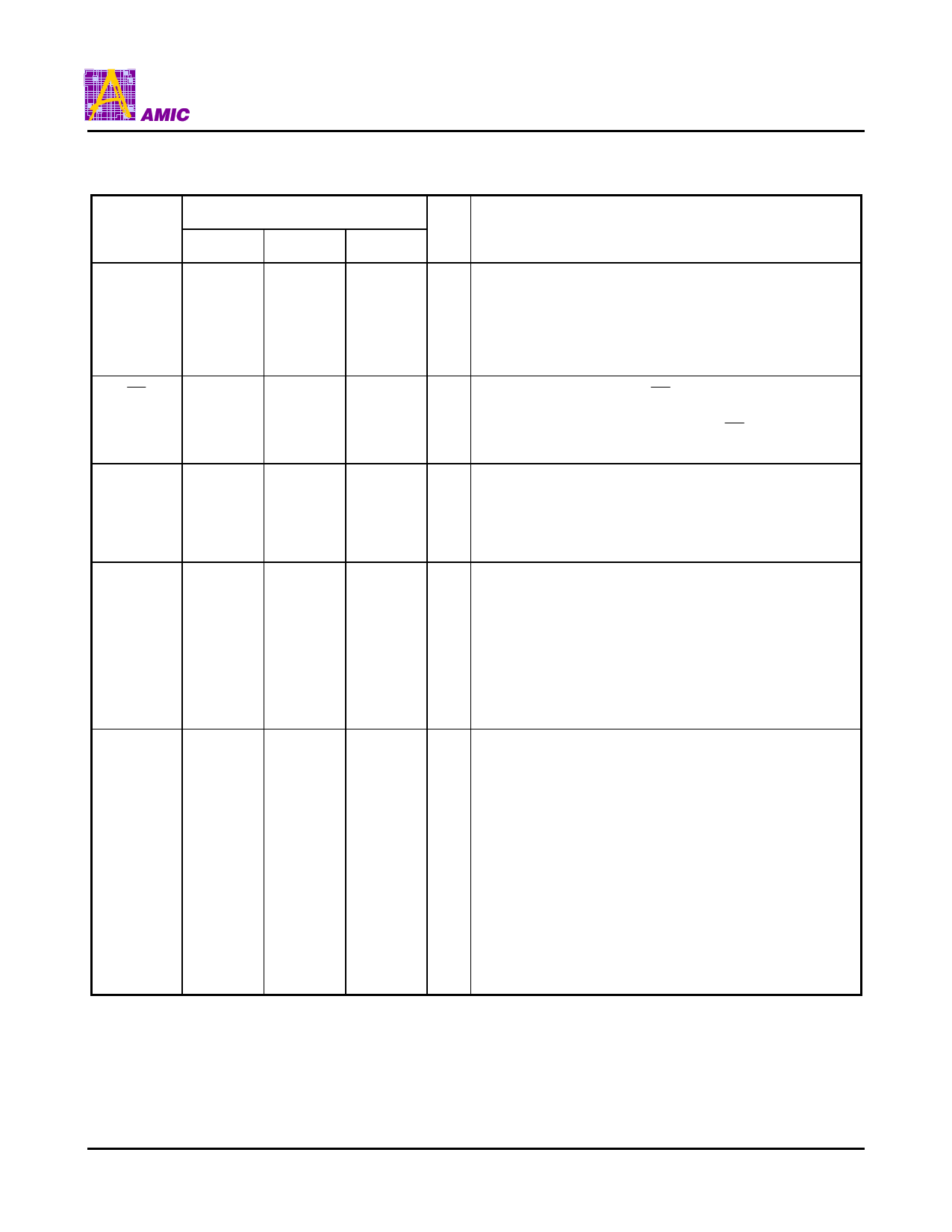

Pin Description

Symbol

ALE

P-DIP

30

EA 31

P0.0-P0.7

32-39

P1.0-P1.7

1-8

P2.0-P2.7

1

2

21-28

Pin No.

PLCC

33

35

36-43

2-9

2

3

24-31

QFP

27

29

30-37

40-44

40

41

18-25

I/O Description

O Address Latch Enable: Output pulse for latching the low

byte of the address during an address to the external

memory. In normal operation, ALE is emitted at a constant

rate of 1/6 the oscillator frequency, and can be used for

external timing or clocking. Note that one ALE pulse is

skipped during each access to external data memory.

I External Access enable: EA must be externally held low

to enable the device to fetch code from external program

memory locations 0000H to FFFFH. If EA is held high, the

device executes from internal program memory.

I/O Port 0: Port 0 is an 8-bit bidirectional I/O port with internal

pullups. Port 0 pins that have 1s written to them are pulled

high by the internal pullups and can be used as inputs. Port

0 is also the multiplexed low-order address and data bus

during accesses to external program and data memory.

I/O Port 1: Port 1 is an 8-bit bidirectional I/O port with internal

pullups. Port 1 pins that have 1s written to them are pulled

high by the internal pullups and can be used as inputs. As

inputs, Port 1 pins that are externally pulled low will source

current because of the internal pullups. (See DC

Characteristics: IIL).

The Port 1 output buffers can sink/source four TTL inputs.

I T2 (P1.0): Timer/Counter 2 external count input.

I T2EX (P1.1): Timer/Counter 2 trigger input.

I/O Port 2: Port 2 is an 8-bit bidirectional I/O port with internal

pullups. Port 2 pins that have 1s written to them are pulled

high by the internal pullups and can be used as inputs. As

inputs, Port 2 pins that are externally pulled low will source

current because of the internal pullups. (See DC

Characteristics: IIL).

Port 2 emits the high order address byte during fetches

from external program memory and during accesses to

external data memory that used 16-bit addresses (MOVX @

DPTR). In this application, Port 2 uses strong internal

pullups when emitting 1s. During accesses to external data

memory that use 8-bit addresses (MOVX @ Ri [i = 0, 1]),

Port 2 emits the contents of the P2 Special Function

Register.

Port 2 also receives the high-order bits and some control

signals during ROM verification.

(July, 2002, Version 1.0)

4 AMIC Technology, Inc.

5 Page

A8351601 Series

Note 1:

M1

0

0

1

1

1

M0 Operating mode

0 Mode 0. (13-bit Timer)

1 Mode 1. (16-bit Timer/Counter)

0 Mode 2. (8-bit auto-load Timer/Counter)

1 Mode 3. (Splits Timer 0 into TL0 and TH0. TL0 is an 8-bit Timer/

Counter controller by the standard Timer 0 control bits. TH0 is an

8-bit Timer and is controlled by Timer 1 control bits.)

1 Mode 3. (Timer/Counter 1 stopped).

SCON:

Serial Port Control Register. Bit Addressable.

76

SM0

SM1

Register Description:

SM0

SCON.7

SM1

SCON.6

SM2

SCON.5

REN

TB8

RB8

TI

RI

SCON.4

SCON.3

SCON.2

SCON.1

SCON.0

5432

SM2 REN TB8 RB8

1

TI

0

RI

Serial port mode specifically. (1)

Serial port mode specifically. (1)

Enable the multiprocessor communication feature in mode 2 and 3. In mode 2 or 3, if SM2

is set to 1 then RI will not be activated if the received 9th data bit (RB8) is 0. In mode 1, if

SM2=1 then RI will not be activated if valid stop bit was not received. In mode 0, SM2

should be 0.

Set/Cleared by software to Enable/Disable reception.

The 9th bit that will be transmitted in mode 2 and 3. Set/Cleared by software.

In modes 2 and 3, RB8 is the 9th data bit that was received. In mode 1, if SM2=0, RB8 is

the stop bit that was received. In mode 0, RB8 is not used.

Transmit interrupt flag. Set by hardware at the end of the 8th bit time in mode 0, or at the

beginning of the stop bit in the other modes. Must be cleared by software.

Receive interrupt flag. Set by hardware at the end of the 8th bit time in mode 0, or halfway

through the stop bit time in the other modes (except see SM2). Must be cleared by

software.

Note:

SM0

0

0

1

1

SM1

0

1

0

1

MODE

0

1

2

3

Description

Shift register

8-bit UART

9-bit UART

9-bit UART

Baud rate

Fosc/12

Variable

Fosc/64 or Fosc/32

Variable

T2CON:

Timer/Counter 2 Control Register. Bit Addressable.

76

TF2 EXF2

Register Description:

TF2 T2CON.7

EXF2

T2CON.6

RCLK

T2CON.5

TCLK

T2CON.4

5

RCLK

4

TCLK

3

EXEN2

2

TR2

1

C/ T2

0

CP/ RL2

Timer 2 overflow flag set by hardware and cleared by software. TF2 cannot be set when

either RCLK = 1 or TCLK = 1.

Timer 2 external flag set when either a capture or reload is caused by a negative transition

on T2EX, and EXEN2 = 1. When Timer 2 interrupt is enabled, EXF2 = 1 causes the CPU to

vector to the Timer 2 interrupt routine. EXF2 must be cleared by software.

Receive clock flag. When set, causes the Serial Port to use Timer 2 overflow pulses for its

receive clock in modes 1 and 3. RCLK = 0 causes Timer 1 overflow to be used for the

receive clock.

Transmit clock flag. When set, causes the Serial Port to use Timer 2 overflow pulses for its

transmit clock in modes 1 and 3. TCLK = 0 causes Timer 1 overflows to be used for the

transmit clock.

(July, 2002, Version 1.0)

10 AMIC Technology, Inc.

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet A8351601-40.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| A8351601-40 | Bar Code Reader | AMIC Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |