|

|

PDF CS49400 Data sheet ( Hoja de datos )

| Número de pieza | CS49400 | |

| Descripción | Multi-Standard Audio Decoder Family | |

| Fabricantes | Cirrus Logic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CS49400 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CS49400 Family DSP

Multi-Standard Audio Decoder

Features

Description

CS49300 Legacy Audio Decoder Support

Dolby Digital EXTM, Dolby Pro Logic IITM

DTS-ES 96/24TM, DTS 96/24TM, DTS-ES

Discrete 6.1TM, DTS-ES Matrix 6.1TM, DTS

Digital SurroundTM and DTS Virtual 5.1TM

MPEG-2: AAC Multichannel 5.1

MPEG Multichannel and Musicam

MPEG-1/2, Layer III (MP3)

DTS Neo:6TM, LOGIC7®, SRS Circle

Surround IITM

Cirrus Extra SurroundTM, Cirrus Original

Surround 6.1 (C.O.S. 6.1)TM

THX Surround EXTM, THX Ultra2 CinemaTM

12-Channel Serial Audio Inputs

Integrated 8K Byte Input Buffer

Powerful 32-bit Audio DSP

Customer Software Security Keys

Large On-chip X,Y, and Program RAM

Supports SDRAM, SRAM, FLASH

memories

16-channel PCM output

Dual S/PDIF Transmitters

SPI Serial, and Motorola® and Intel® Parallel

Host Control Interfaces

GPIO support for all common sub-circuits

The CS49400 Audio Decoder DSP is targeted as a market-

specific consumer entertainment processor for AV Receivers

and DVD Audio/Video Players. The device is constructed using

an enhanced version of the CS49300 Family DSP audio

decoder followed by a 32-bit programmable post-processor

DSP, which gives the designer the ability to add product

differentiation through the Cirrus FrameworkTM programming

structure and Framework module library. Dolby Digital Pro

Logic II, DTS Digital Surround, MPEG Multichannel, and Cirrus

Original Surround 6.1 PCM Effects Processor (capable of

generating such DSP audio modes as: Hall, Theater, Church)

are included in the cost of the CS49400 Family DSP. Additional

algorithms available through the Crystal WareTM Software

Licensing Program, give the designer the ability to further

deliver end-product differentiation.

The CS49400 contains sufficient on-chip SRAM to support

decoding all major audio decoding algorithms available today

including: AAC Multichannel, DTS 96/24, DTS-ES 96/24. The

CS49400 also supports a glueless SDRAM/SRAM for

increased all-channel delays. The SRAM interface also

supports connection to an external byte-wide EPROM for code

storage or Flash memory thus allowing products to be field-

upgradable as new audio algorithms are developed.

This chip, teamed with Crystal WareTM certified decoder

library, Cirrus digital interface products and mixed signal data

converters, enables the conception and design of next

generation digital entertainment products.

Ordering Information: See page 98

Compressed

Digital

Interface

Digital

Audio

Input

DSP AB

PLL Clock

Manager

Frame

Shifter

Input

Buffer

RAM

Multi-Standard

Audio Decoder

Parallel or Serial

Host Interface

SAI 0

SAI 1

SAI 2

SAI 3

DSP C

Serial

Audio

Interface

Programmable

32-Bit DSP

DSP

RAM

DSP

ROM

External Memory

Interface

Digital

Audio

Output

DAO 0

DAO 1

GPIO and I/O

Controller

Parallel or Serial

Host Interface

Preliminary Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

P.O. Box 17847, Austin, Texas 78760

(512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

©Copyright Cirrus Logic, Inc. 2002

(All Rights Reserved)

JUL ‘02

DS536PP2

1

1 page

Figure 42. Intel Mode, One-Byte Write Flow Diagram for DSPC .......................................................60

Figure 44. Intel Mode, One-Byte Read Flow Diagram for DSPC ......................................................61

Figure 43. Intel Mode, 32-bit (4-byte) Write Flow

Diagram for DSPC .............................................................................................................................62

Figure 45. Intel Mode, 32-Bit (4-Byte) Read Flow

Diagram for DSPC .............................................................................................................................63

Figure 46. Motorola Mode, One-Byte Write Flow

Diagram for DSPC .............................................................................................................................64

Figure 47. Motorola Mode, 32-bit (4-byte) Write Flow Diagram for DSPC ........................................65

Figure 48. Motorola Mode, One-Byte Read Flow

Diagram for DSPC .............................................................................................................................66

Figure 49. Motorola Mode, 32-Bit (4-Byte) Read Flow Diagram for DSPC .......................................67

Figure 50. Typical Parallel Host Mode Control Write Sequence Flow Diagram for DSPC ................68

Figure 51. Typical Parallel Host Mode Control Read Sequence Flow Diagram for DSPC ................69

Figure 52. Host Controlled Master Boot

(Downloading both a DSPAB Application Code and a DSPC Application Code) ..............................73

Figure 53. Host Boot Via DSPC .......................................................................................................76

Figure 54. Host Controlled Master Softreset .....................................................................................78

Figure 55. I2S Format ........................................................................................................................80

Figure 56. Left Justified Format (Rising Edge Valid SCLK) ...............................................................80

Figure 57. Pin Layout (144-Pin LQFP Package) ...............................................................................87

Figure 58. Pin Layout (100-Pin LQFP Package) ...............................................................................88

Figure 59. 144-Pin LQFP Package Drawing ...................................................................................100

5

5 Page

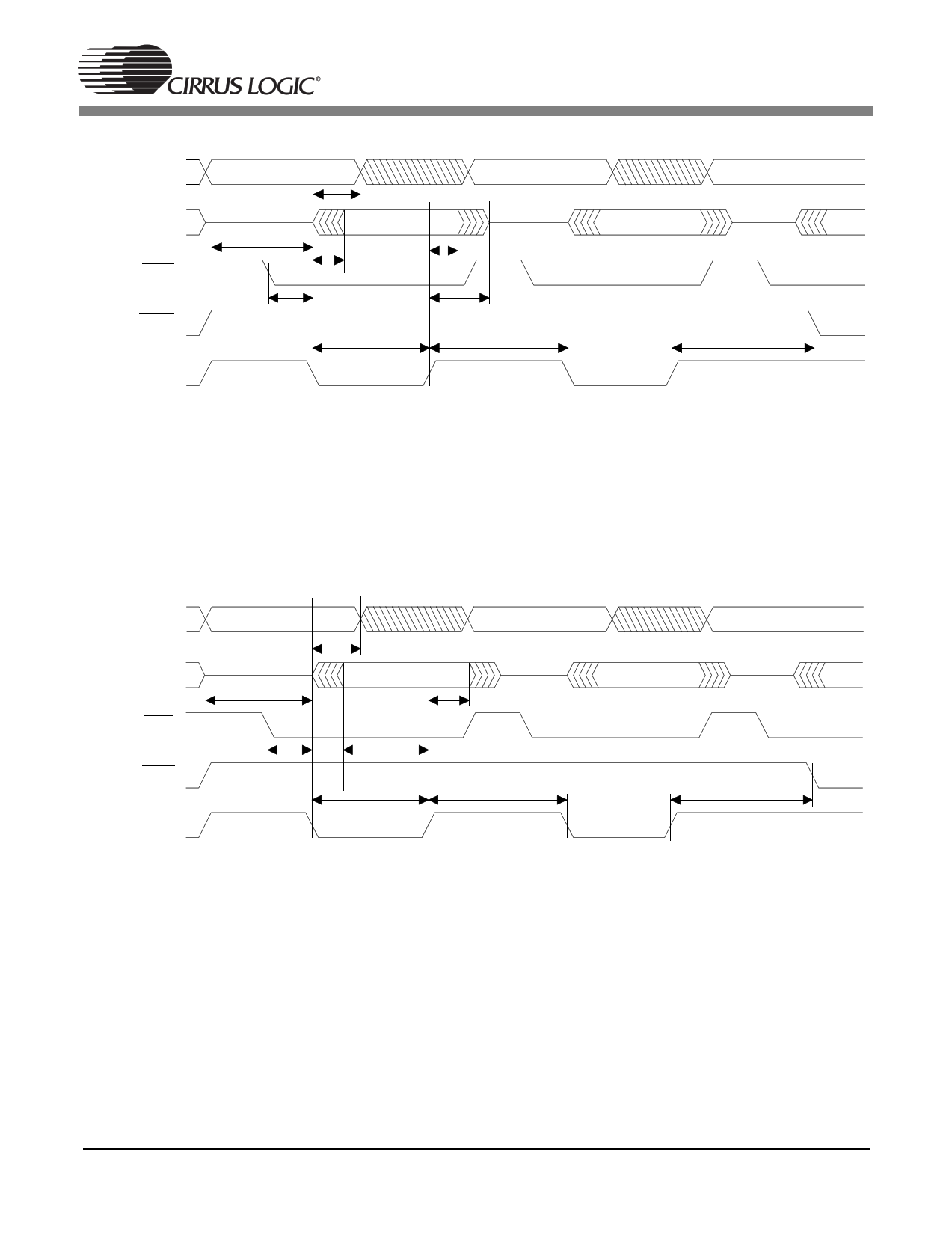

F A1:0

FD A T A7 :0

FCS

FWR

F RD

Tias

Ticdr

Tia h

Tidd

Tidhr

Tidis

Tirpw

Tird

T ird tw

Figure 3. Intel® Parallel Host Mode Slave Read Cycle for DSPAB

F A1:0

F DATA7:0

FCS

FRD

F WR

T ia s

Ticdw

Tiah

Tid hw

T iw p w

Tid su

Tiw d

Tiw tr d

Figure 4. Intel® Parallel Host Mode Slave Write Cycle for DSPAB

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CS49400.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CS49400 | Multi-Standard Audio Decoder Family | Cirrus Logic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |