|

|

PDF CS51033YN8 Data sheet ( Hoja de datos )

| Número de pieza | CS51033YN8 | |

| Descripción | Fast PFET Buck Controller Does Not Require Compensation | |

| Fabricantes | Cherry Semiconductor Corporation | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CS51033YN8 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

CS51033

Fast PFET Buck Controller

Does Not Require Compensation

Description

Features

The CS51033 is a switching con-

troller for use in DC-DC converters.

It can be used in the buck topology

with a minimum number of exter-

nal components. The CS51033 con-

sists of a 1.0A power driver for con-

trolling the gate of a discrete P-

channel transistor, fixed frequency

oscillator, short circuit protection

timer, programmable soft start, pre-

cision reference, fast output voltage

monitoring comparator, and output

stage driver logic with latch.

The high frequency oscillator

allows the use of small inductors

and output capacitors, minimizing

PC board area and systems cost.

The programmable soft start

reduces current surges at start up.

The short circuit protection timer

significantly reduces the PFET duty

cycle to approximately 1/30 of its

normal cycle during short circuit

conditions.

The CS51033 is available in 8L SO

and 8L PDIP plastic packages.

s 1A Totem Pole Output

Driver

s High Speed Oscillator

(700kHz max)

s No Stability

Compensation Required

s Lossless Short Circuit

Protection

s 2% Precision Reference

s Programmable Soft Start

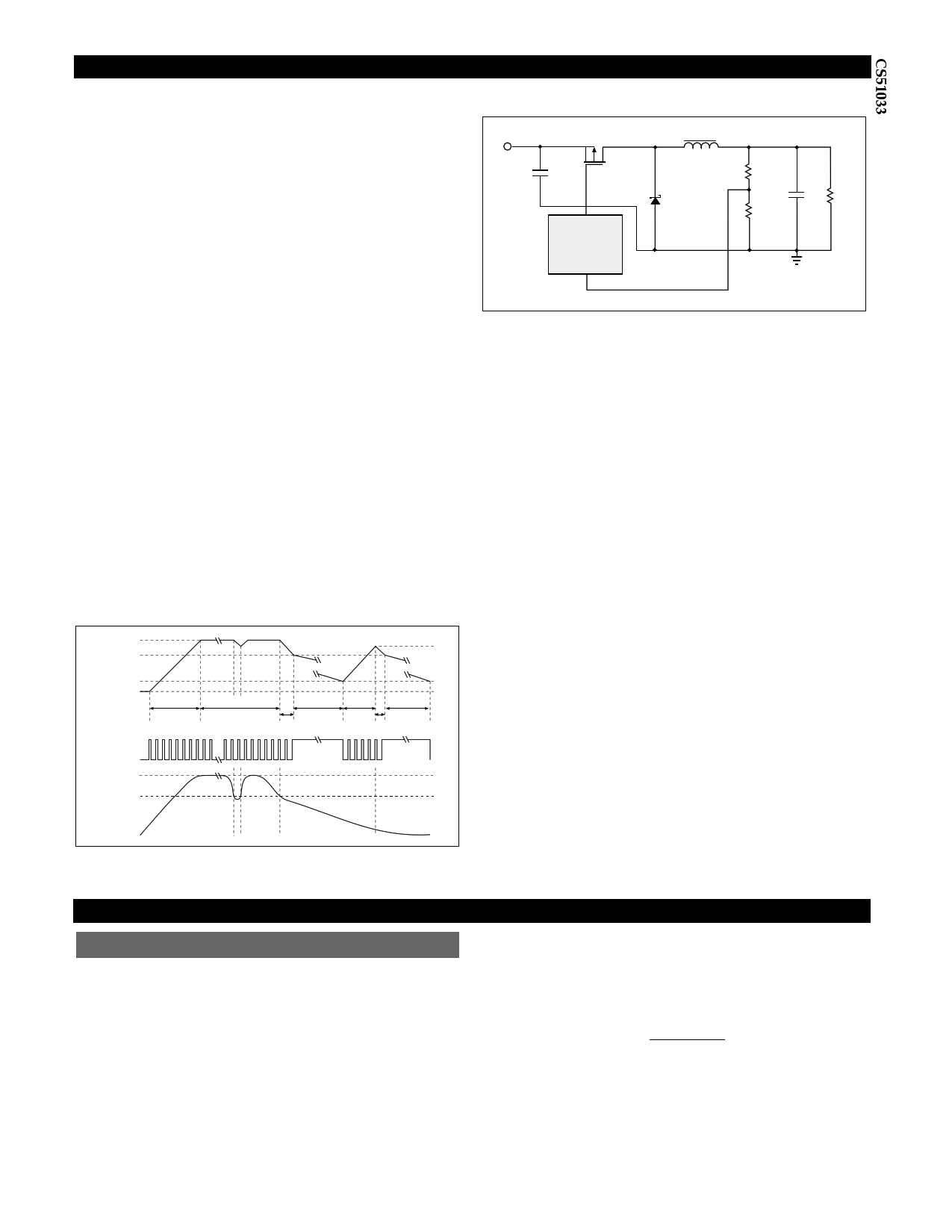

Typical Application Diagram

3.3VIN

CIN

100µF

RC D4

10Ω 1N5818

D2

1N4148

D3

1N4148

C1

0.1µF

C2 C3 COSC

1µF 100µF 150pF

VC

VCC

VGATE

U1

CS51033

COSC

VFB

RG

10Ω

0.01µF

IRF 7404

4.7µH

Gnd CS

PGnd

CS

0.1µF

100

.1µF

D1

1N5821

C0 C4

100µF 0.1µF

1.5VOUT

@3Amp

100µF

Gnd

NOTE: Capacitors C2, C3 and C4 are low ESR tantalum

caps used for noise reduction.

RA

1.5k

RB

300

Gnd

Package Options

8 Lead SO Narrow & PDIP

VGATE 1

PGnd

COSC

Gnd

VC

CS

VCC

VFB

Rev. 2/13/98

Cherry Semiconductor Corporation

2000 South County Trail, East Greenwich, RI 02818

Tel: (401)885-3600 Fax: (401)885-5786

Email: [email protected]

Web Site: www.cherry-semi.com

1 A ® Company

1 page

Circuit Description: continued

feedback to the VFB Comparator sets the GATE flip-flop dur-

ing COSC ’s charge cycle. Once the GATE flip-flop is set,

VGATE goes low and turns on the PFET. When VCS exceeds

2.4V, the CS charge sense comparator (A4) sets the VFB com-

parator reference to 1.25V completing the startup cycle.

Lossless Short Circuit Protection

The CS51033 has “Lossless” short circuit protection since

there is no current sense resistor required. When the voltage

at the CS pin (the fault timing capacitor voltage ) reaches

2.5V, the fault timing circuitry is enabled. During normal

operation the CS voltage is 2.6V. During a short circuit con-

dition or a transient condition, the output voltage moves

lower and the voltage at VFB drops. If VFB drops below

1.15V, the output of the fault comparator goes high and the

CS51033 goes into a fast discharge mode. The fault timing

capacitor, CS, discharges to 2.4V. If the VFB voltage is still

below 1.15V when the CS pin reaches 2.4V, a valid fault con-

dition has been detected. The slow discharge comparator

output goes high and enables gate G5 which sets the slow

discharge flip flop. The Vgate flip flop resets and the output

switch is turned off. The fault timing capacitor is slowly dis-

charged to 1.5V. The CS51033 then enters a normal startup

routine. If the fault is still present when the fault timing

capacitor voltage reaches 2.5V, the fast and slow discharge

cycles repeat as shown in figure 2.

If the VFB voltage is above 1.15V when CS reaches 2.4V a

fault condition is not detected, normal operation resumes

and CS charges back to 2.6V. This reduces the chance of

erroneously detecting a load transient as a fault condition.

2.6V

VCS 2.4V

1.5V

0V

VGATE

1.25V

1.15V

VFB

S1

TSTART

START

S2 S1

S2

S3

S2 2.5V

S3 S1

S3

S3

NORMAL OPERATION

td1

tFAULT

tRESTART td2

FAULT

tFAULT

0V

Figure 2. Voltage on start capacitor (VGS ), the gate (VGATE ), and in the

feedback loop (VFB), during startup, normal and fault conditions.

Buck Regulator Operation

VIN

CIN

Q1

Control

L

D1

R1

CO

R2

RLOAD

Feedback

Figure 3. Buck regulator block diagram.

A block diagram of a typical buck regulator is shown in

Figure 3. If we assume that the output transistor is initially

off, and the system is in discontinuous operation, the induc-

tor current IL is zero and the output voltage is at its nominal

value. The current drawn by the load is supplied by the out-

put capacitor CO . When the voltage across CO drops below

the threshold established by the feedback resistors R1 and

R2 and the reference voltage VREF, the power transistor Q1

switches on and current flows through the inductor to the

output. The inductor current rises at a rate determined by

(VIN-VOUT)/Load. The duty cycle (or “on” time) for the

CS51033 is limited to 80%. If the output voltage remains

higher than nominal during the entire COSC charge time, the

Q1 does not turn on, skipping the pulse.

CHARGE PUMP CIRCUIT

(Refer to the CS51033 Application Diagram)

An external charge pump circuit is necessary when the input

voltage is below 5V to ensure that there is sufficient gate

drive voltage for the external FET. When VIN is applied,

capacitors C1 and C2 will be charged to a diodes drop below

VIN via diodes D2 and D4, respectively. When the PFET

turns on, its drain voltage will be approximately equal to

VIN. Since the voltage across C1 can not change instanta-

neously, D2 is reverse biased and the anode voltage rises to

approximately 2*3.3V-VD2. C1 transfers some of its stored

charge C2 via D3. After several cycles there is sufficient gate

drive voltage.

Applications Information

Designing a Power Supply with the CS51033

Specifications

VIN = 3.3V +/- 10% (i.e. 3.63V max., 2.97V min.)

VOUT = 1.5V +/- 2%

IOUT = 0.3A to 3A

Output ripple voltage < 33mV.

FSW = 200kHz.

1) Duty Cycle Estimates

Since the maximum duty cycle, D, of the CS51033 is limited

to 80% min. it is best to estimate the duty cycle for the vari-

ous input conditions to see that the design will work over

the complete operating range.

The duty cycle for a buck regulator operating in a continu-

ous conduction mode is given by:

VOUT + VD

D = VIN - VSAT

Where VSAT is Rdson × IOUT Max.

In this case we can assume that VD = 0.6V and VSAT = 0.6V

so the equation reduces to:

5

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet CS51033YN8.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CS51033YN8 | Fast PFET Buck Controller Does Not Require Compensation | Cherry Semiconductor Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |