|

|

PDF CS51311GDR14 Data sheet ( Hoja de datos )

| Número de pieza | CS51311GDR14 | |

| Descripción | Synchronous CPU Buck Controller for 12V and 5V Applications | |

| Fabricantes | Cherry Semiconductor Corporation | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de CS51311GDR14 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

CS51311

Synchronous CPU Buck Controller

for 12V and 5V Applications

Description

Features

The CS51311 is a synchronous dual

NFET Buck Regulator Controller. It is

designed to power the core logic of

the latest high performance CPUs. It

uses the V2TM control method to

achieve the fastest possible transient

response and best overall regulation.

It incorporates many additional fea-

tures required to ensure the proper

operation and protection of the CPU

and Power system. The CS51311 pro-

vides the industry’s most highly inte-

grated solution, minimizing external

component count, total solution size,

and cost.

The CS51311 is specifically designed

to power Intel’s Pentium® II processor

and includes the following features:

5-bit DAC with 1.2% tolerance,

Power-Good output, over-current

hiccup mode protection, VCC monitor,

soft start, adaptive voltage position-

ing, adaptive FET non-overlap time,

and remote sense. The CS51311 will

operate over an 8.4V to 14V range

and is available in 14 lead narrow

body surface mount package.

Application Diagram

+12V

+5V

s Synchronous Switching

Regulator Controller for

CPU VCORE

s Dual N-Channel MOSFET

Synchronous Buck Design

s V2TM Control Topology

s 200ns Transient Loop

Response

s 5-bit DAC with 1.2% Tolerance

s Hiccup Mode Overcurrent

Protection

s 40ns Gate Rise and Fall Times

(3.3nF load)

s 65ns Adaptive FET

Non-overlap Time

s Adaptive Voltage Positioning

s Power-Good Output Monitors

Regulator Output

s VCC Monitor Provides Under

Voltage Lockout

s Enable Through use of the

COMP pin

680pF

0.01

100Ω µF

0.1

µF

VID0

VID1

VID2

VID3

VID4

1µF

10K

COFF

COMP

VCC

GATE(H)

GATE(L)

FS70VSJ-03

FS70VSJ-03

1200µF/10V

x3

1.2µH 3.3mΩ

VFB

VOUT

Gnd PWRGD

0.1µF

510Ω

510Ω

PWRGD

V2 is a trademark of Switch Power, Inc.

Pentium is a registered trademark of Intel Corporation.

Rev. 3/11/99

1

VCC(CORE)

2.0V@19A

1200µF/10V

x5

Package Options

14 Lead SO Narrow

VID0 1

VID1

VID2

VID3

VID4

VFB

VOUT

COMP

COFF

PWRGD

GATE(L)

Gnd

GATE(H)

VCC

Cherry Semiconductor Corporation

2000 South County Trail, East Greenwich, RI 02818

Tel: (401)885-3600 Fax: (401)885-5786

Email: [email protected]

Web Site: www.cherry-semi.com

A ® Company

1 page

Electrical Characteristics: 0˚C < TA < 70˚C; 0˚C < TJ < 125˚C; 9V < VCC < 14V;

2.0V DAC Code (VID4 = VID3 =VID2 = VID1 = 0, VID0 = 1), CGATE(H) = CGATE(L) = 3.3nF, COFF = 390pF; Unless otherwise stated.

PARAMETER

TEST CONDITIONS

s General Electrical Specifications

VCC Monitor Start Threshold

VCC Monitor Stop Threshold

Hysteresis

Start - Stop

VCC Supply Current

No Load on GATE(H), GATE(L)

MIN

7.9

7.6

0.15

TYP

8.4

8.1

0.30

12

MAX

8.9

8.6

0.60

20

UNIT

V

V

V

mA

Note 1: The IC power dissipation in a typical application with VCC = 12V, switching frequency fSW = 250kHz, 50nc

MOSFETs and RθJA = 115°C/W yields an operating junction temperature rise of approximately 52°C, and a junction tem-

perature of 77°C with an ambient temperature of 25°C.

Note 2: Guaranteed by design, not 100% tested in production.

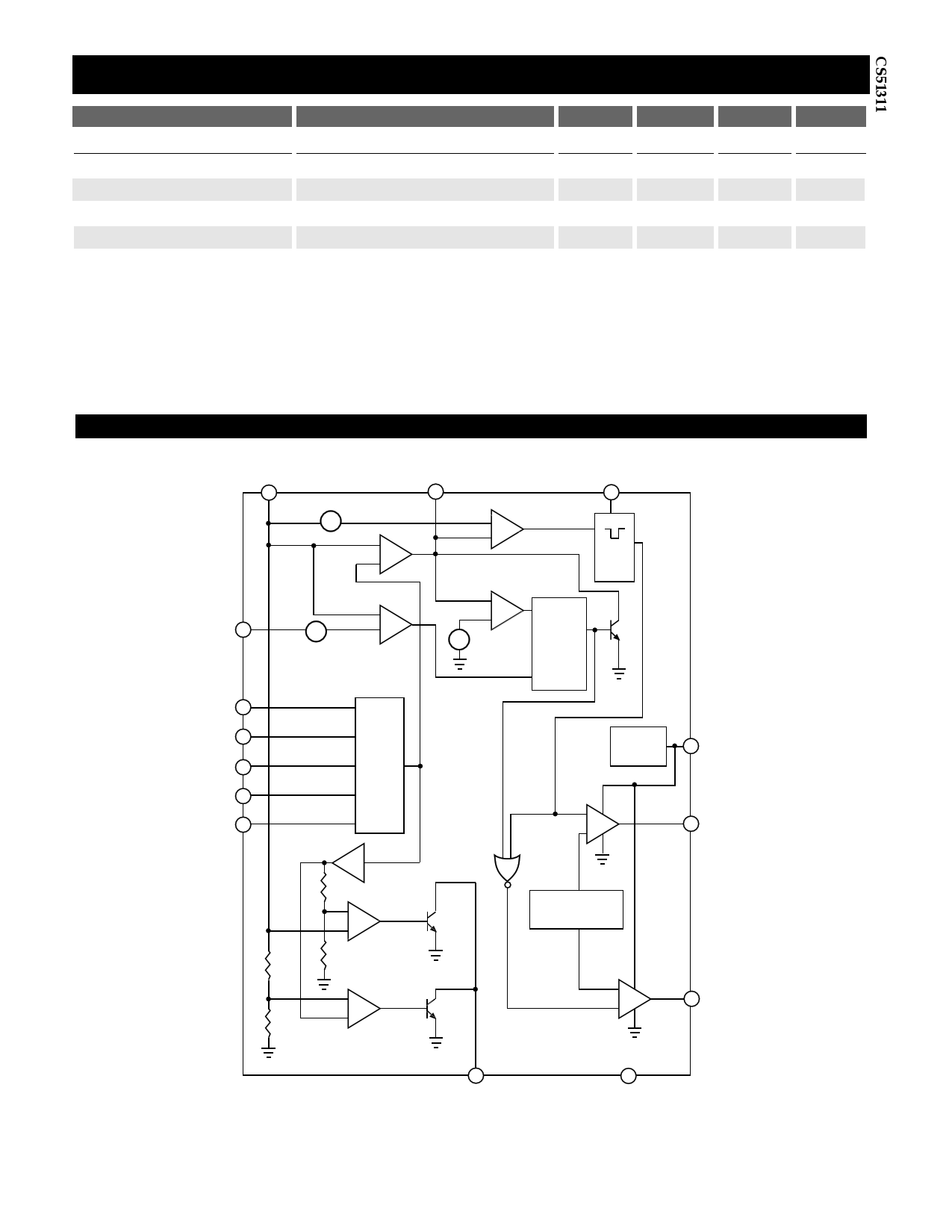

Block Diagram

VOUT

VID0

VID1

VID2

VID3

VID4

VFB

1.1V

-

COMP

EA

PWM COMP

+

-

CURRENT LIMIT

86mV

-

+

-

DISCHARGE

COMP

R

+- 0.25V

Q

FAULT

LATCH

S

COFF

OFF

TIME

DAC

UVLO

VCC

GATE(H)

NONOVERLAP

+ LOGIC

-

+ GATE(L)

-

PWRGD

Gnd

5

5 Page

Application Information: continued

Number of capacitors =

ESRCAP

ESRMAX

,

Duty Cycle = D =

VOUT + (VHFET + VL + VDROOP)

VIN + VLFET − VHFET − VL

,

where

ESRCAP = maximum ESR per capacitor (specified in

manufacturer’s data sheet);

ESRMAX = maximum allowable ESR.

The actual output voltage deviation due to ESR can then be

verified and compared to the value assigned by the design-

er:

∆VESR = ∆IOUT × ESRMAX

Similarly, the maximum allowable ESL is calculated from

the following formula:

ESLMAX =

∆VESL × ∆t

∆I

,

where

∆I/∆T = load current slew rate (as high as 20A/µs);

∆VESL = change in output voltage due to ESL.

The actual maximum allowable ESL can be determined by

using the equation:

ESLMAX =

ESLCAP

Number of output capacitors

,

where ESLCAP = maximum ESL per capacitor (it is estimat-

ed that a 10 × 12mm Aluminum Electrolytic capacitor has

approximately 4nH of package inductance).

The actual output voltage deviation due to the actual maxi-

mum ESL can then be verified:

where

VOUT = buck regulator output voltage;

VHFET = high side FET voltage drop due to RDS(ON);

VL = output inductor voltage drop due to inductor wire

DC resistance;

VDROOP = droop (current sense) resistor voltage drop;

VIN = buck regulator input voltage;

VLFET = low side FET voltage drop due to RDS(ON).

Step3a: Calculation of Switch On-Time

The switch On-Time (time during which the switching

MOSFET in a synchronous buck topology is conducting) is

determined by:

TON =

Duty Cycle

FSW

,

where FSW = regulator switching frequency selected by the

designer.

Higher operating frequencies allow the use of smaller

inductor and capacitor values. Nevertheless, it is common

to select lower frequency operation because a higher fre-

quency results in lower efficiency due to MOSFET gate

charge losses. Additionally, the use of smaller inductors at

higher frequencies results in higher ripple current, higher

output voltage ripple, and lower efficiency at light load

currents.

Step 3b: Calculation of Switch Off-Time

The switch Off-Time (time during which the switching

MOSFET is not conducting) can be determined by:

∆VESL =

ESLMAX × ∆I

∆t

.

TOFF =

1

FSW

− TON,

The designer now must determine the change in output

voltage due to output capacitor discharge during the tran-

sient:

∆VCAP =

∆I × ∆tTR

COUT

,

where

∆tTR = the output voltage transient response time

(assigned by the designer);

∆VCAP = output voltage deviation due to output capaci-

tor discharge;

∆I = Load step.

The total change in output voltage as a result of a load cur-

rent transient can be verified by the following formula:

∆VOUT = ∆VESR + ∆VESL + ∆VCAP

Step 3: Selection of the Duty Cycle,

Switching Frequency, Switch On-Time (TON)

and Switch Off-Time (TOFF)

The duty cycle of a buck converter (including parasitic

losses) is given by the formula:

The COFF capacitor value has to be selected in order to set

the Off-Time, TOFF, above:

COFF =

Period × (1 − D) ,

3980

where

3980 is a characteristic factor of the CS51311;

D = Duty Cycle.

Step 4: Selection of the Output Inductor

The inductor should be selected based on its inductance,

current capability, and DC resistance. Increasing the induc-

tor value will decrease output voltage ripple, but degrade

transient response. There are many factors to consider in

selecting the inductor including cost, efficiency, EMI and

ease of manufacture. The inductor must be able to handle

the peak current at the switching frequency without satu-

rating, and the copper resistance in the winding should be

kept as low as possible to minimize resistive power loss.

There are a variety of materials and types of magnetic

cores that could be used for this application. Among them

are ferrites, molypermalloy cores (MPP), amorphous and

powdered iron cores. Powdered iron cores are very com-

monly used. Powdered iron cores are very suitable due to

11

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet CS51311GDR14.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CS51311GDR14 | Synchronous CPU Buck Controller for 12V and 5V Applications | Cherry Semiconductor Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |