|

|

PDF CT2553-FP Data sheet ( Hoja de datos )

| Número de pieza | CT2553-FP | |

| Descripción | CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 | |

| Fabricantes | Aeroflex Circuit Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de CT2553-FP (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

CT2553 / 2554 / 2555 / 2556

Advanced Integrated MUX (AIM) Hybrid

FOR MIL-STD-1553

Features

I Second Source Compatible to the BUS-61553

I Complete Integrated MUX Including:

• Low Power Dual Transceiver

• BC/RTU/MT Protocol

• 8K x 16 Shared Ram

• Interrupt Logic

I Compatible with MIL-STD- 1750 and other Standard CPUs

I DIP or Flatpack Hybrid

I Minimizes CPU Overhead

I Provides Memory Mapped 1553 Interface

I On-Line & Off-Line Self-Test

I PCs Development Tools Available

I SEAFAC Tested

I MIL-PRF-38534 compliant circuits available

I DESC SMD #5962–88692 Pending

I Packaging – Hermetic Metal

• 78 Pin, 2.1" x 1.87" x .25" Plug-In type package

• 82 Lead, 2.2" x 1.61" x .18" Flat package

CIRCUIT TECHNOLOGY

www.aeroflex.com

FLEX LA

ISO

9001

CE R T I F I E D

General Description

Aeroflex’s CT2553 Advanced Integrated Mux (AIM) Hybrid is a complete MIL-STD-1553 Bus

Controller (BC), Remote Terminal Unit (RTU), and Bus Monitor (MT) device. Packaged in a single

78 pin DIP package, the CT2553 contains dual low-power transceivers, complete BC/RTU/MT

protocol logic, a MIL-STD-1553-to-host interface unit and an 8K x 16 RAM.

Using an industry standard dual transceiver and standard status and control signals, the CT2553

simplifies system integration at both the MIL-STD-1553 and host processor interface levels.

All 1553 operations are controlled through the CPU access to the shared 8K x 16 RAM. To ensure

maximum design flexibility, memory control lines are provided for attaching external RAM to the

CT2553 Address and Data Buses and for disabling internal memory; the total combined memory

space can be expanded to 64K x16. All 1553 transfers are entirely memory-mapped; thus the CPU

interface requires minimal hardware and/or software support.

The CT2553 operates over the full military -55°C to +125°C temperature range. Available screened

to MIL-STD883, the CT2553 is ideal for demanding military and industrial microprocessor to 1553

interface applications. See "Ordering Information" (last sheet) for CT2554, CT2555 & CT2556.

eroflex Circuit Technology – Data Bus Modules For The Future © SCDCT2553 REV B 8/6/99

1 page

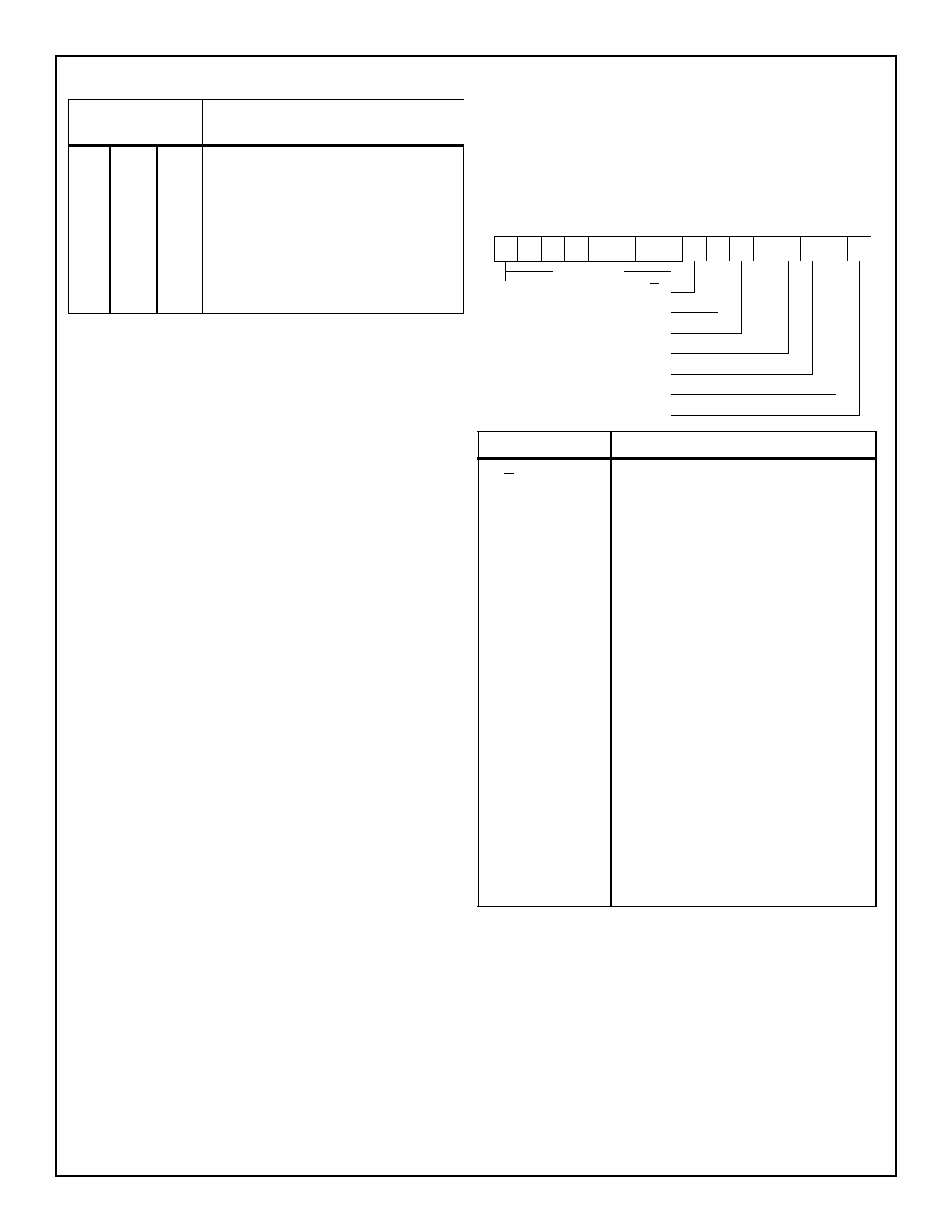

ROM

RAM

I/O

CPU

ADDRESS

DECODER

HOST PROCESSOR

RD/WR

(DIR)

DATA 16

D0 - D15

RD/WR

36 51

RTADP

RTADDRESS

(OE) (54LS245)

IOEN

MEMENA-OUT

(SEE NOTE 1)

(OE) (54LS244)

ADDRESS

A0 - A12

MEMENA-IN

13

POR

MSTRCLR

(SEE NOTE 2)

SELECT

MEM/REG

(54LS04)

STRBD

8

73 40 TX/RX-A 1

31 2

78 TX/RX-A

3

69

7

6

5

4

BUS-25679

CT2553

8

TX/RX-B

20

1

7

71 2 6

59 TX/RX-B

3

74

5

4

BUS-25679

33

3 +5V

34 2 -15V

+

–

+

–

READYD

INT

75

72

MEMOE

16MHz

CLOCK

30

32

12 ILLCMD

+5V

13 SA/MC-0

15 SA/MC-1

52 SA/MC-2

54 SA/MC-3

53 SA/MC-4

57 T/R

XX BCSTRCV

17 LMC

ILLEGALIZATION

PROM

(OPTIONAL)

1553 INTERFACE

Aeroflex Circuit Technology

Figure 2 – CT2553 Example Interconnection

5 SCDCT2553 REV B 8/6/99 Plainview NY (516) 694-6700

5 Page

Table 2 – CT2553 Register Address Definition

Address Bits

A2 A1 A0

Definition

0 0 0 R/W Interrupt Mask Register

0 0 1 R/W Configuration Register

0 1 0 – Not Used

0 1 1 W Start/Reset Register

1 0 0 R/W * External Register

1 0 1 R/W * External Register

1 1 0 R/W * External Register

1 1 1 R/W * External Register

* Note: R/W (read/write) capability is dependent on the user's

decoding implementation (See Figure 9).

CONTENTION HANDLING

The CT2553 arbitrates shared RAM (and control

register) accesses between the host CPU and the

internal 1553 protocol logic.

If the host attempts to access the RAM while an

internal 1553 memory cycle is in progress, the

CT1553 will delay the CPU's memory cycle by

inserting wait states via the READYD control

signal until the cycle has been completed. The

maximum delay is 1.8µs.

If the internal 1553 protocol logic attempts to

access the RAM while the host CPU has control of

the memory, the internal 1553 logic will wait until

the host CPU cycle has been completed. To

ensure the integrity of 1553 data transfers, the

host CPU must complete its memory cycle within

1.5µs (See Figures 28-32).

SELF TEST

The CT2553 has two self-test modes: the

automatic, continuous On-Line test and the

software-initiated Off-Line test. In both tests the

Loop Test Fail bit within the Block Status Word will

be set to a logic 1 if a failure is detected.

ON-LINE TEST. The On-Line test occurs in BC

and RTU modes during transmission of each

message onto the 1553 bus. This test wraps

around the last word transmitted, exercising the

1553 protocol logic through the 1553 transceivers.

While operating as a BC, the last word transmitted

is received, decoded, and written back into

memory location immediately following the last

word within the message block. The host CPU can

read and compare this Loop Back Word with the

last word of the message Data Block; these two

words should be identical. This insures data

integrity between the CPU and the CT2553.

While in the RTU mode, the internal 1553 Status

Word will be updated to reflect the result of the self

test. The Status Word's Terminal Flag bit will be

set to a logic 1 if a fault was indicated by the

wrap-around, self-test.

OFF-LINE TEST. The software-initiated Off-Line

test can be executed only when the CT2553 is

configured as a BC. Set the Wrap-Around Test bit

within the BC Control Word to a logic 1 and initiate

any standard message transfer. This inhibits the

1553 transceivers and initiates the standard

wrap-around test (i.e., internal 1553 encoder

output is fed back into the decoder - the word is

then written into memory). See BC Operation and

Figure 14, BC Control Word for more details.

15 8 7 6 5 4 3 2 1 0

NOT USED

BUS CHANNEL A/B

OFF-LINE SELF TEST

MASK BROADCAST

NOT USED

MODE CODE

BROADCAST

RT-RT

BIT NAME

DEFINITION

BUS CHANNEL Determines whether message will be

A/B transmitted on 1553 Bus A or Bus B.

Logic 1 = A, logic 0 = B.

INITIATE

OFF-LINE SELF

TEST

Logic 1 performs internal off-line

transmit/receive test. The last word

of the message is looped back

through the decoder and placed in

RAM. See Self Test paragraph.

MASK

BROADCAST (1)

When logic 1, prevents Broadcast

RCVD bit of the 1553 Status Word

response from signalling a status

error as a result of a Broadcast

command. (A FORMAT error will be

generated if the BROADCAST bit is

not set on the RTU’s Status Word.)

MODE CODE

When logic 1, the message is treated

as a Mode Code. (The Command

Word - Word Count field indicates

Mode Code type.)

BROADCAST

When logic 1, indicates that the

message is a Broadcast Command.

(No Status Word is expected.)

RT-RT

When logic 1, the message is treated

as an RT-RT transfer. (The next two

words are Command Words.) Both

Status Word responses are

validated.

Note:

1. MASK BROADCAST XOR BROADCAST BIT in Status Word =

STATUS SET ERROR.

2. When the BC expects the BROADCAST bit set in the Status Word,

a logic 1 will mask the Status Interrupt Error flag.

Figure 14 – BC CONTROL WORD

RESET

The CT2553 can be reset by pulsing the

MSTRCLR (pin 71) low or by writing to the

Start/Reset register. After a reset condition has

occurred, the Configuration, Interrupt, and

(internal) Block Status word register outputs are

forced to a logic 0.

Aeroflex Circuit Technology

11 SCDCT2553 REV B 8/6/99 Plainview NY (516) 694-6700

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet CT2553-FP.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| CT2553-FP | CT2553 / 2554 / 2555 / 2556 Advanced Integrated MUX (AIM) Hybrid FOR MIL-STD-1553 | Aeroflex Circuit Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |