|

|

PDF HSP50110 Data sheet ( Hoja de datos )

| Número de pieza | HSP50110 | |

| Descripción | Digital Quadrature Tuner | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HSP50110 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

Data Sheet

HSP50110

January 1999 File Number 3651.4

Digital Quadrature Tuner

The Digital Quadrature Tuner (DQT) provides many of the

functions required for digital demodulation. These functions

include carrier LO generation and mixing, baseband

sampling, programmable bandwidth filtering, baseband AGC,

and IF AGC error detection. Serial control inputs are provided

which can be used to interface with external symbol and

carrier tracking loops. These elements make the DQT ideal

for demodulator applications with multiple operational modes

or data rates. The DQT may be used with HSP50210 Digital

Costas Loop to function as a demodulator for BPSK, QPSK,

8-PSK OQPSK, FSK, FM, and AM signals.

The DQT processes a real or complex input digitized at rates

up to 52 MSPS. The channel of interest is shifted to DC by a

complex multiplication with the internal LO. The quadrature

LO is generated by a numerically controlled oscillator (NCO)

with a tuning resolution of 0.012Hz at a 52MHz sample rate.

The output of the complex multiplier is gain corrected and fed

into identical low pass FIR filters. Each filter is comprised of a

decimating low pass filter followed by an optional

compensation filter. The decimating low pass filter is a 3

stage Cascaded-Integrator-Comb (CIC) filter. The CIC filter

can be configured as an integrate and dump filter or a third

order CIC filter with a (sin(X)/X)3 response. Compensation

filters are provided to flatten the (sin(X)/X)N response of the

CIC. If none of the filtering options are desired, they may be

bypassed. The filter bandwidth is set by the decimation rate of

the CIC filter. The decimation rate may be fixed or adjusted

dynamically by a symbol tracking loop to synchronize the

output samples to symbol boundaries. The decimation rate

may range from 1-4096. An internal AGC loop is provided to

maintain the output magnitude at a desired level. Also, an

input level detector can be used to supply error signal for an

external IF AGC loop closed around the A/D.

The DQT output is provided in either serial or parallel formats

to support interfacing with a variety DSP processors or digital

filter components. This device is configurable over a general

purpose 8-bit parallel bidirectional microprocessor control bus.

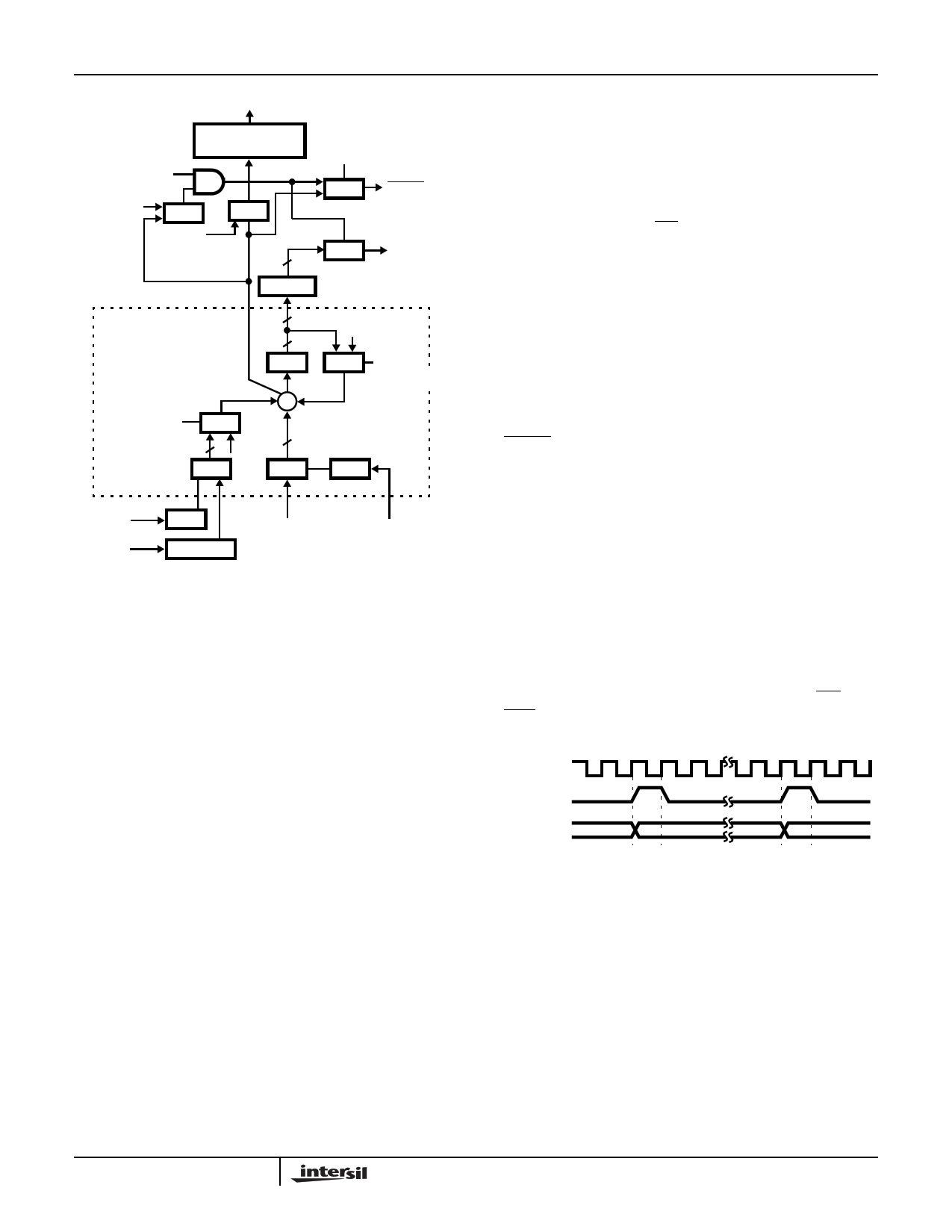

Block Diagram

Features

• Input Sample Rates to 52 MSPS

• Internal AGC Loop for Output Level Stability

• Parallel or Serial Output Data Formats

• 10-Bit Real or Complex Inputs

• Bidirectional 8-Bit Microprocessor Interface

• Frequency Selectivity <0.013Hz

• Low Pass Filter Configurable as Three Stage Cascaded-

Integrator-Comb (CIC), Integrate and Dump, or Bypass

• Fixed Decimation from 1-4096, or Adjusted by NCO

Synchronization with Baseband Waveforms

• Input Level Detection for External IF AGC Loop

• Designed to Operate with HSP50210 Digital Costas Loop

• 84 Lead PLCC

Applications

• Satellite Receivers and Modems

• Complex Upconversion/Modulation

• Tuner for Digital Demodulators

• Digital PLL’s

• Related Products: HSP50210 Digital Costas Loop;

A/D Products HI5703, HI5746, HI5766

• HSP50110/210EVAL Digital Demod Evaluation Board

Ordering Information

PART NUMBER

HSP50110JC-52

HSP50110JI-52

TEMP.

RANGE (oC) PACKAGE

0 to 70 84 Ld PLCC

-40 to 85 84 Ld PLCC

PKG. NO.

N84.1.15

N84.1.15

10

REAL OR COMPLEX

INPUT DATA

10

IF AGC

CONTROL

CONTROL/STATUS

BUS

COMPLEX

MULTIPLIER GCA

LOOP

FILTER

LOW PASS FIR

FILTER

90o

0o NCO

LEVEL

DETECT

8

GCA

LOW PASS FIR

FILTER

PROGRAMMABLE

CONTROL

INTERFACE

LEVEL

DETECT

10

I DATA

DUMP

RE-SAMPLING

NCO

CARRIER

TRACKING CONTROL

10

Q DATA

SAMPLE STROBE

SAMPLE RATE

CONTROL

3-229

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

1 page

HSP50110

processing elements so that they are enabled once for each

time ENI is sampled low. This mode minimizes the

processing pipeline latency, and the latency of the part’s

serial interfaces while conserving power. Note: the

effective input sample rate to the internal processing

elements is equal to the frequency with which ENI is

asserted “low”.

In Interpolated Input Mode, the ENI input is used to insert

zeroes between the input data samples. This process

increases the input sample rate to the processing elements

which improves the time resolution of the processing chain.

When ENI is sampled “high” by CLK, a zero is input into the

processing pipeline. When ENI is sampled “low” the input

data is fed into the pipeline. Note: Due to the nature of the

rate change operation, consideration must be given to

the scaling and interpolation filtering required for a

particular rate change factor.

In either the Gated or Interpolated Input Mode, the

Synthesizer NCO is gated by the ENI input. This only allows

clocking of the NCO when external samples are input to the

processing pipeline. As a result, the NCO frequency must be

set relative to the input sample rate, not the CLK rate (see

Synthesizer/Mixer Section). NOTE: Only fixed

interpolation rates should be used when operating the

part in Interpolated Mode at the Input Controller.

Input Level Detector

The Input Level Detector generates a one-bit error signal for

an external IF AGC filter and amp. The error signal is

generated by comparing the magnitude of the input samples

to a user programmable threshold. The HI/LO pin is then

driven “high” or “low” depending the relationship of its

magnitude to the threshold. The sense of the HI/LO pin is

programmable so that a magnitude exceeding the threshold

can either be represented as a “high” or “low” logic state.

The threshold and the sense of the HI/LO pin are configured

by loading the appropriate control registers via the

Microprocessor Interface (see Tables 8 and 12).

The high/low outputs can be integrated by an external loop

filter to close an AGC loop. Using this method the gain of the

loop forces the median magnitude of the input samples to

the threshold. When the magnitude of half the samples are

above the threshold and half are below, the error signal is

integrated to zero by the loop filter.

The algorithm for determining the magnitude of the complex

input is given by:

Mag(I,Q) = |I| + .375 x |Q| if |I| > |Q|

(EQ. 1)

or:

Mag(I,Q) = |Q| + .375 x |I| if |Q| > |I|,

(EQ. 2)

Using this algorithm, the magnitude of complex inputs can

be estimated with an error of <0.55dB or approximately

6.5%. For real inputs, the magnitude detector reduces to a

an absolute value detector with negligible error.

Note: an external AGC loop using the Input Level

Detector may go unstable for a real sine wave input

whose frequency is exactly one quarter of the sample

rate (FS/4). The Level Detector responds to such an

input by producing a square wave output with a 50%

duty cycle for a wide range of thresholds. This square

wave integrates to zero, indicating no error for a range

of input signal amplitudes.

Synthesizer/Mixer

The Synthesizer/Mixer spectrally shifts the input signal of

interest to DC for subsequent baseband filtering. This

function is performed by using a complex multiplier to

multiply the input with the output of a quadrature numerically

controlled oscillator (NCO). The multiplier operation is:

IOUT = IIN x cos (ωc) - QIN x sin (ωc)

(EQ. 3)

QOUT = IIN x sin (ωc) + QIN x cos (ωc)

(EQ. 4)

The complex multiplier output is rounded to 12 bits. For real

inputs this operation is similar to that performed by a

quadrature downconverter. For complex inputs, the

Synthesizer/Mixer functions as a single-sideband or image

reject mixer which shifts the frequency of the complex

samples without generating images.

TO COMPLEX MULTIPLIER

COS

SIN

10 10

†Controlled via

microprocessor interface.

REG

REG

SIN/COS

ROM

PH0-1

R

E

G

2

11 8 R PHASE OFFSET †

+E

G

LOTP

REG

REG

0

MUX LOAD †

COF

ENABLE †

+

MUX

32

COF

0

REG

32

CF

REG

PHASE

ACCUMULATOR

COFSYNC

SYNC

COF

SHIFT REG

CFLD

R

E

G

SYNC

CARRIER LOAD CARRIER

FREQUENCY † FREQUENCY †

FIGURE 2. SYNTHESIZER NCO

3-233

5 Page

HSP50110

TO DECIMATING FILTERS

PROGRAMMABLE

DIVIDER

SAMPLE PHASE

OUT CONTROL †

DATARDY

SYNC

MUX

MODE †

REG

CLK

32-BIT ADDER

CARRY OUTPUT

5

REG

SHIFTER

SSTRB

SPH0-4

RE-SAMPLER

NCO

8

32

REG

+

SOF ENABLE †

MUX

32 0

32

SOF REG SCF REG

0

MUX

LOAD

RESAMPLER

NCO †

SYNC

SOFSYNC

SOF

SYNC

SHIFT REG

SAMPLER

CENTER

FREQUENCY †

† Controlled via microprocessor interface.

FIGURE 13. RE-SAMPLER

LOAD

ON CF

WRITE

The calculation of the decimation factor depends on whether

the output sample rate is fixed or adjusted dynamically. For a

fixed sample rate, the decimation factor is equal to the divisor

loaded into the programmable divider. For example, if the

divider is configured with a divisor of 8, the decimation factor

is 8 (i.e., the output data rate is Fs/8). If the decimation factor

is adjusted dynamically, it is a function of both the

programmable divisor and the frequency of carry outs from

the Re-Sampler NCO (FCO) as given by:

Decimation Factor =

(Programmable Divisor) x Fs/FCO

(EQ. 10)

For example, if the programmable divisor is 8 and Fs/FCO =

40, the decimation factor would be 320.

NOTE: The CIC filter architecture only supports

decimation factors up to 4096.

The phase accumulator in the Re-Sampler NCO generates

the carry outs used to clock the programmable divider. The

frequency at which carry outs are generated (FCO) is

determined by the values loaded into the Sampler Center

Frequency (SCF) and Sampler Offset Frequency (SOF)

Registers. The relationship between the values loaded into

these registers and the frequency of the carry outs is given by:

FCO = Fs x (SCF + SOF)/232

(EQ. 11)

where Fs is the input sample rate of the Low Pass Filter

Section, SCF is the 32-bit value loaded into the Sampler

Center Frequency Register, and SOF is the 32-bit value

loaded into the Sample Offset Frequency Register. The SCF

Register is loaded through the Microprocessor Interface (see

Microprocessor Interface Section), and the SOF Register is

loaded serially via the SOF and SOFSYNC inputs (see Serial

Input Section). The sample rate Fs is a function of the Input

Controller Mode. If the Controller is in Gated Input Mode, Fs is

the frequency with which ENI is asserted. In Interpolated Input

Mode, Fs is the CLK frequency (see Input Controller Section).

The carry out and 5 of the most significant 8 bits of the

NCO’s phase accumulator are output to control a resampling

filter such as the HSP43168. The resampling filter can be

used to provide finer time (symbol phase) resolution than

can be achieved by the sampling clock alone. This may be

needed to improve transmit/receive timing or better, align a

matched filter’s impulse response with the symbol

boundaries of a baseband waveform at high symbol rates.

The carry out of the NCO’s phase accumulator is output on

SSTRB, and a window of 5 of the 8 most significant 8 bits of

the Phase Accumulator are output on SPH0-4.

Output Formatter

The Output Formatter supports either Word Parallel or Bit

Serial output modes. The output can be chosen to have a

two’s complement or offset binary format. The configuration

is selected by loading the I/O Formatting/Control Register

(see Table 10).

In parallel output mode, the in-phase and quadrature

samples are output simultaneously at rates up to the

maximum CLK. The DATARDY output is asserted on the first

CLK cycle that new data is available on IOUT0-9 and

QOUT0-9 as shown in Figure 14. Output enables (OEI,

OEQ) are provided to individually three-state IOUT0-9 and

QOUT0-9 for output multiplexing.

CLK

DATARDY

IOUT9-0/

QOUT9-0

NOTE: DATARDY may be programmed active high or low.

FIGURE 14. PARALLEL OUTPUT TIMING

When bit serial output is chosen, two serial output modes are

provided, Simultaneous I/Q Mode and I Followed by Q Mode.

In Simultaneous I/Q Mode, the 10-bit I and Q samples are

output simultaneously on IOUT0 and QOUT0 as shown in

Figure 15. In I Followed by Q Mode, both samples are output

on IOUT0 with I samples followed by Q samples as shown in

Figure 16. In this mode, the I and Q samples are packed into

separate 16-bit serial words (10 data bits + 6 zero bits). The

10 data bits are the 10 MSBs of the serial word, and the I

sample is differentiated from the Q sample by a 1 in the LSB

position of the 16-bit data word. A continuous serial output

clock is provided on IOUT9 which is derived by dividing the

3-239

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet HSP50110.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HSP50110 | Digital Quadrature Tuner | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |