|

|

PDF HTRC11001T Data sheet ( Hoja de datos )

| Número de pieza | HTRC11001T | |

| Descripción | HITAG reader chip | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HTRC11001T (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

HTRC11001T

HITAG reader chip

Product specification

Supersedes data of 1999 Jan 01

File under Integrated Circuits, IC11

2001 Nov 23

1 page

Philips Semiconductors

HITAG reader chip

Product specification

HTRC11001T

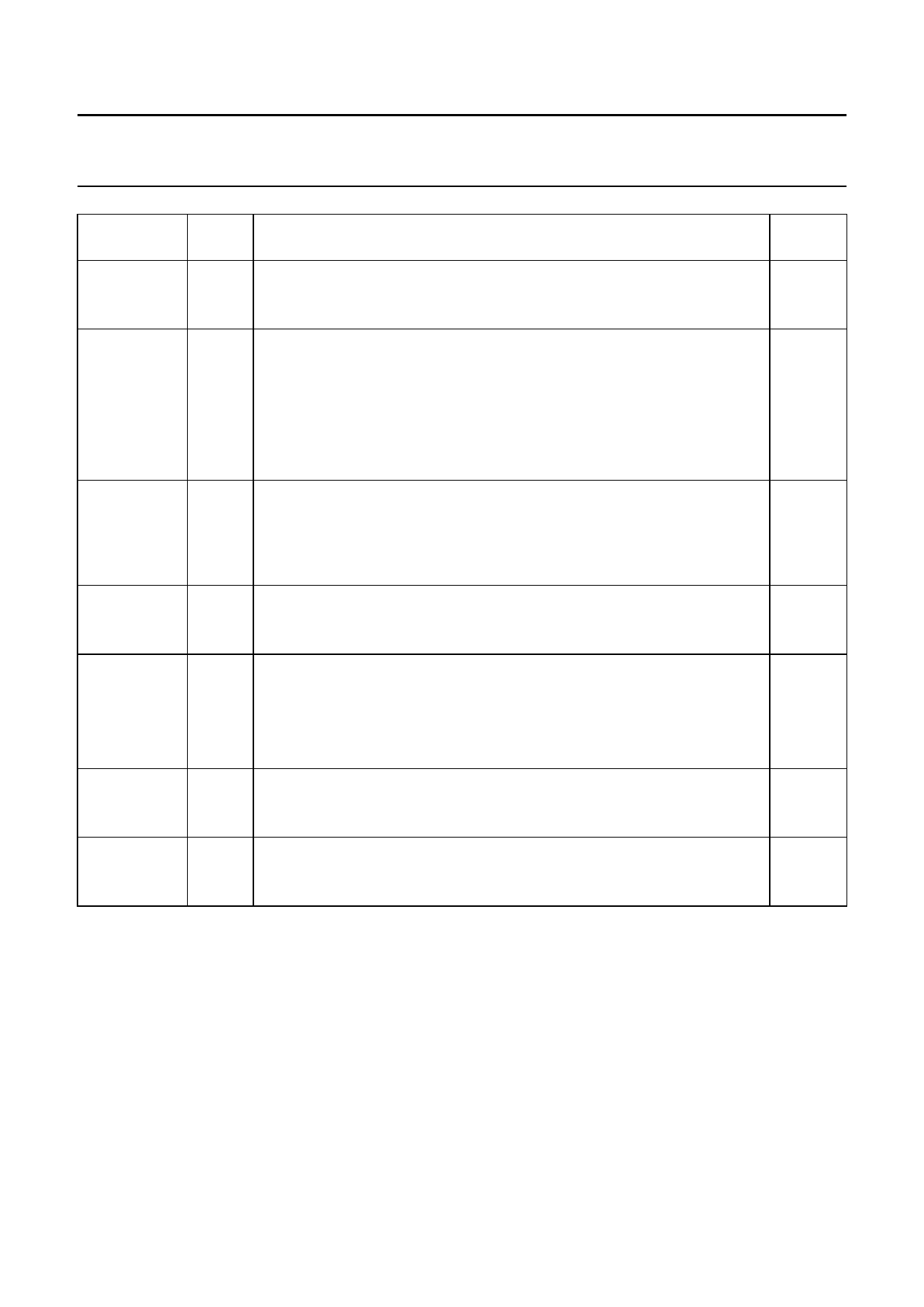

7 PINNING

SYMBOL

VSS

TX2

VDD

TX1

MODE

XTAL1

XTAL2

SCLK

DIN

DOUT

n.c.

CEXT

QGND

RX

PIN DESCRIPTION

1 ground supply

2 antenna driver output 2

3 supply voltage (5 V stabilized)

4 antenna driver output 1

5 control input to enable filtering of serial clock and data input; for active antenna applications

6 oscillator input 1

7 oscillator input 2

8 serial clock input of microcontroller interface

9 serial data input of microcontroller interface

10 serial data output of microcontroller interface

11 not connected

12 high-pass filter coupling capacitor connection

13 internal analog virtual ground capacitor connection

14 demodulator input

handbook, halfpage

VSS 1

TX2 2

VDD 3

TX1 4

MODE 5

XTAL1 6

XTAL2 7

14 RX

13 QGND

12 CEXT

HTRC11001T 11 n.c.

10 DOUT

9 DIN

8 SCLK

MGW266

Fig.2 Pin configuration.

2001 Nov 23

5

5 Page

Philips Semiconductors

HITAG reader chip

Product specification

HTRC11001T

BIT NAME VALUE

DESCRIPTION

PD_MODE

select Power-down mode

0 Idle mode

1 Power-down mode

FREEZE1,

FREEZE0

facility to achieve fast settling times (MSB and LSB)

00 normal operation

01 main low-pass is frozen; main high-pass is pre-charged to level on pin QGND

10 main low-pass is frozen; time constant of main high-pass is reduced by a

factor of 16 for bit FILTERH = 0 and by a factor of 8 for bit FILTERH = 1

11 main high-pass time constant is reduced by a factor of 16 for bit FILTERH = 0

and by a factor of 8 for bit FILTERH = 1; second high-pass is pre-charged

ACQAMP

store signal amplitude (see also bit AMPCOMP in Table 5)

0 set status bit AMPCOMP when the actual data signal amplitude is higher than

the stored reference

1 store actual amplitude of the data signal as reference for later amplitude

comparison

THRESET

reset threshold generation of digitizer

0 no reset

1 reset

FSEL1, FSEL0

clock frequency selection (MSB and LSB)

00 4 MHz

01 8 MHz

10 12 MHz

11 16 MHz

DISSMART-

COMP

disable smart comparator

0 smart comparator: on

1 smart comparator: off

DISLP1

disable low-pass 1

0 low-pass: on

1 low-pass: off

INITIAL

VALUE

0

00

0

0

00

0

0

2001 Nov 23

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet HTRC11001T.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HTRC11001 | HITAG reader chip | NXP Semiconductors |

| HTRC11001T | HITAG reader chip | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |