|

|

PDF LTC1604I Data sheet ( Hoja de datos )

| Número de pieza | LTC1604I | |

| Descripción | High Speed/ 16-Bit/ 333ksps Sampling A/D Converter with Shutdown | |

| Fabricantes | Linear Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LTC1604I (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

LTC1604

High Speed, 16-Bit, 333ksps

Sampling A/D Converter

with Shutdown

FEATURES

s A Complete, 333ksps 16-Bit ADC

s 90dB S/(N+D) and –100dB THD (Typ)

s Power Dissipation: 220mW (Typ)

s No Pipeline Delay

s No Missing Codes over Temperature

s Nap (7mW) and Sleep (10µW) Shutdown Modes

s Operates with Internal 15ppm/°C Reference

or External Reference

s True Differential Inputs Reject Common Mode Noise

s 5MHz Full Power Bandwidth

s ±2.5V Bipolar Input Range

s 36-Pin SSOP Package

U

APPLICATIONS

s Telecommunications

s Digital Signal Processing

s Multiplexed Data Acquisition Systems

s High Speed Data Acquisition

s Spectrum Analysis

s Imaging Systems

DESCRIPTION

The LTC®1604 is a 333ksps, 16-bit sampling A/D con-

verter that draws only 220mW from ±5V supplies. This

high performance device includes a high dynamic range

sample-and-hold, a precision reference and a high speed

parallel output. Two digitally selectable power shutdown

modes provide power savings for low power systems.

The LTC1604’s full-scale input range is ± 2.5V. Outstand-

ing AC performance includes 90dB S/(N+D) and – 100dB

THD at a sample rate of 333ksps.

The unique differential input sample-and-hold can acquire

single-ended or differential input signals up to its 15MHz

bandwidth. The 68dB common mode rejection allows

users to eliminate ground loops and common mode noise

by measuring signals differentially from the source.

The ADC has µP compatible,16-bit parallel output port.

There is no pipeline delay in conversion results. A separate

convert start input and a data ready signal (BUSY) ease

connections to FlFOs, DSPs and microprocessors.

, LTC and LT are registered trademarks of Linear Technology Corporation.

TYPICAL APPLICATION

+

47µF

DIFFERENTIAL

ANALOG INPUT

± 2.5V

2.2µF

3

VREF

10µF

5V 10µF

10Ω

+

36

+

35

AVDD AVDD

4 REFCOMP

4.375V

1.75X

7.5k 2.5V

REF

5V 10µF

+

9 10

DVDD

DGND

SHDN 33

CONTROL

LOGIC

AND

TIMING

CS 32

CONVST 31

RD 30

BUSY 27

µP

CONTROL

LINES

1 AIN+

2 AIN–

+

16-BIT

SAMPLING

– ADC

B15 TO B0

OUTPUT

BUFFERS

AGND AGND AGND AGND VSS

5 6 7 8 34

OVDD 29

OGND 28

5V OR

3V

10µF

D15 TO D0

16-BIT

PARALLEL

BUS

11 TO 26

1604 TA01

+ 10µF

–5V

LTC1604 4096 Point FFT

0

fSAMPLE = 333kHz

–20 fIN = 100kHz

SINAD = 89dB

THD = –96dB

–40

–60

–80

–100

–120

–140

0 20 40 60 80 100 120 140 160

FREQUENCY (kHz)

1604 TA02

1

1 page

WU

TI I G CHARACTERISTICS (Note 5)

The q denotes specifications that apply over the full operating temperature

range.

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: All voltage values are with respect to ground with DGND, OGND

and AGND wired together unless otherwise noted.

Note 3: When these pin voltages are taken below VSS or above VDD, they

will be clamped by internal diodes. This product can handle input currents

greater than 100mA below VSS or above VDD without latchup.

Note 4: When these pin voltages are taken below VSS, they will be clamped

by internal diodes. This product can handle input currents greater than

100mA below VSS without latchup. These pins are not clamped to VDD.

Note 5: VDD = 5V, VSS = – 5V, fSMPL = 333kHz, and tr = tf = 5ns unless

otherwise specified.

Note 6: Linearity, offset and full-scale specification apply for a single-

ended AIN+ input with AIN– grounded.

LTC1604

Note 7: Integral nonlinearity is defined as the deviation of a code from a

straight line passing through the actual endpoints of the transfer curve.

The deviation is measured from the center of the quantization band.

Note 8: Typical RMS noise at the code transitions. See Figure 17 for

histogram.

Note 9: Bipolar offset is the offset voltage measured from – 0.5LSB when

the output code flickers between 0000 0000 0000 0000 and 1111 1111

1111 1111.

Note 10: Signal-to-Noise Ratio (SNR) is measured at 5kHz and distortion

is measured at 100kHz. These results are used to calculate Signal-to-Nosie

Plus Distortion (SINAD).

Note 11: Guaranteed by design, not subject to test.

Note 12: Recommended operating conditions.

Note 13: The falling CONVST edge starts a conversion. If CONVST returns

high at a critical point during the conversion it can create small errors. For

best performance ensure that CONVST returns high either within 250ns

after conversion start or after BUSY rises.

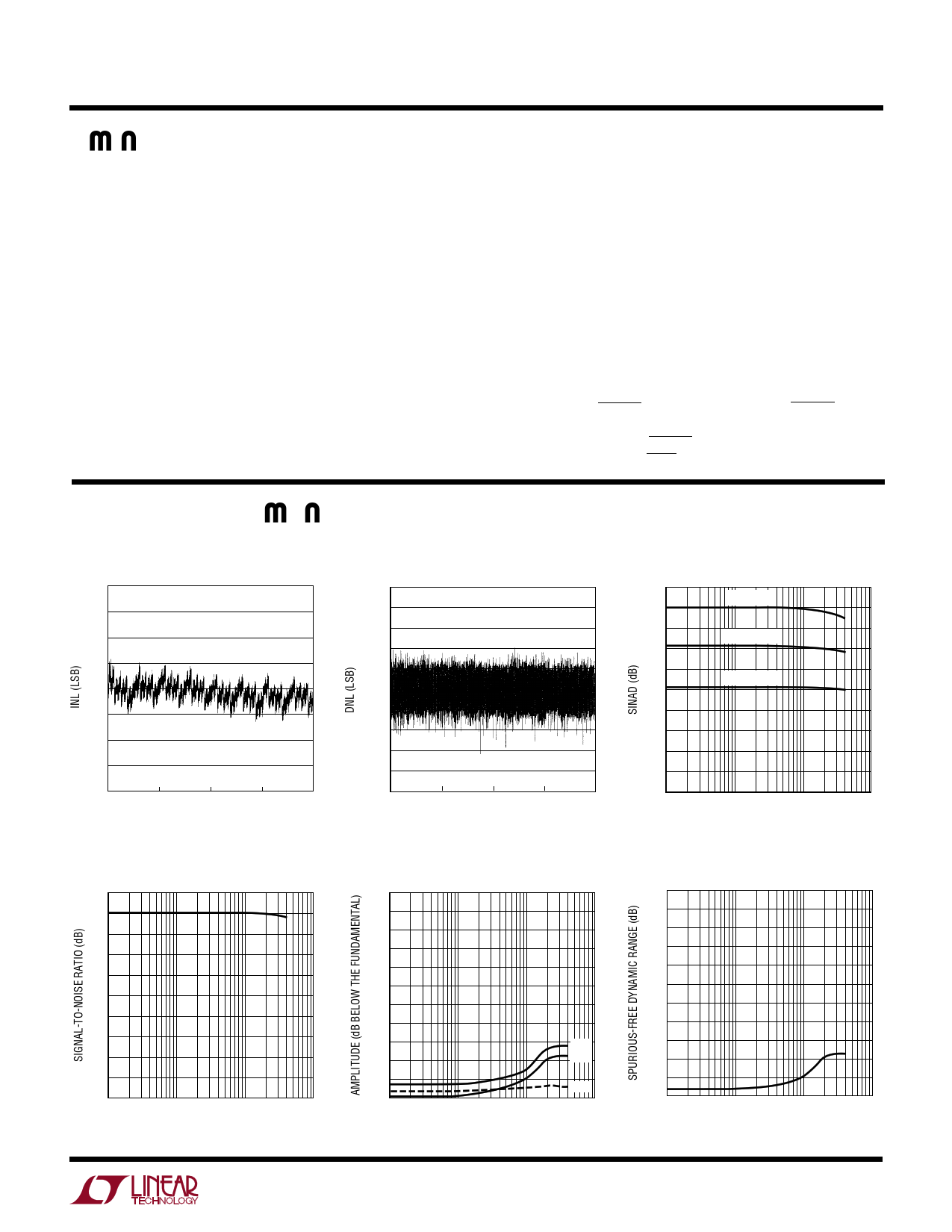

TYPICAL PERFORMANCE CHARACTERISTICS

Integral Nonlinearity vs

Output Code

2.0

1.5

1.0

0.5

0.0

–0.5

–1.0

–1.5

–2.0

–32768 –16384

0

16384 32767

CODE

1604 G11

Signal-to-Noise Ratio vs

Input Frequency

100

90

80

70

60

50

40

30

20

10

0

1k 10k 100k 1M

FREQUENCY (Hz)

1604 G03

Differential Nonlinearity vs

Output Code

1.0

0.8

0.6

0.4

0.2

0.0

–0.2

–0.4

–0.6

–0.8

–1.0

–32768 –16384

0

16384 32767

CODE

1604 G10

Distortion vs Input Frequency

0

–10

–20

–30

–40

–50

–60

–70

–80 THD

–90 3RD

–100

–110

1k

10k 100k

INPUT FREQUENCY (Hz)

2ND

1M

1604 G04

S/(N + D) vs Input Frequency

and Amplitude

100

VIN = 0dB

90

80 VIN = –20dB

70

60 VIN = –40dB

50

40

30

20

10

0

1k 10k 100k 1M

FREQUENCY (Hz)

1604 G01

Spurious-Free Dynamic Range

vs Input Frequency

0

–10

–20

–30

–40

–50

–60

–70

–80

–90

–100

–110

1k

10k 100k

INPUT FREQUENCY (Hz)

1M

1604 G05

5

5 Page

LTC1604

APPLICATIONS INFORMATION

CS = 0

tCONV

t8

RD = CONVST

BUSY

t6

t11

DATA

t10

DATA (N – 1)

D5 TO D0

t7

DATA N

D15 TO D0

DATA N

D15 TO D0

Figure 8. Mode 2. Slow Memory Mode Timing

DATA (N + 1)

D15 TO D0

1604 F08

CS = 0

RD = CONVST

BUSY

DATA

tCONV

t8

t6 t11

t10

DATA (N – 1)

D15 TO D0

DATA N

D15 TO D0

Figure 9. ROM Mode Timing

1604 F09

three-state until read by the MPU with the RD signal. Mode

2 can be used for operation with a shared data bus.

In slow memory and ROM modes (Figures 8 and 9) CS is

tied low and CONVST and RD are tied together. The MPU

starts the conversion and reads the output with the com-

bined CONVST-RD signal. Conversions are started by the

MPU or DSP (no external sample clock is needed).

In slow memory mode the processor applies a logic low to

RD (= CONVST), starting the conversion. BUSY goes low,

forcing the processor into a wait state. The previous

conversion result appears on the data outputs. When the

conversion is complete, the new conversion results

appear on the data outputs; BUSY goes high, releasing the

processor and the processor takes RD (= CONVST) back

high and reads the new conversion data.

In ROM mode, the processor takes RD (= CONVST) low,

starting a conversion and reading the previous conversion

result. After the conversion is complete, the processor can

read the new result and initiate another conversion.

DIFFERENTIAL ANALOG INPUTS

Driving the Analog Inputs

The differential analog inputs of the LTC1604 are easy to

drive. The inputs may be driven differentially or as a single-

ended input (i.e., the AIN– input is grounded). The AIN+ and

AIN– inputs are sampled at the same instant. Any un-

wanted signal that is common mode to both inputs will be

reduced by the common mode rejection of the sample-

and-hold circuit. The inputs draw only one small current

spike while charging the sample-and-hold capacitors at

the end of conversion. During conversion the analog

inputs draw only a small leakage current. If the source

impedance of the driving circuit is low, then the LTC1604

inputs can be driven directly. As source impedance in-

creases so will acquisition time (see Figure 10). For

minimum acquisition time with high source impedance, a

buffer amplifier should be used. The only requirement is

that the amplifier driving the analog input(s) must settle

after the small current spike before the next conversion

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet LTC1604I.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LTC1604 | High Speed/ 16-Bit/ 333ksps Sampling A/D Converter with Shutdown | Linear Technology |

| LTC1604ACG | High Speed/ 16-Bit/ 333ksps Sampling A/D Converter with Shutdown | Linear Technology |

| LTC1604AIG | High Speed/ 16-Bit/ 333ksps Sampling A/D Converter with Shutdown | Linear Technology |

| LTC1604C | High Speed/ 16-Bit/ 333ksps Sampling A/D Converter with Shutdown | Linear Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |