|

|

PDF DECIMATE Data sheet ( Hoja de datos )

| Número de pieza | DECIMATE | |

| Descripción | DECIMATE | |

| Fabricantes | Intersil Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de DECIMATE (archivo pdf) en la parte inferior de esta página. Total 5 Páginas | ||

|

No Preview Available !

Data Sheet

DECIMATE™

May 1999 File Number 3368.1

Intersil HSP43220 Decimating Digital Filter

Development Software

Intersil DECIMATE Development Software assists the design

engineer to prototype designs for the Intersil HSP43220

Decimating Digital filter (DDF). Developed specifically for the

DDF, this software consists of three integrated modules:

DDF Design, DDF Simulator and DDF PROM. The Design

module designs a filter from a set of user specifications for

the DDF. The Simulator module models the DDF’s internal

operation. The PROM module uses the device configuration

created by the Design module to build a PROM data file that

can be used to store and download the DDF configuration.

DDF System Design

The DDF consists of two stages: a High Decimation Filter

(HDF) and a Finite Impulse Response (FIR) filter. Together

these provide a unique narrow band, low pass filter. Because of

this unique architecture, special software is required to

configure the device for a given set of filter parameters. This

software uses system level filter parameters (listed below) to

perform the trade off analysis and calculate the values for the

DDF’s Configuration Registers and FIR coefficients.

Design specifications are supplied by the user in terms of:

1. Input sample frequency.

2. Required output sample frequency.

3. Passband signal bandwidth.

4. Transition bandwidth.

5. Amount of attenuation allowed in the passband.

6. Amount of stopband attenuation required for signals

outside of the band of interest.

This information is entered into a menu screen (See Figure

1), providing immediate feedback on the design validity. The

design module calculates the order of the HDF, HDF

decimation required, the FIR input data rate, minimum clock

frequency for the FIR, FIR order and decimation required in

the FIR.

The design module will then generate the FIR filter. Four

different methods are provided for the FIR design:

1. A Standard FIR automatically designed by the module

using the Parks-McClellan method to compute the

coefficients of an equiripple (Chebyshev) filter.

2. Any FIR imported into the Design module from another

FIR design program.

3. A precompensated FIR which is automatically designed

by the module to compensate for the roll-off in the

passband of the HDF frequency response.

4. The FIR may also be bypassed in which case the optimal

HDF is designed from the user specifications.

Frequency response curves are then displayed showing the

resulting responses in the HDF, FIR and for the entire chip

using the given filter design. Figure 2 is a typical display. The

user may save this frequency response data for further

analysis. The design module also creates a report file

documenting the filter design and providing the coefficients

and setup register values for programming the device.

DDF Simulator

The simulator provides an accurate simulation of the device

before any hardware is built. It can be used to simulate any

filter designed with DECIMATE. The simulator takes into

account the fixed point bus widths and pipeline delays for

every element in the DDF.

The simulator provides the user with an input signal which

can be used to stimulate the filter. This signal is created from

the options shown in Table 1. The user can select a pure

step, impulse, cosine, chirp, uniform or Gaussian noise as

the input signal, or a more complex signal can be generated

by combining that data with an option selected from the

Signal #2 column, with the combining operator chosen from

the middle column. The user can also import a signal from

an outside source.

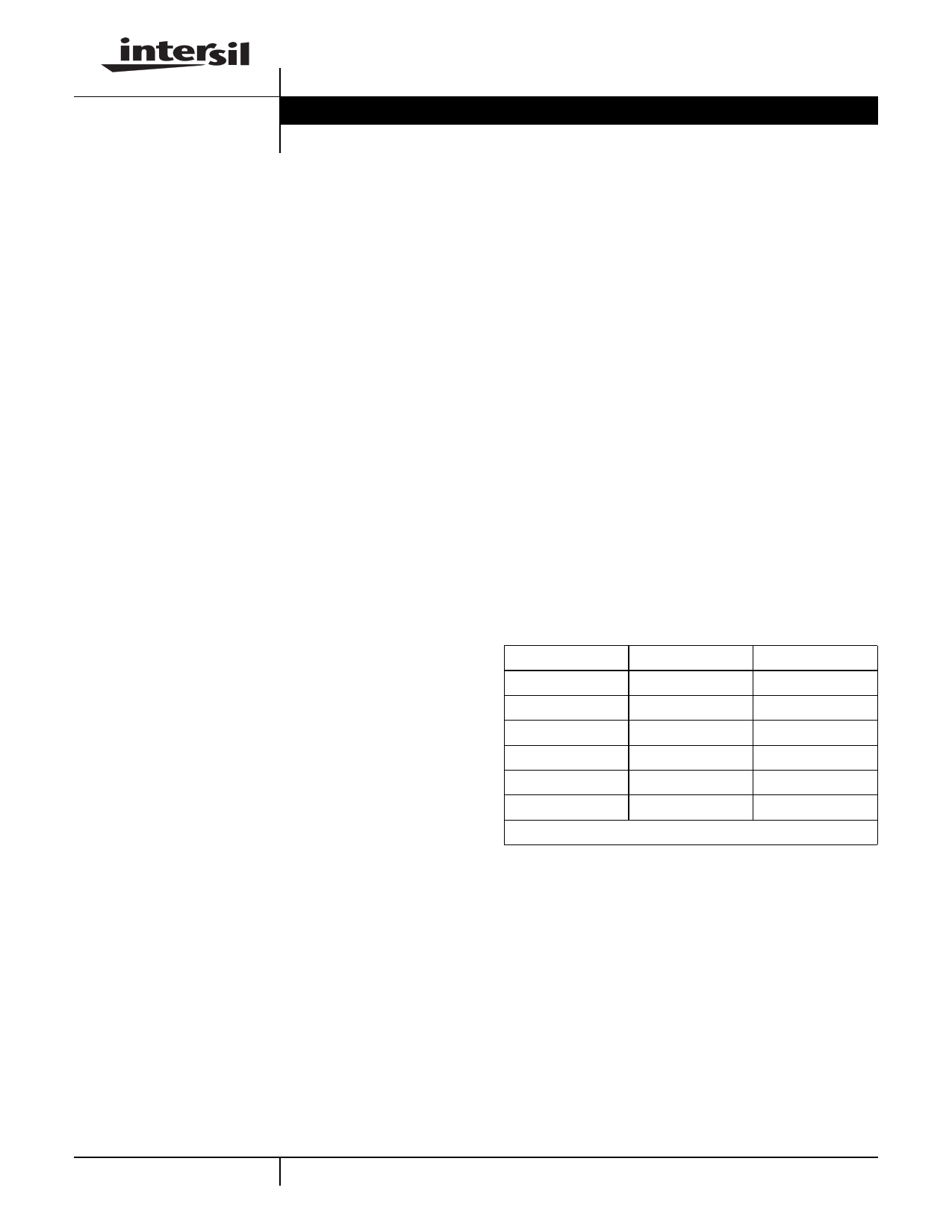

TABLE 1.

SIGNAL #1

OPERATION

SIGNAL #2

Step

Step

Impulse

No Operation

Impulse

COSlNE

Add

COSINE

Chirp

Concatenate

Chirp

Uniform Noise

Multiply

Uniform Noise

Gaussian Noise

Gaussian Noise

Imported From Outside

Probes are provided to select specific areas to graphically

display data values, as well as save into data files for further

processing. The DDF Simulator has two levels; the DDF

Simulator Specification Screen and the DDF Simulator Main

Screen.

The Specification Screen (see Figure 3) is used to input the

simulation parameters. The user selects display modes in

either continuous or decimated format and data formats in

either decimal or hexadecimal. The Specification Screen

also provides for selection of the input signal.

The simulator main screen (see Figure 4) defines the

simulator test probes and displays the data values per clock

cycle. The interactive simulator screen consists of the

HSP43220 Block Diagram, test probes and register

1 CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999

DECIMATE™ is a trademark of Intersil Corporation.

1 page

PROBE #0

1.0999

0.9999

0.8999

0

PROBE #1

6.70E + 07

3.35E + 07

42954

0

PROBE #2

6.70E + 07

3.44E + 07

2723756

0

PROBE #3

0.9536

0.4768

0

0

PROBE #4

0.9621

0.4581

-0.0458

0

DECIMATE

511.5

511.5

29

29

14

FIGURE 5. SIMULATOR PROBE DISPLAY

1023

1023

58

58

28

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time with-

out notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and

reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result

from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

Sales Office Headquarters

NORTH AMERICA

Intersil Corporation

P. O. Box 883, Mail Stop 53-204

Melbourne, FL 32902

TEL: (407) 724-7000

FAX: (407) 724-7240

EUROPE

Intersil SA

Mercure Center

100, Rue de la Fusee

1130 Brussels, Belgium

TEL: (32) 2.724.2111

FAX: (32) 2.724.22.05

ASIA

Intersil (Taiwan) Ltd.

7F-6, No. 101 Fu Hsing North Road

Taipei, Taiwan

Republic of China

TEL: (886) 2 2716 9310

FAX: (886) 2 2715 3029

5

5 Page | ||

| Páginas | Total 5 Páginas | |

| PDF Descargar | [ Datasheet DECIMATE.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DECIMATE | DECIMATE | Intersil Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |