|

|

PDF LXT970A Data sheet ( Hoja de datos )

| Número de pieza | LXT970A | |

| Descripción | Dual-Speed Fast Ethernet Transceiver | |

| Fabricantes | Intel Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de LXT970A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

LXT970A

Dual-Speed Fast Ethernet Transceiver

Datasheet

The LXT970A is an enhanced derivative of the LXT970 10/100 Mbps Fast Ethernet PHY

Transceiver that supports selectable driver strength capabilities and link-loss criteria. The

LXT970A supports 100BASE-TX, 10BASE-T, and 100BASE-FX applications. It provides a

Media Independent Interface (MII) for easy attachment to 10/100 Media Access Controllers

(MAC)s and a pseudo-ECL interface for use with 100BASE-FX fiber networks.

The LXT970A supports full-duplex operation at 10 and 100 Mbps. Its operating condition is set

using auto-negotiation, parallel detection or manual control. The encoder may be bypassed for

symbol mode applications.

The LXT970A is fabricated with an advanced CMOS process and requires only a single 5V

power supply. The MII may be operated independently with either a 5V or a 3.3V supply.

Applications

s Combination 10BASE-T/100BASE-TX

Network Interface Cards (NICs)

s 10/100 Switches, 10/100 Printservers

Product Features

s 100BASE-FX Network Interface Cards

(NICs)

s IEEE 802.3 Compliant:

— 10BASE-T and 100BASE-TX using a

single RJ-45 connection.

— Supports auto-negotiation and parallel

detection for legacy systems.

— MII interface with extended register

capability.

s Robust baseline wander correction

performance.

s 100BASE-FX fiber optic capable.

s Standard CSMA/CD or full-duplex

operation.

s Configurable via MII serial port or external

control pins.

s Configurable for DTE or switch

applications.

s CMOS process with single 5Vsupply

operation

with provision for interface to 3.3V MII

bus.

s Integrated LED drivers.

s Integrated supply monitor and line

disconnect during low supply fault.

s Available in:

— 64-pin TQFP (LXT970ATC)

— 64-pin PQFP (LXT970AQC)

s Commercial temperature range (0 - 70oC

ambient).

As of January 15, 2001, this document replaces the Level One document

LXT970A — Dual-Speed Fast Ethernet Transceiver.

Order Number: 249099-001

January 2001

1 page

Dual-Speed Fast Ethernet Transceiver — LXT970A

Figures

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

LXT970A Block Diagram ....................................................................................... 9

LXT970A Pin Assignments .................................................................................10

Network Interface Card (NIC) Application ..........................................................18

MII Interface .......................................................................................................20

MII Data Interface ...............................................................................................21

Loopback Paths ..................................................................................................23

Repeater Block Diagram ....................................................................................24

MDIO Interrupt Signaling ....................................................................................25

Management Interface - Read Frame Structure .................................................25

Management Interface - Write Frame Structure .................................................25

LXT970A Initialization Sequence .......................................................................30

Auto-Negotiation Operation ................................................................................31

100BASE-TX Frame Structure ...........................................................................33

100BASE-TX Data Flow .....................................................................................33

LXT970A Protocol Sublayers .............................................................................36

100BASE-TX Reception with No Errors .............................................................37

100BASE-TX Reception with Invalid Symbol ....................................................37

100BASE-TX Transmission with No Errors .......................................................37

100BASE-TX Transmission with Collision .........................................................37

Voltage Divider ...................................................................................................45

Typical Interface Circuitry ...................................................................................46

MII - 100BASE-TX Receive Timing / 4B Mode ...................................................51

MII - 100BASE-TX Transmit Timing / 4B Mode .................................................52

MII - 100BASE-TX Receive Timing / 5B Mode ...................................................53

100BASE-TX Transmit Timing / 5B Mode ..........................................................54

MII - 100BASE-FX Receive Timing / 4B Mode ...................................................55

MII - 100BASE-FX Transmit Timing / 4B Mode ..................................................56

MII - 10BASE-T Receiving Timing ......................................................................57

MII - 10BASE-T Transmit Timing .......................................................................58

10BASE-T SQE (Heartbeat) Timing ...................................................................59

10BASE-T Jab and Unjab Timing ......................................................................59

Auto Negotiation and Fast Link Pulse Timing ....................................................60

Fast Link Pulse Timing .......................................................................................60

MDIO Timing when Sourced by STA .................................................................61

MDIO Timing when Sourced by PHY .................................................................61

Power-Down Recovery Timing (Over Recommended Range) ...........................62

PHY Identifier Bit Mapping .................................................................................66

64-Pin QFP Package Diagram ...........................................................................73

64-Pin TQFP Package Diagram .........................................................................74

Datasheet

5

5 Page

Dual-Speed Fast Ethernet Transceiver — LXT970A

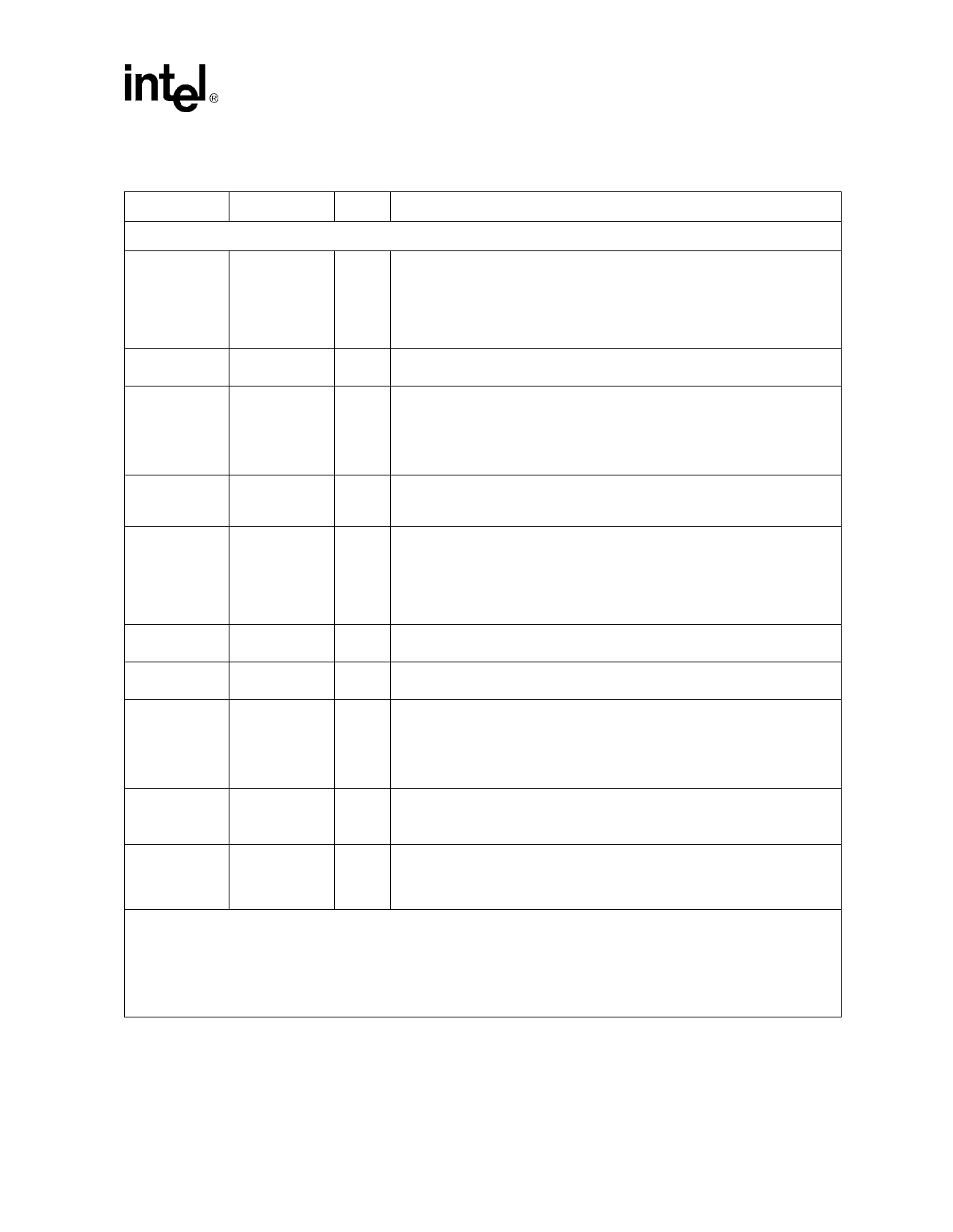

Table 2. LXT970A MII Signal Descriptions

Pin#1

Pin Name

I/O2,3

Signal Description4

MII Data Interface Pins

63 TXD4

62 TXD3

Transmit Data. The Media Access Controller (MAC) drives data to the

61

TXD2

I LXT970A using these inputs. TXD4 is monitored only in Symbol (5B) Mode.

60 TXD1

These signals must be synchronized to the TX_CLK.

59 TXD0

58

TX_EN

I

Transmit Enable. The MAC asserts this signal when it drives valid data on the

TXD inputs. This signal must be synchronized to the TX_CLK.

Transmit Clock. Normally the LXT970A drives TX_CLK; in Slave Clock Mode,

TX_CLK is an input. Refer to the Clock Requirements discussion in the

57

TX_CLK

I/O Functional Description section on page 18.

25 MHz for 100 Mbps operation.

2.5 MHz for 10 Mbps operation.

Transmit Coding Error. The MAC asserts this input when an error has

56

TX_ER

I occurred in the transmit data stream. When the LXT970A is operating at 100

Mbps, the LXT970A responds by sending invalid code symbols on the line.

46 RXD4

47 RXD3

Receive Data. The LXT970A drives received data on these outputs,

48

RXD2

O synchronous to RX_CLK.

49 RXD1

RXD4 is driven only in Symbol (5B) Mode.

50 RXD0

51

RX_DV

O

Receive Data Valid. The LXT970A asserts this signal when it drives valid data

on RXD. This output is synchronous to RX_CLK.

55

RX_ER

O

Receive Error. The LXT970A asserts this output when it receives invalid

symbols from the network. This signal is synchronous to RX_CLK.

Receive Clock. This continuous clock provides reference for RXD, RX_DV, and

RX_ER signals. Refer to the Clock Requirements discussion in the Functional

54

RX_CLK

O Description section.

25 MHz for 100 Mbps operation.

2.5 MHz for 10 Mbps operation.

Collision Detected. The LXT970A asserts this output when detecting a

64

COL

O collision. This output remains High for the duration of the collision.

This signal is asynchronous and inactive during full-duplex operation.

Carrier Sense. During half-duplex operation (bit 0.8 = 0), the LXT970A asserts

1

CRS

O

this output when either transmit or receive medium is non-idle. During full-

duplex operation (bit 0.8 = 1) or repeater operation

(bit 19.13 = 1), CRS is asserted only when the receive medium is non-idle.

1. Pin numbers apply to all package types.

2. I/O Column Coding: I = Input, O = Output, OD = Open Drain, A = Analog.

3. If bit 17.3 = 0, 55Ω series termination resistors are recommended on all output signals to avoid undershoot/overshoot, even

on short traces.

If bit 17.3 = 1, termination resistors are not required.

4. The LXT970A supports the 802.3 MDIO register set. Specific bits in the registers are referenced using an “X.Y” notation,

where X is the register number (0-6 or 16-20) and Y is the bit number (0-15).

Datasheet

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet LXT970A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LXT970 | Fast Ethernet Transceiver | Level One |

| LXT970A | Dual-Speed Fast Ethernet Transceiver | Intel Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |