|

|

PDF 5962-9313001MPA Data sheet ( Hoja de datos )

| Número de pieza | 5962-9313001MPA | |

| Descripción | High Speed/ Video Difference Amplifier | |

| Fabricantes | Analog Devices | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 5962-9313001MPA (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

a

High Speed, Video

Difference Amplifier

FEATURES

Differential Amplification

Wide Common-Mode Voltage Range: +12.8 V, –12 V

Differential Voltage Range: ؎2 V

High CMRR: 60 dB @ 4 MHz

Built-in Differential Clipping Level: ؎2.3 V

Fast Dynamic Performance

85 MHz Unity Gain Bandwidth

35 ns Settling Time to 0.1%

360 V/s Slew Rate

Symmetrical Dynamic Response

Excellent Video Specifications

Differential Gain Error: 0.06%

Differential Phase Error: 0.08؇

15 MHz (0.1 dB) Bandwidth

Flexible Operation

High Output Drive of ؎50 mA min

Specified with Both ؎5 V and ؎15 V Supplies

Low Distortion: THD = –72 dB @ 4 MHz

Excellent DC Performance: 3 mV max Input Offset

Voltage

APPLICATIONS

Differential Line Receiver

High Speed Level Shifter

High Speed In-Amp

Differential to Single Ended Conversion

Resistorless Summation and Subtraction

High Speed A/D Driver

PRODUCT DESCRIPTION

The AD830 is a wideband, differencing amplifier designed for

use at video frequencies but also useful in many other applica-

tions. It accurately amplifies a fully differential signal at the

110

100

90

80 VS = ±15V

70

60

VS = ±5V

50

40

30

1k

10k 100k 1M

10M

FREQUENCY – Hz

Common-Mode Rejection Ratio vs. Frequency

REV. A

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for its

use, nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

AD830

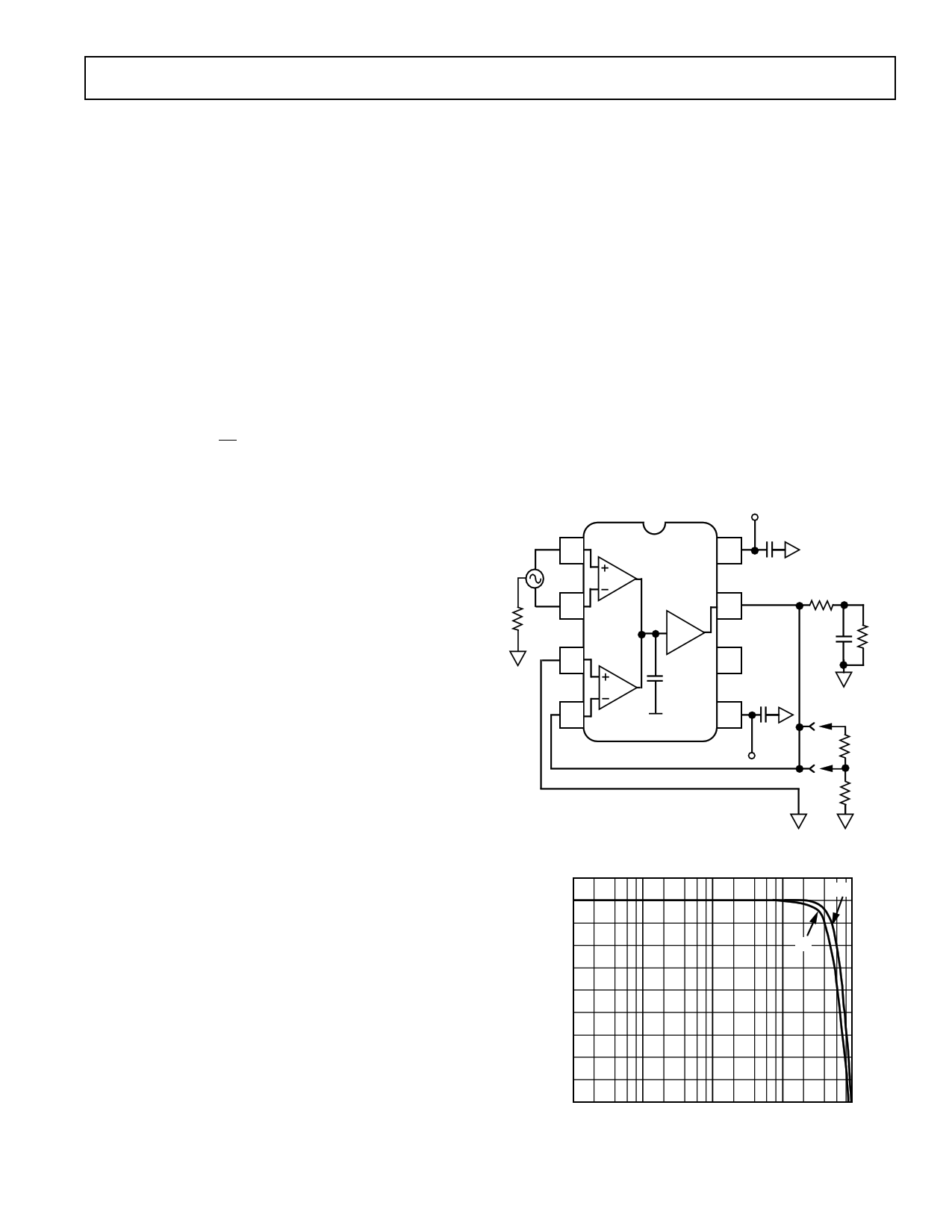

CONNECTION DIAGRAM

8-Pin Plastic Mini-DIP (N),

Cerdip (Q) and SOIC (R) Packages

X1 1

X2 2

Y1 3

Y2 4

V→1

V→1

AD830

A=1

8 VP

7 OUT

6 NC

5 VN

NC = NO CONNECT

input and produces an output voltage referred to a user-chosen

level. The undesired common-mode signal is rejected, even at

high frequencies. High impedance inputs ease interfacing to fi-

nite source impedances and thus preserve the excellent

common-mode rejection. In many respects, it offers significant

improvements over discrete difference amplifier approaches, in

particular in high frequency common-mode rejection.

The wide common-mode and differential-voltage range of the

AD830 make it particularly useful and flexible in level shifting

applications, but at lower power dissipation than discrete solu-

tions. Low distortion is preserved over the many possible differ-

ential and common-mode voltages at the input and output.

Good gain flatness and excellent differential gain of 0.06% and

phase of 0.08° make the AD830 suitable for many video system

applications. Furthermore, the AD830 is suited for general pur-

pose signal processing from dc to 10 MHz.

9

6 VS = ±5V

RL = 150Ω

3

0

CL = 33pF

–3

CL = 4.7pF

–6

–9

–12

CL = 15pF

–15

–18

–21

10k

100k

1M

10M 100M 1G

FREQUENCY – Hz

Closed-Loop Gain vs. Frequency, Gain = +1

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700

Fax: 617/326-8703

1 page

110

100

90

80 VS = ±15V

70

60

VS = ±5V

50

40

30

1k

10k 100k 1M

FREQUENCY – Hz

10M

Figure 1. Common-Mode Rejection Ratio vs. Frequency

–50

VOUT = 2V p-p

RL = 150Ω

GAIN = +1

–60

–70

±5V SUPPLIES

2ND HARMONIC

3RD HARMONIC

±15V SUPPLIES

2ND HARMONIC

–80 3RD HARMONIC

–90

1k

10k 100k

FREQUENCY – Hz

1M

10M

Figure 2. Harmonic Distortion vs. Frequency

9

8

7

6

5

4

3

–60 –40 –20 0

20 40 60 80 100 120 140

JUNCTION TEMPERATURE – °C

Figure 3. Input Bias Current vs. Temperature

Typical Characteristics–AD830

100

90

TO VP @ ±5V

80

TO VN @ ±15V

70

TO VP @ ±15V

60

TO VN @ ±5V

50

40

30

20

10

1k

10k 100k 1M

FREQUENCY – Hz

10M

Figure 4. Power Supply Rejection Ratio vs. Frequency

3

0

–3

RL = 150Ω

–6 CL = 4.7pF

–9

±15V

±10V

–12

–15

–18 ±5V

–21

–24

–27

10k

100k

1M 10M

FREQUENCY – Hz

100M

1G

Figure 5. Closed-Loop Gain vs. Frequency G = +1

3

±5V S

2

1 ±10VS

0

–1 ±15VS

–2

–3

–4

–60 –40 –20 0

20 40 60 80 100 120 140

JUNCTION TEMPERATURE – °C

Figure 6. Input Offset Voltage vs. Temperature

REV. A

–5–

5 Page

AD830

Choice of Polarity

The sign of the gain is easily selected by choosing the polarity of

the connections to the + and – inputs of the X GM stage. Swap-

ping between inverting and noninverting gain is possible simply

by reversing the input connections. The response of the ampli-

fier is identical in either connection, except for the sign change.

The bandwidth, high impedance, transient behavior, etc., of the

AD830, is symmetrical for both polarities of gain. This is very

advantageous and unlike an op amp.

Input Impedance

The relatively high input impedance of the AD830, for a differ-

ential receiver amplifier, permits connections to modest imped-

ance sources without much loading or loss of common-mode

rejection. The nominal input resistance is 300 kΩ. The real limit

to the upper value of the source resistance is in its effect on

common-mode rejection and bandwidth. If the source resistance

is in only one input, then the low frequency common-mode re-

jection will be lowered to ≈ RIN/RS. The source resistance/input

capacitance pole

f

=

1

2π

× RS

× CIN

limits the bandwidth.

Furthermore, the high frequency common-mode rejection will

be additionally lowered by the difference in the frequency re-

sponse caused by the RS ϫ CIN pole. Therefore, to maintain

good low and high frequency common-mode rejection, it is rec-

ommended that the source resistances of the + and – inputs be

matched and of modest value (≤10 kΩ).

Handling Bias Currents

The bias currents are typically 4 µA flowing into each pin of the

GM stages of the AD830. Since all applications possess some fi-

nite source resistance, the bias current through this resistor will

create a voltage drop (IBIAS ϫ RS). The relatively high input im-

pedance of the AD830 permits modest values of RS, typically

≤10 kΩ. If the source resistance is in only one terminal, then an

objectional offset voltage may result (e.g., 4 µA ϫ 5 kΩ =

20 mV). Placement of an equal value resistor in series with the

other input will cancel the offset to first order. However, due to

mismatches in the resistances, a residual offset will remain and

likely be greater than bias current (offset current) mismatches.

Applying Feedback

The AD830 is intended for use with gain from 1 to 100. Gains

greater than one are simply set by a pair of resistors connected

as shown in the difference amplifier (Figure 35) with gain >1.

The value of the bottom resistor R2, should be kept less than

1 kΩ to insure that the pole formed by CIN and the parallel con-

nection of R1 and R2 is sufficiently high in frequency so that it

does not introduce excessive phase shift around the loop and de-

stabilizes the amplifier. A compensating resistor, equal to the

parallel combination of R1 and R2, should be placed in series

with the other Y GM stage input to preserve the high frequency

common-mode rejection and to lower the offset voltage induced

by the input bias current.

Output Common Mode

The output swing of the AD830 is defined by the differential in-

put voltage, the gain and the output common. Depending on

the anticipated signal span, the output common (or ground)

may be set anywhere between the allowable peak output voltage

in a manner similar to that described for input voltage common

mode. A plot of the peak output voltage versus supply is shown

in Figure 26. A prediction of the common-mode range versus

the peak output differential voltage can be easily derived from

the maximum output swing as VOCM = VMAX–VPEAK.

Output Current

The absolute peak output current is set by the short circuit cur-

rent limiting, typically greater that 60 mA. The maximum drive

capability is rated at 50 mA, but without a guarantee of distor-

tion performance. Best distortion performance is obtained by

keeping the output current ≤20 mA. Attempting to drive large

voltages into low valued resistances (e.g., 10 V into 150 Ω) will

cause an apparent lowering of the limit for output signal swing,

but is just the current limiting behavior.

Driving Cap Loads

The AD830 is capable of driving modest sized capacitive loads

while maintaining its rated performance. Several curves of band-

width versus capacitive load are given in Figures 15 and 18. The

AD830 was designed primarily as a low distortion video speed

amplifier, but with a tradeoff, giving up very large capacitive

load driving capability. If very large capacitive loads must be

driven, then the network shown in Figure 27 should be used to

insure stable operation. If the loss of gain caused by the resistor

RS in series with the load is objectionable, then the optional

feedback network shown may be added to restore the lost gain.

+VS

1

VCM

+

INPUT

SIGNAL

–

2

ZCM

GM

3

GM

4

AD830 8

7

0.1µF

RS

36.5Ω

VOUT

A=1

C

C1

100pF

R1

1kΩ

6

5

0.1µF

–VS

* OPTIONAL

FEEDBACK

NETWORK

RS

R1

Figure 27. Circuit for Driving Large Capacitive Loads

3

±15V

0

–3

–6 ±5V

–9

–12

–15

–18

–21

–24

–27

10k

100k

1M

FREQUENCY – Hz

10M

100M

Figure 28. Closed-Loop Response vs. Frequency with

100 pF Load and Series Resistor Compensation

REV. A

–11–

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet 5962-9313001MPA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 5962-9313001MPA | High Speed/ Video Difference Amplifier | Analog Devices |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |