|

|

PDF DS_K7N323601M Data sheet ( Hoja de datos )

| Número de pieza | DS_K7N323601M | |

| Descripción | 1Mx36 & 2Mx18-Bit Pipelined NtRAM | |

| Fabricantes | Samsung semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS_K7N323601M (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

K7N323601M

K7N321801M

1Mx36 & 2Mx18 Pipelined NtRAMTM

Document Title

1Mx36 & 2Mx18-Bit Pipelined NtRAM TM

Revision History

Rev. No.

History

0.0 1. Initial document.

0.1 1. Add 165FBGA package

0.2 1. Update JTAG scan order

2. Speed bin merge.

From K7N3236(18)09M to K7N3236(18)01M

3. AC parameter change.

tOH(min)/tLZC(min) from 0.8 to 1.5 at -25

tOH(min)/tLZC(min) from 1.0 to 1.5 at -22

tOH(min)/tLZC(min) from 1.0 to 1.5 at -20

0.3 1. Change pin out for 165FBGA

- x18/x36 ; 11B => from A to NC , 2R ==> from NC to A

0.4 1. Insert pin at JTAG scan order of 165FBGA in connection with

pin out change

- x18/x36 ; insert Pin ID of 2R to BIT number of 69

0.5 1. Add Icc, Isb, Isb1 and Isb2 values.

1.0 1. Final datasheet release.

1.1 1. Change the Stand-by current (Isb)

Before After

Isb - 25 : 120 170

- 22 : 110 160

- 20 : 100 150

- 16 : 90 140

- 15 : 90 140

- 13 : 90 140

Isb1 : 90 110

Isb2 : 80 100

2.0 1. Delete the 119BGA package

2. Delete the 225MHz and 150MHz speed bin

Draft Date

Remark

May. 10. 2001

Aug. 29. 2001

Dec. 31. 2001

Preliminary

Preliminary

Preliminary

Feb. 14. 2002 Preliminary

Apr. 20. 2002 Preliminary

May. 10. 2002

Sep. 26. 2002

Oct. 17, 2003

Preliminary

Final

Final

Nov. 18, 2003 Final

The attached data sheets are prepared and approved by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the

specifications. SAMSUNG Electronics will evaluate and reply to your requests and questions on the parameters of this device. If you have any ques-

tions, please contact the SAMSUNG branch office near your office, call or contact Headquarters.

- 1 - Nov. 2003

Rev 2.0

1 page

K7N323601M

K7N321801M

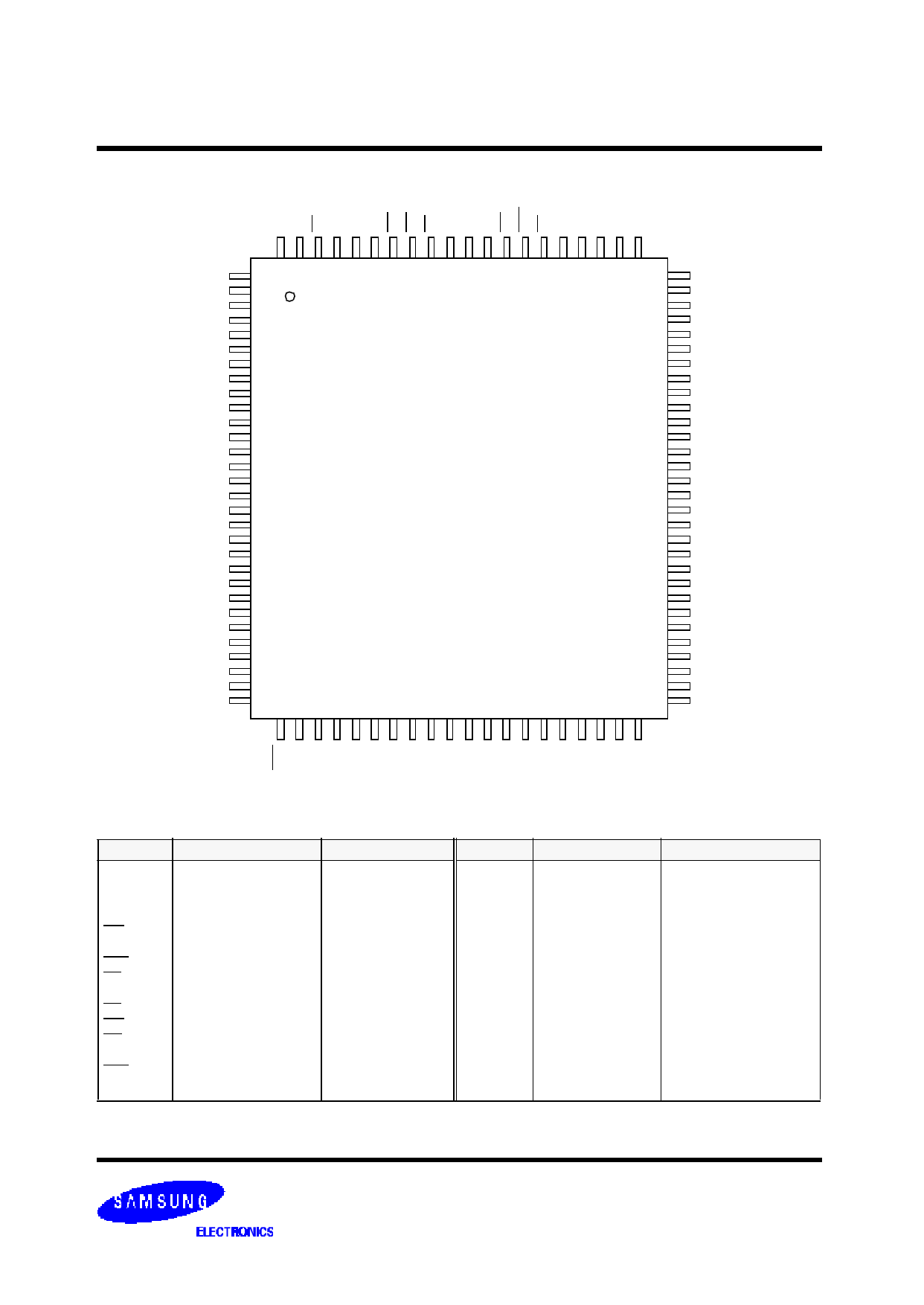

PIN CONFIGURATION(TOP VIEW)

1Mx36 & 2Mx18 Pipelined NtRAMTM

N.C.

N.C.

N.C.

VDDQ

VSSQ

N.C.

N.C.

DQb8

DQb7

VSSQ

VDDQ

DQb6

DQb5

VDD

VDD

VDD

VSS

DQb4

DQb3

VDDQ

VSSQ

DQb2

DQb1

DQb0

N.C.

VSSQ

VDDQ

N.C.

N.C.

N.C.

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

100 Pin TQFP

(20mm x 14mm)

K7N321801M(2Mx18)

80 A10

79 N.C.

78 N.C.

77 VDDQ

76 VSSQ

75 N.C.

74 DQa0

73 DQa1

72 DQa2

71 VSSQ

70 VDDQ

69 DQa3

68 DQa4

67 VSS

66 VDD

65 VDD

64 ZZ

63 DQa5

62 DQa6

61 VDDQ

60 VSSQ

59 DQa7

58 DQa8

57 N.C.

56 N.C.

55 VSSQ

54 VDDQ

53 N.C.

52 N.C.

51 N.C.

PIN NAME

SYMBOL

PIN NAME

TQFP PIN NO.

SYMBOL

PIN NAME

TQFP PIN NO.

A0 - A20

Address Inputs

ADV

Address Advance/Load

WE Read/Write Control Input

CLK

Clock

CKE

Clock Enable

CS1

Chip Select

CS2

Chip Select

CS2

Chip Select

BW x(x=a,b) Byte Write Inputs

OE Output Enable

ZZ Power Sleep Mode

LBO

Burst Mode Control

32,33,34,35,36,37,43

44,45,46,47,48,49,50,

80,81,82,83,84,99,100

85

88

89

87

98

97

92

93,94

86

64

31

VDD

VSS

N.C.

DQa0~a 8

DQb0~b 8

VDDQ

VSSQ

Power Supply(+3.3V) 14,15,16,41,65,66,91

Ground

17,40,67,90

No Connect

1,2,3,6,7,25,28,29,30,

38,39,42,51,52,53,

56,57,75,78,79,95,96

Data Inputs/Outputs 58,59,62,63,68,69,72,73,74

Data Inputs/Outputs 8,9,12,13,18,19,22,23,24

Output Power Supply 4,11,20,27,54,61,70,77

(3.3V or 2.5V)

Output Ground

5,10,21,26,55,60,71,76

NOTE : A 0 and A1 are the two least significant bits(LSB) of the address field and set the internal burst counter if burst is desired.

- 5 - Nov. 2003

Rev 2.0

5 Page

K7N323601M

K7N321801M

1Mx36 & 2Mx18 Pipelined NtRAMTM

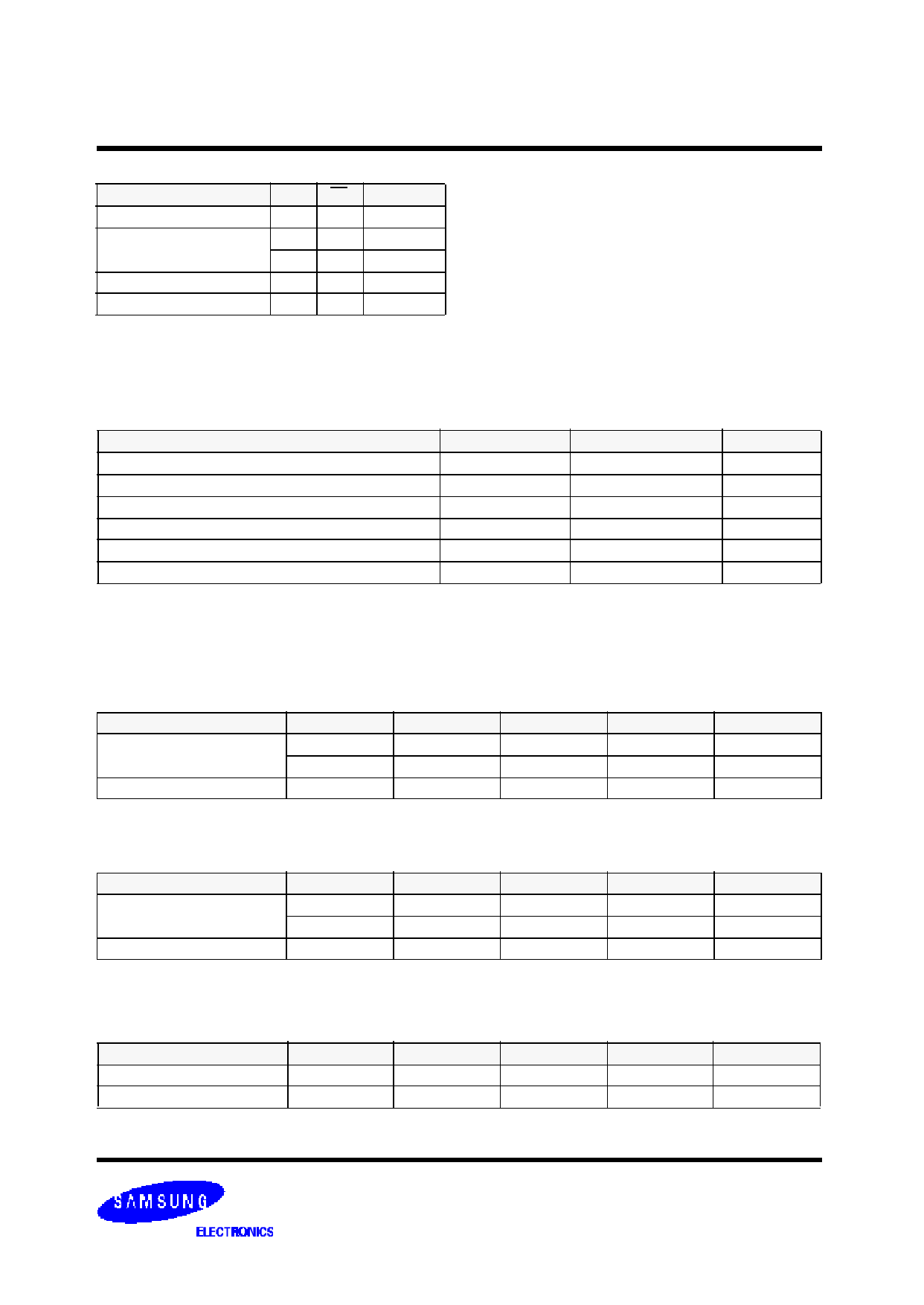

ASYNCHRONOUS TRUTH TABLE

OPERATION

Sleep Mode

Read

Write

Deselected

ZZ OE I/O STATUS

HX

High-Z

LL

DQ

LH

High-Z

L X Din, High-Z

LX

High-Z

Notes

1. X means "Don′t Care".

2. Sleep Mode means power Sleep Mode of which stand-by current does

not depend on cycle time.

3. Deselected means power Sleep Mode of which stand-by current

depends on cycle time.

ABSOLUTE MAXIMUM RATINGS*

PARAMETER

SYMBOL

RATING

UNIT

Voltage on VDD Supply Relative to VSS

VDD

-0.3 to 4.6

V

Voltage on Any Other Pin Relative to VSS

VIN

-0.3 to VDD+0.3

V

Power Dissipation

PD 1.6 W

Storage Temperature

TSTG

-65 to 150

°C

Operating Temperature

T OPR

0 to 70

°C

Storage Temperature Range Under Bias

TBIAS

-10 to 85

°C

*Note : Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only

and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not

implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

OPERATING CONDITIONS at 3.3V I/O(0°C ≤ TA ≤ 70°C)

PARAMETER

SYMBOL

MIN

Supply Voltage

VDD

VDDQ

3.135

3.135

Ground

VSS

0

Typ.

3.3

3.3

0

OPERATING CONDITIONS at 2.5V I/O(0°C ≤ TA ≤ 70°C)

PARAMETER

SYMBOL

MIN

Supply Voltage

VDD

VDDQ

3.135

2.375

Ground

VSS

0

Typ.

3.3

2.5

0

MAX

3.465

3.465

0

UNIT

V

V

V

MAX

3.465

2.9

0

UNIT

V

V

V

CAPACITANCE*(TA=25°C, f=1MHz)

Parameter

Symbol

Input Capacitance

CIN

Output Capacitance

C OUT

*Notes : Sampled not 100% tested.

Test Condition

VIN=0V

VOUT =0V

TYP

-

-

- 11 -

Max

5

7

Unit

pF

pF

Nov. 2003

Rev 2.0

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet DS_K7N323601M.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS_K7N323601M | 1Mx36 & 2Mx18-Bit Pipelined NtRAM | Samsung semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |