|

|

PDF X25097S-2.7 Data sheet ( Hoja de datos )

| Número de pieza | X25097S-2.7 | |

| Descripción | 5MHz Low Power SPI Serial E 2 PROM with IDLock TM Memory | |

| Fabricantes | Xicor | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de X25097S-2.7 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

8K

X25097

1024 x 8 Bit

5MHz Low Power SPI Serial E2PROM with IDLockTM Memory

FEATURES

• 5MHz Clock Rate

• IDLock™ Memory

—IDLock First or Last Page, any 1/4 or Lower 1/2

of E2PROM Array

• Low Power CMOS

—<1µA Standby Current

—<3mA Active Current during Write

—<400µA Active Current during Read

• 1.8V to 3.6V, 2.7V-5.5V or 4.5V to 5.5V Operation

• Built-in Inadvertent Write Protection

—Power-Up/Power-Down Protection Circuitry

—Write Enable Latch

—Write Protect Pin

• SPI Modes (0,0 & 1,1)

• 1024 x 8 Bits

—16 Byte Page Mode

• Self-Timed Write Cycle

—5ms Write Cycle Time (Typical)

• High Reliability

—Endurance: 100,000 Cycles/Byte

—Data Retention: 100 Years

—ESD: 2000V on all pins

• 8-Lead TSSOP Package

• 8-Lead SOIC Package

• 8-Lead PDIP Package

DESCRIPTION

The X25097 is a CMOS 8K-bit serial E2PROM, internally

organized as 1024 x 8. The X25097 features a Serial

Peripheral Interface (SPI) and software protocol

allowing operation on a simple four-wire bus. The bus

signals are a clock input (SCK) plus separate data in (SI)

and data out (SO) lines. Access to the device is

controlled through a chip select (CS) input, allowing any

number of devices to share the same bus.

IDLock is a programmble locking mechanism which

allows the user to lock system ID and parametric data in

different portions of the E2PROM memory space,

ranging from as little as one page to as much as 1/2 of

the total array. The X25097 also features a WP pin that

can be used for hardwire protection of the part, disabling

all write attempts, as well as a Write Enable Latch that

must be set before a write operation can be initiated.

The X25097 utilizes Xicor’s proprietary Direct WriteTM

cell, providing a minimum endurance of 100,000 cycles

per byte and a minimum data retention of 100 years.

FUNCTIONAL DIAGRAM

SI

SO

SCK

COMMAND

DECODE

AND

CONTROL

LOGIC

CS

X

DECODE

LOGIC

DATA REGISTER

Y DECODE LOGIC

16 8

64

8K E2PROM

ARRAY

(1024 x 8)

WP WRITE CONTROL LOGIC

©Xicor, Inc. 1994, 1995, 1996 Patents Pending

7034-1.1 5/8/97 T1/C0/D0 SH

1

HIGH VOLTAGE

CONTROL

7038 FRM F01

Characteristics subject to change without notice

1 page

X25097

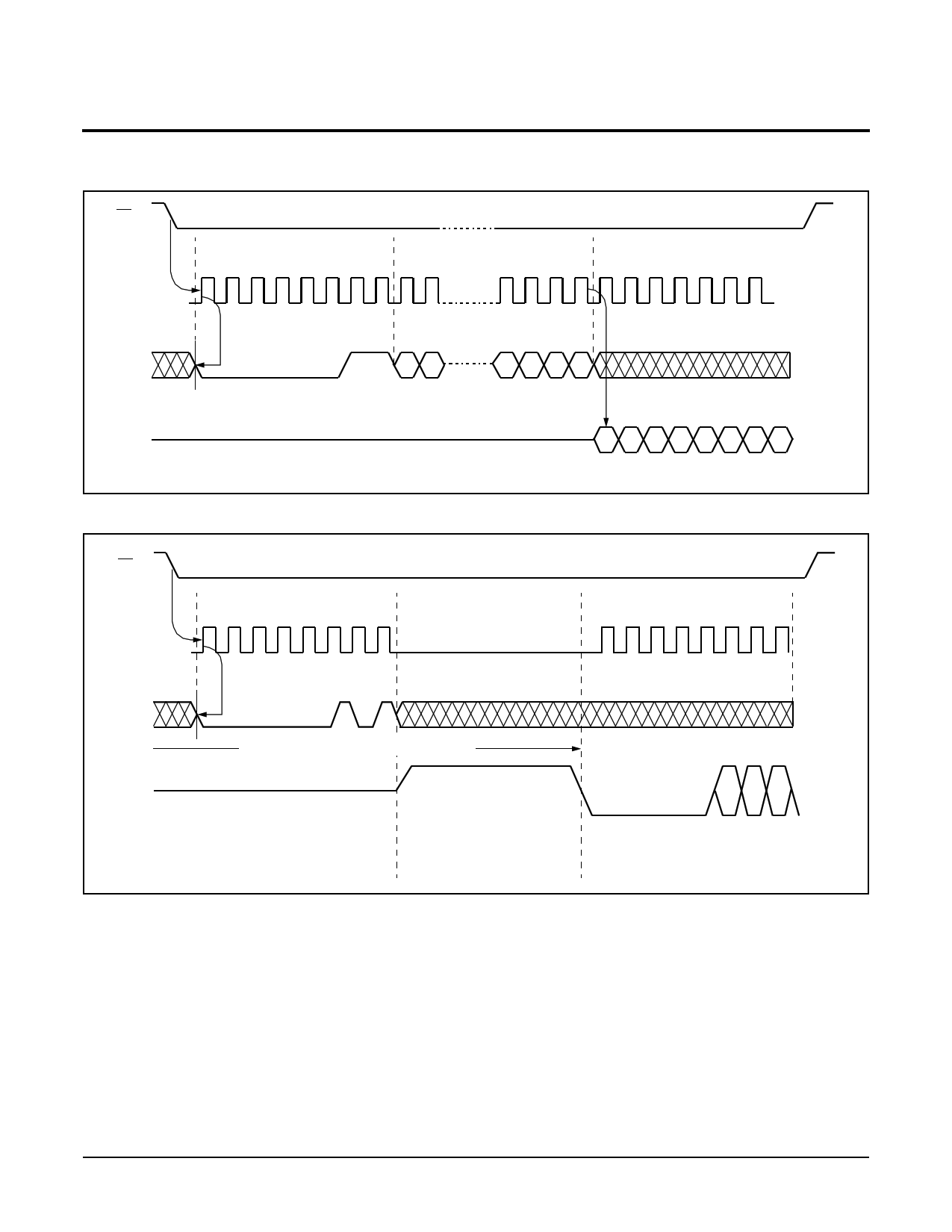

Figure 2. Read Operation Sequence

CS

SCK

SI

0123456789

20 21 22 23 24 25 26 27 28 29 30

READ INSTRUCTION

(1 BYTE)

BYTE ADDRESS (2 BYTE)

15 14

3210

DATA OUT

HIGH IMPEDANCE

SO

Figure 3. Read Status Operation Sequence

CS

SCK

SI

SO

01234567

READ STATUS

INSTRUCTION

NONVOLATILE WRITE IN PROGRESS

SO HIGH DURING

NONVOLATILE

WRITE CYCLE

76543210

7038 FRM F03.1

...

...

...I I I

D DD

L LL

2 10

SO = STATUS REG BIT

WHEN NO NONVOLATILE

WRITE CYCLE

7038 FRM F04.2

5

5 Page

X25097

Figure 9. Serial Input Timing

CS

SCK

SI

t LEAD

tSU t H

MSB IN

HIGH IMPEDANCE

SO

tCS

t LAG

tRI t FI

LSB IN

7005 FRM F11

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet X25097S-2.7.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| X25097S-2.7 | 5MHz Low Power SPI Serial E 2 PROM with IDLock TM Memory | Xicor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |