|

|

PDF TSW5070FNTR Data sheet ( Hoja de datos )

| Número de pieza | TSW5070FNTR | |

| Descripción | PROGRAMMABLE CODEC/FILTER COMBO 2ND GENERATION | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TSW5070FNTR (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

TS5070

TS5071

PROGRAMMABLE CODEC/FILTER

COMBO 2ND GENERATION

COMPLETE CODEC AND FILTER SYSTEM

INCLUDING :

– TRANSMIT AND RECEIVE PCM CHANNEL

FILTERS

– µ-LAW OR A-LAW COMPANDING CODER

AND DECODER

– RECEIVE POWER AMPLIFIER DRIVES

300 Ω

– 4.096 MHz SERIAL PCM DATA (max)

PROGRAMMABLE FUNCTIONS :

– TRANSMIT GAIN : 25.4 dB RANGE, 0.1 dB

STEPS

– RECEIVE GAIN : 25.4 dB RANGE, 0.1 dB

STEPS

– HYBRID BALANCE CANCELLATION FIL-

TER

– TIME-SLOT ASSIGNMENT: UP TO 64

SLOTS/FRAME

– 2 PORT ASSIGNMENT (TS5070)

– 6 INTERFACE LATCHES (TS5070)

– A OR µ-LAW

– ANALOG LOOPBACK

– DIGITAL LOOPBACK

DIRECT INTERFACE TO SOLID-STATE

SLICs

SIMPLIFIES TRANSFORMER SLIC, SINGLE

WINDING SECONDARY

STANDARD SERIAL CONTROL INTERFACE

80 mW OPERATING POWER (typ)

1.5mW STANDBY POWER (typ)

MEETS OR EXCEEDS ALL CCITT AND

LSSGR SPECIFICATIONS

TTL AND CMOS COMPATIBLE DIGITAL IN-

TERFACES

DESCRIPTION

The TS5070series are the second generationcom-

bined PCM CODEC and Filter devices optimized

for digital switching applications on subscriber and

trunk line cards.

Using advanced switched capacitor techniques the

TS5070 and TS5071 combine transmit bandpass

and receive lowpass channel filters with a com-

panding PCM encoder and decoder. The devices

are A-law and µ-law selectable and employ a con-

ventional serial PCM interface capable of being

clocked up to 4.096 MHz. A number of programma-

ble functions may be controlled via a serial control

port.

December 1997

DIP20 (Plastic)

ORDERING NUMBER:TS5071N

PLCC28

ORDERING NUMBERS: TS5070FN

TS5070FNTR

Channel gains are programmable over a 25.4 dB

range in each direction, and a programmable filter

is included to enable Hybrid Balancing to be ad-

justed to suit a wide range of loop impedance con-

ditions.

Both transformer and active SLIC interface circuits

with real or complex termination impedances can

be balanced by this filter, with cancellation in ex-

cess of 30 dB being readily achievable when meas-

ured across the passbandagainst standardtest ter-

mination networks.

To enable COMBO IIG to interface to the SLIC con-

trol leads, a number of programmable latches are

included ; each may be configured as either an in-

put or an output. The TS5070 provides 6 latches

and the TS5071 5 latches.

1/32

1 page

TS5070 - TS5071

TRANSMIT SECTION

Name

Pin

Type

TS5070

FN

TS5071

N

Function

FSX I 22 15 Transmit

Frame Sync.

Description

Normally a pulse or squarewave waveform with an 8 kHz

repetition rate is applied to this input to define the start of

the transmit time-slot assigned to this device (non-delayed

data mode) or the start of the transmit frame (delayed

data mode using the internal time-slot assignment

counter).

VFXI

I

28

20 Transmit

Analog

This is a high–impedance input. Voice frequency signals

present on this input are encoded as an A–law or µ–law

PCM bit stream and shifted out on the selected DX pin.

DX0 0 18 13 Transmit Data DX1 is available on the TS5070 only, DX0 is available on

DX1 0

19

–

all devices. These transmit data TRI–STATE® outputs

remain in the high impedance state except during the

assigned transmit time–slot on the assigned port, during

which the transmit PCM data byte is shifted out on the

rising edges of BCLK.

TSX0

0

20

14 Transmit

TSX1 is available on the TS5070 only.

TSX1

0

21

– Time–slot

TSX0 is available on all devices. Normally these opendrain

outputs are floating in a high impedance state except

when a time–slot is active on one of the DX outputs, when

the apppropriate TSX output pulls low to

enable a backplane line–driver. Should be strapped to

ground (GND) when not used.

RECEIVE SECTION

Name

Pin

Type

TS5070

FN

TS5071

N

Function

Description

FSR I

8

6 Receive Frame Normally a pulse or squarewave waveform with an 8 kHz

Sync.

repetition rate is applied to this input to define the start of

the receive time–slot assigned to this device (non-delayed

frame mode) or the start of the receive frame (delayed

frame mode using the internal time-slot assignment

counter.

VFR0

0

2

2 Receive Analog The receive analog power amplifier output, capable of

driving load impedances as low as 300 Ω (depending on

the peak overload level required). PCM data received on

the assigned DR pin is decoded and appears at this output

as voice frequency signals.

DR0 I

DR1 I

10

9

7 Receive Data DR1 is available on the TS5070 only, DR0 is available on

– all devices. These receive data input(s) are inactive

except during the assigned receive time–slot of the

assigned port when the receive PCM data is shifted in on

the falling edges of BCLK.

5/32

5 Page

Alternatively, the internal time-slot assignment

counters and comparators can be used to access

any time-slot in a frame,using the framesync inputs

as marker pulses for the beginning of transmit and

receive time-slot 0. In this mode, a frame may con-

sist of up to 64 time-slots of 8 bits each. A time-slot

is assignedby a 2-byte instructionas shown in table

1 and 6. The last 6 bits of the second byte indicate

the selected time-slot from 0-63 using straight bi-

nary notation. A new assignment becomes active

on the second frame following the end of the Chip

Select for the second control byte. The ”EN” bit al-

lows the PCM inputs DR0/1 or outputs DX0/1 as ap-

propriate, to be enabled or disabled.

Time-Slot Assignment mode requires that the FSX

and FSR pulses must conformto the delayedtiming

format shown in figure 6.

PORT SELECTION

On the TS5070 only, an additional capability is

available : 2 Transmit serial PCM ports, DX0 and

DX1, and 2 receive serial PCM ports, DR0 and DR1,

are provided to enable two-way space switching to

be implemented. Port selections for transmit and

receive are made within the appropriate time-slot

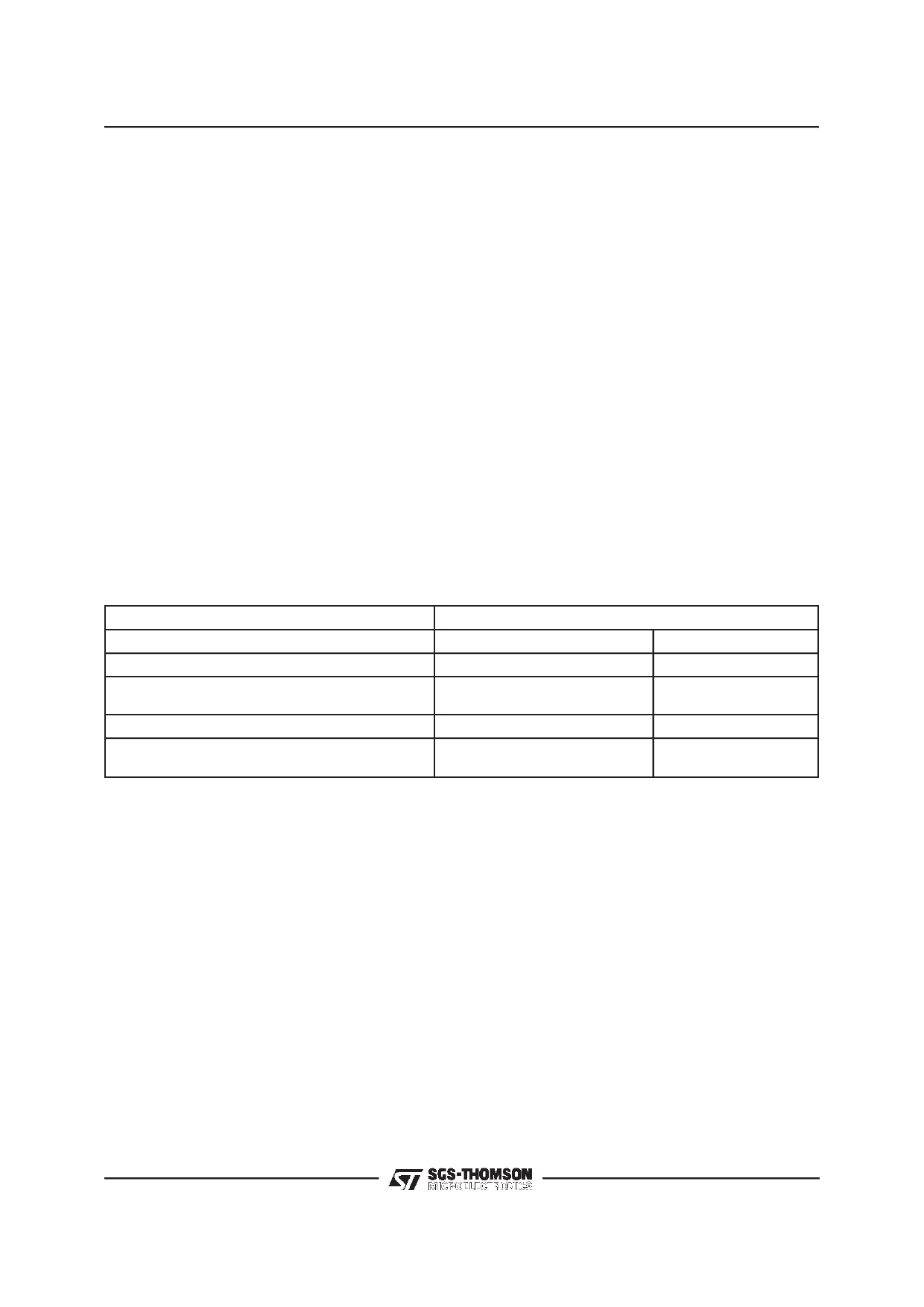

Table 7: Byte 2 of Transmit Gain Instructions.

Bit Number

76543210

00000000

00000001

00000010

10111111

11111110

11111111

(*) State at power initialization

RECEIVE GAIN INSTRUCTION BYTE 2

The receive gain can be programmed in 0.1 dB

steps by writing to the Receive GainRegister as de-

fined in table 1 and 8. Note the following restriction

on output drive capability :

a) 0 dBm0 levels ≤ 8.1dBm at VFRO may be

driven into a load of ≥ 15 kΩ to GND,

b) 0 dBm0 levels ≤ 7.6dBm at VFRO may be

driven into a load of ≥ 600 Ω to GND,

c) 0 dBm levels ≤ 6.9dBm at VFRO may be driven

TS5070 - TS5071

assignmentinstruction using the ”PS” bit in the sec-

ond byte.

On the TS5071, only ports DX0 and DR0 are avail-

able, therefore the ”PS” bit MUST always be set to

0 for these devices.

Table 6 shows the format for the second byte of

both transmitand receive time-slot and port assign-

ment instructions.

TRANSMIT GAIN INSTRUCTION BYTE 2

The transmit gain can be programmed in 0.1 dB

steps by writing to the Transmit Gain Register as

defined in tables 1 and 7. This corresponds to a

range of 0 dBm0 levels at VFXI between 1.619

Vrms and 0.087 Vrms (equivalent to + 6.4 dBm to

– 19.0 dBm in 600 Ω).

To calculate the binary code for byte 2 of this in-

struction for any desired input 0 dBm0 level in

Vrms, take the nearest integer to the decimal

number given by :

200 X log10 (V/√6 ) + 191

and convert to the binary equivalent. Some exam-

ples are given in table 7.

0dBm0 Test Leve at VFXI

In dBm (Into 600Ω)

In Vrms (approx.)

No Output

– 19

– 18.9

0.087

0.088

0 0.775

+6.3

+6.4

1.60

1.62

into a load of ≥ 300 Ω to GND.

To calculate the binary code for byte 2 of this in-

struction for any desired output 0 dBm0 level in

Vrms, take the nearest integer to the decimal num-

ber given by :

a 200 X log10 (V/√6 ) + 174

n

d convert to the binary equivalent. Some exam-

ples are given in table 8.

11/32

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet TSW5070FNTR.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TSW5070FNTR | PROGRAMMABLE CODEC/FILTER COMBO 2ND GENERATION | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |