|

|

PDF TS68020MR25 Data sheet ( Hoja de datos )

| Número de pieza | TS68020MR25 | |

| Descripción | HCMOS 32-bit Virtual Memory Microprocessor | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TS68020MR25 (archivo pdf) en la parte inferior de esta página. Total 45 Páginas | ||

|

No Preview Available !

Features

• Object Code Compatible with Earlier TS68000 Microprocessors

• Addressing Mode Extensions for Enhanced Support of High Level Languages

• New Bit Field Data Type Accelerates Bit-oriented Application, i.e. Video Graphics

• Fast on-chip Instruction Cache Speed Instructions and Improves Bus Bandwidth

• Co-processor Interface to Companion 32-bit Peripherals: TS68881 and TS68882

Floating Point Co-processors

• Pipelined Architecture with High Degree of Internal Parallelism Allowing Multiple

Instructions to be Executed Concurrently

• High Performance Asynchronous Bus in Non-multiplexed and Full 32 Bits

• Dynamic Bus Sizing Efficiently Supports 8-, 16-, 32-bit Memories and Peripherals

• Full Support of Virtual Memory and Virtual Machine

• Sixteen 32-bit General-purpose Data and Address Registers

• Two 32-bit Supervisor Stack Pointers and 5 Special Purpose Control Registers

• 18 Addressing Modes and 7 Data Types

• 4-Gbyte Direct Addressing Range

• Processor Speed: 16.67 MHz - 20 MHz - 25 MHz

• Power Supply: 5.0 VDC ± 10%

Description

The TS68020 is the first full 32-bit implementation of the TS68000 family of micropro-

cessors. Using HCMOS technology, the TS68020 is implemented with 32-bit registers

and data paths, 32-bit addresses, a rich instruction set, and versatile addressing

modes.

HCMOS 32-bit

Virtual Memory

Microprocessor

TS68020

Screening/Quality

This product is manufactured in full compliance with either:

• MIL-STD-883 (class B)

• DESC 5962 - 860320

• or according to Atmel standards

See “Ordering Information” on page 43.

Pin connection: see page 3.

R suffix

PGA 114

Ceramic Pin Grid Array

F suffix

CQFP 132

Ceramic Quad Flat Pack

Rev. 2115A–HIREL–07/02

1

1 page

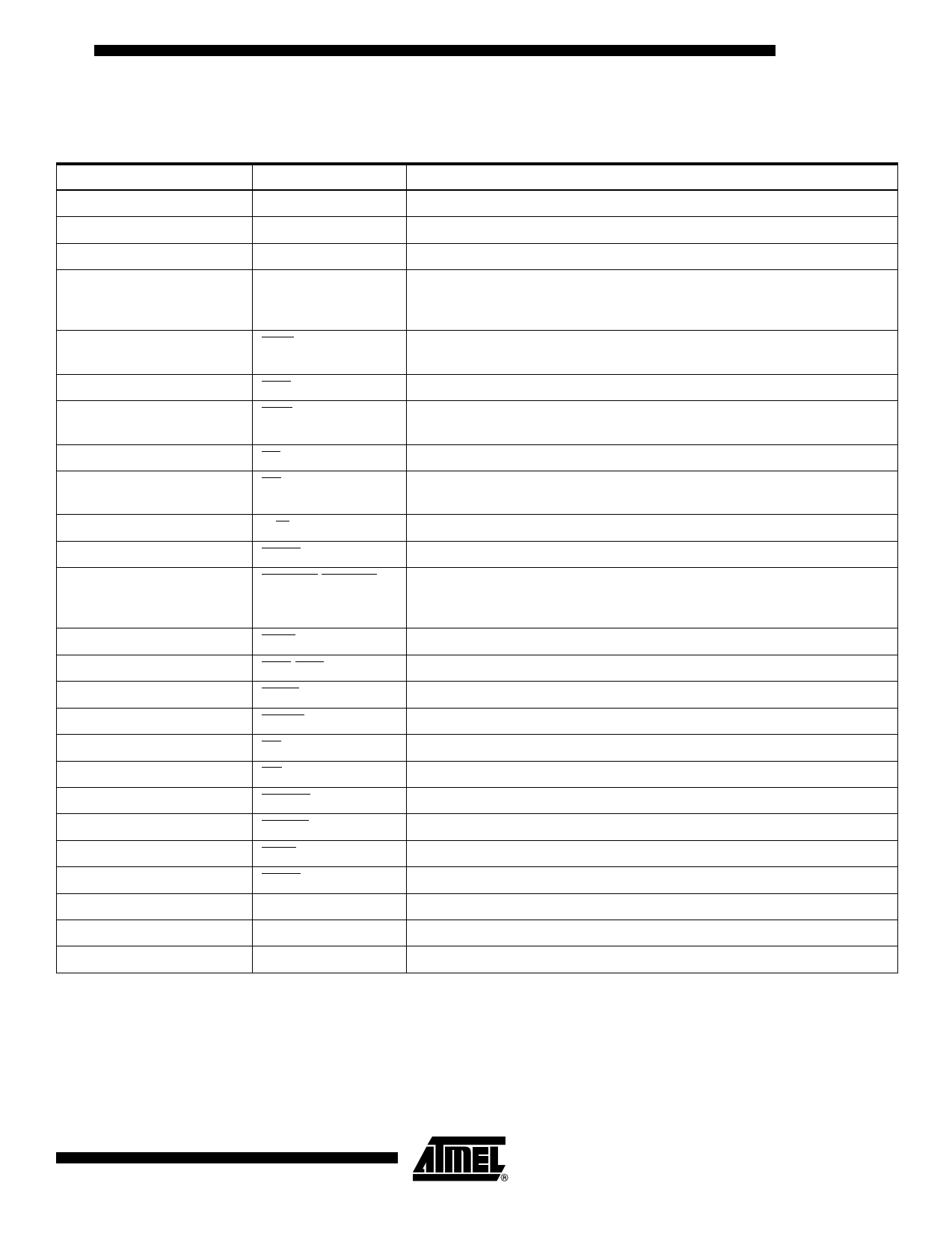

TS68020

Table 1. Signal Index

Signal Name

Address Bus

Data Bus

Function Codes

Size

Read-Modify-Write Cycle

External Cycle Start

Operand Cycle Start

Address Strobe

Data Strobe

Read/Write

Data Buffer Enable

Data Transfer and Size

Acknowledge

Cache Disable

Interrupt Priority Level

Autovector

Interrupt Pending

Bus Request

Bus Grant

Bus Grant Acknowledge

Reset

Halt

Bus Error

Clock

Power Supply

Ground

Mnemonic

A0-A31

D0-D31

FC0-FC2

SIZ0/SIZ1

RMC

ECS

OCS

AS

DS

R/W

DBEN

DSACK0/DSACK1

CDIS

IPL0-IPL2

AVEC

IPEND

BR

BG

BGACK

RESET

HALT

BERR

CLK

VCC

GND

Function

32-bit Address Bus Used to address any of 4, 294, 967, 296 bytes.

32-bit Data Bus Used to Transfer 8, 16, 24 or 32 bits of Data Per Bus Cycle.

3-bit Function Case Used to Identify the Address Space of Each Bus Cycle.

Indicates the Number of Bytes Remaining to be Transferred for this Cycle.

These Signals, Together with A0 And A1, Define the Active Sections of the

Data Bus.

Provides an Indicator that the Current Bus Cycle is Part of an Indivisibleread-

modify-write Operation.

Provides an Indication that a Bus Cycle is Beginning.

Identical Operation to that of ECS Except that OCS Is Asserted Only During

the First Bus Cycle of an Operand Transfer.

Indicates that a Valid Address is on The Bus.

Indicates that Valid Data is to be Placed on the Data Bus by an External

Device or has been Laced on the Data Bus by the TS68020.

Defines the Bus Transfer as an MPU Read or Write.

Provides an Enable Signal for External Data Buffers.

Bus Response Signals that Indicate the Requested Data Transfer Operation

is Completed. In Addition, these Two Lines Indicate the Size of the External

Bus Port on a Cycle-by-cycle Basis.

Dynamically Disables the On-chip Cache to Assist Emulator Support.

Provides an Encoded Interrupt Level to the Processor.

Requests an Autovector During an Interrupt Acknowledge Cycle.

Indicates that an Interrupt is Pending.

Indicates that an External Device Requires Bus Mastership.

Indicates that an External Device may Assume Bus Mastership.

Indicates that an External Device has Assumed Bus Mastership.

System Reset.

Indicates that the Processor Should Suspend Bus Activity.

Indicates an Invalid or Illegal Bus Operation is Being Attempted.

Clock Input to the Processor.

+5-volt ± 10% Power Supply.

Ground Connection.

2115A–HIREL–07/02

5

5 Page

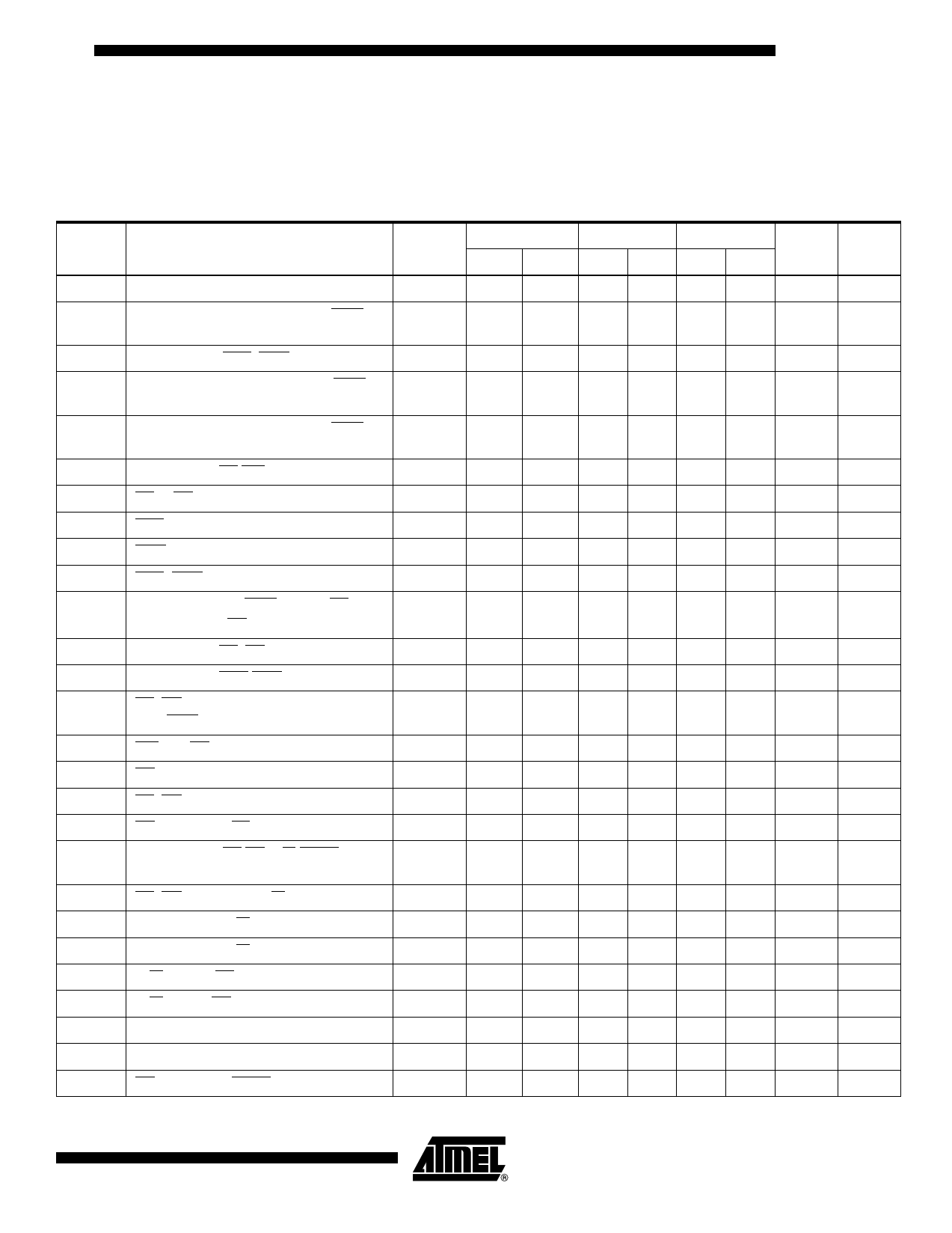

TS68020

Dynamic (Switching)

Characteristics

The limits and values given in this section apply over the full case temperature range -

55°C to +125°C and VCC in the range 4.5V to 5.5V VIL = 0.5V and VIH = 2.4V (See also

note 12 and 13). The INTERVAL numbers refer to the timing diagrams. See Figure 5,

Figure 9 and Figure 12.

Table 6. Dynamic Electrical Characteristics

Symbol

tCPW

tCHAV

tCHEV

tCHAZX

tCHAZn

tCLSA

tSTSA

tECSA

tOCSA

tEOCSN

tAVSA

tCLSN

tCLEN

tSNAI

tSWA

tSWAW

tSN

tSNSA

tCSZ

tSNRN

tCHRH

tCHRL

tRAAA

tRASA

tCHDO

tSNDI

tDNDBN

Parameter

Clock Pulse Width

Clock High to Address/FC/Size/RMC

Valid

Clock High to ECS, OCS Asserted

Clock High to Address/Data/FC/RMC/

Size High Impedance

Clock High to Address/FC/Size/RMC

Invalid

Clock Low to AS, DS Asserted

AS to DS Assertion (Read)(Skew)

ECS Width Asserted

OCS Width Asserted

ECS, OCS Width Negated

Address/FC/Size/RMC Valid to AS

Asserted (and DS Asserted, Read)

Clock Low to AS, DS Negated

Clock Low to ECS/OCS Negated

AS, DS Negated to Address/FC/

Size/RMC Invalid

AS (and DS, Read) Width Asserted

DS Width Asserted, Write

AS, DS Width Negated

DS Negated to AS Asserted

Clock High to AS/DS/R/W/DBEN High

Impedance

AS, DS Negated to R/W High

Clock High to R/W High

Clock High to R/W Low

R/W High to AS Asserted

R/W Low to DS Asserted (Write)

Clock High to Data Out Valid

AS, DS Negated to Data Out Valid

DS Negated to DBEN Negated (Write)

Interval

Number

2,3

6

68020-16

Min Max

24 95

0 30

68020-20

Min Max

20 54

0 25

68020-25

Min Max

19 61

0 25

6A 0 20 0 15 0 12

7 0 60 0 50 0 40

80

00

9 3 30 3 25 3 18

9A -15 15 -10 10 -10 10

10 20

15 15

10A 20

15 15

10B 15

10 5

11 15

10 6

12 0 30 0 25 0 15

12A 0 30 0 25 0 15

13 15

10 10

14 100

85 70

14A 40

38 30

15 40

38 30

15A 35

30 25

16 60 50 40

17 15

10 10

18 0 30 0 25 0 20

20 0 30 0 25 0 20

21 15

10 5

22 75

60 50

23 30 25 25

25 15

10 5

25A 15

10 5

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Notes

(11)

(1)

(11)

(6)

(11)

(8)

(11)

(6)

(6)

(6)

(6)

(9)

2115A–HIREL–07/02

11

11 Page | ||

| Páginas | Total 45 Páginas | |

| PDF Descargar | [ Datasheet TS68020MR25.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TS68020MR20 | HCMOS 32-bit Virtual Memory Microprocessor | ATMEL Corporation |

| TS68020MR25 | HCMOS 32-bit Virtual Memory Microprocessor | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |