|

|

PDF TS68230 Data sheet ( Hoja de datos )

| Número de pieza | TS68230 | |

| Descripción | HMOS PARALLEL INTERFACE/TIMER | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de TS68230 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

TS68230

HMOS PARALLEL INTERFACE/TIMER

.. TS68000 BUS COMPATIBLE

PORT MODES INCLUDE :

BIT I/O

UNIDIRECTIONAL 8 BIT AND 16 BIT

BIDIRECTIONAL 8 BIT AND 16 BIT

. PROGRAMMABLE HANDSHAKING OPTIONS

. 24-BIT PROGRAMMABLE TIMER MODES

. FIVE SEPARATE INTERRUPT VECTORS

. SEPARATE PORT AND TIMER INTERRUPT

SERVICE REQUESTS

. REGISTERS ARE READ/WRITE AND DIRECT-

LY ADDRESSABLE

. REGISTERS ARE ADDRESSED FOR MOVEP

(Move Peripheral) AND DMAC COMPATIBILITY

1

P

(PDIP48)

FN

(PLCC52)

DESCRIPTION

The TS68230 parallel interface/timer (PI/T) provides

versatile double buffered parallel interfaces and a

system oriented timer for TS68000 systems. The pa-

rallel interfaces operate in unidirectional or bidirectio-

nal modes, either 8 or 16 bits wide. In the

unidirectional modes, an associated data direction

register determines whether each port pin is an input

or output. In the bidirectional modes the data direc-

tion registers are ignored and the direction is deter-

mined dynamically by the state of four handshake

pins. These programmable handshake pins provide

an interface flexible enough for connection to a wide

variety of low, medium, or high speed peripherals or

other computer systems. The PI/T ports allow use of

vectored or auto-vectored interrupts, and also pro-

vide a DMA request pin for connection to the 68440

direct memory access controller (DMAC) or a similar

circuit. The PI/T timer contains a 24-bit wide counter

and a 5-bit prescaler. The timer may be clocked by

the system clock (PI/T CLK pin) or by an external

clock (TIN pin), and a 5-bit prescaler can be used. It

can generate periodic interrupts, a square wave, or

a single interrupt after a programmed time period. It

can also be used for elapsed time measurement or

as a device watchdog.

January 1989

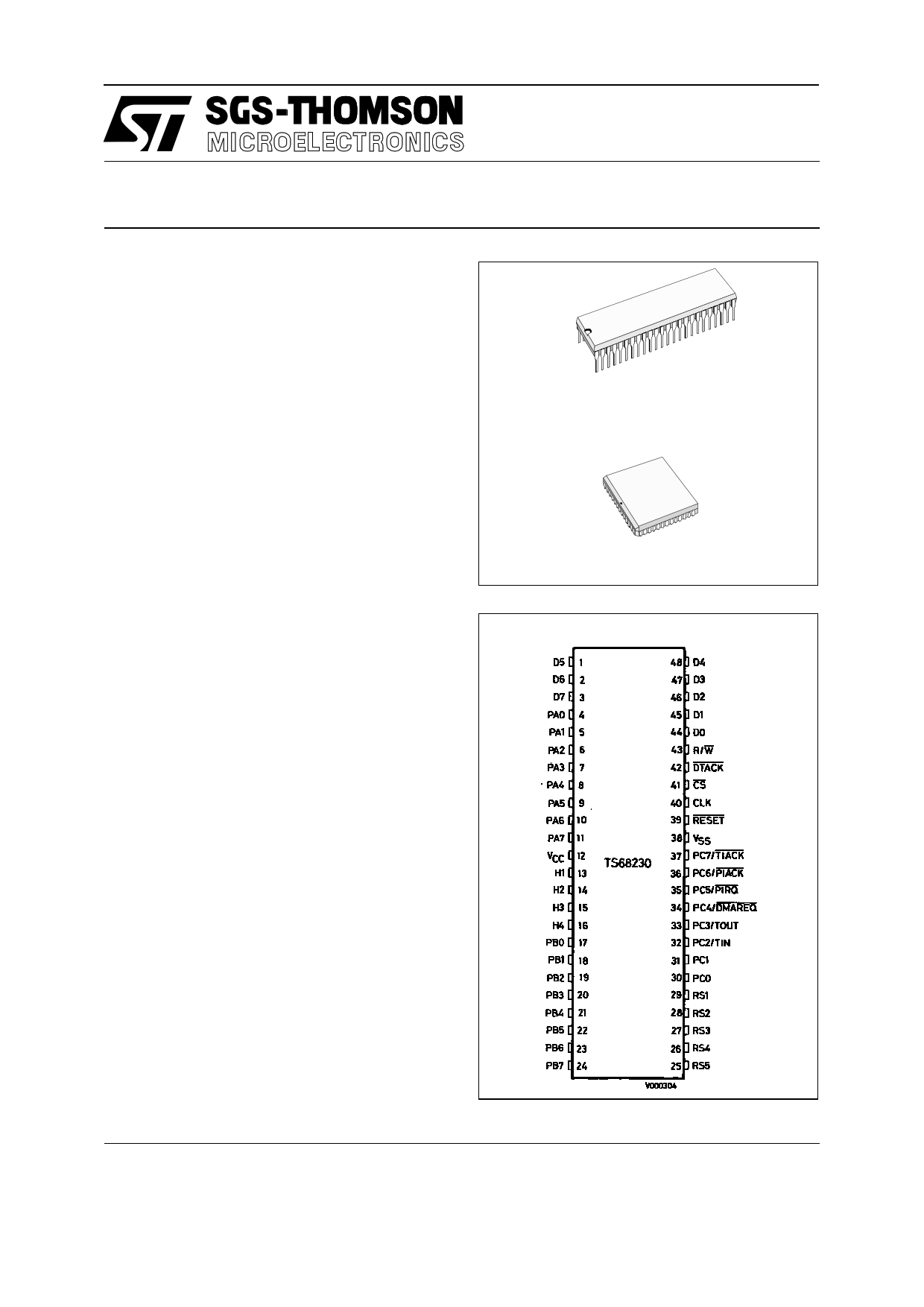

PIN CONNECTIONS

1/61

1 page

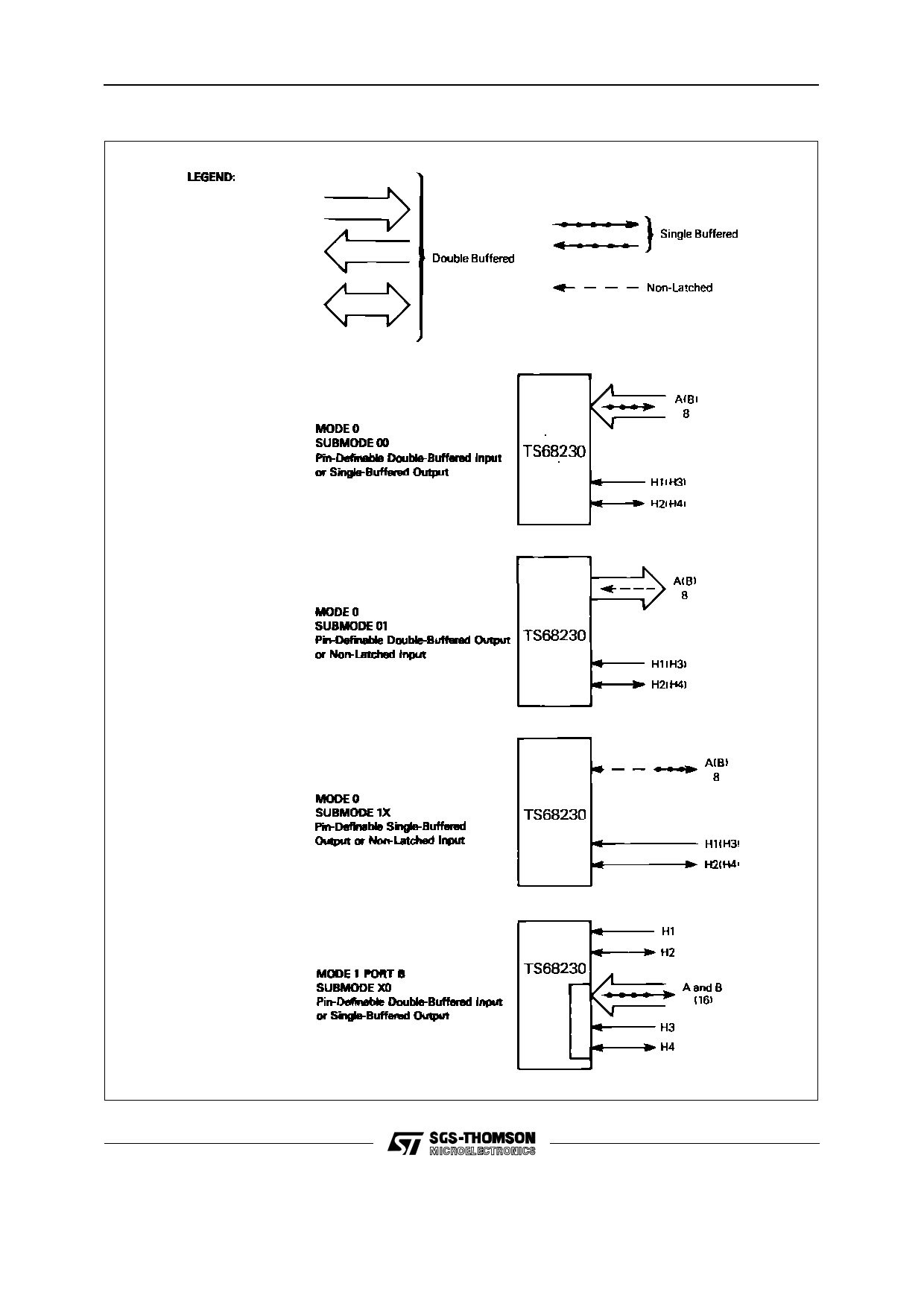

Figure 1.2 : Port Mode Layout.

TS68230

5/61

5 Page

TS68230

1.4. BUS INTERFACE OPERATION

The PI/T has an asynchronous bus interface prima-

rily designed for use with an TS68000 microproces-

sor. With care, however, it can be connected to syn-

chronous microprocessor buses. This section

completely describes the PI/T’s bus interface, and is

intended for the asynchronous bus designer unless

otherwise mentioned.

In an asynchronous system the PI/T clock may ope-

rate at a significantly different frequency, either hi-

gher or lower, than the bus master and other system

components, as long as all bus specifications are

met. The TS68230 CLK pin has the same specifica-

tions as the TS68000 CLK pin, and must not be ga-

ted off at any time.

The following signals generate normal read and

write cycles to the PI/T : CS (chip select), R/W

(read/write), RS1-RS5(five register select bits), D0-

D7 (the 8-bit bidirectional data bus), and DTACK

(data transfer acknowledge). To generate interrupt

acknowledge cycles, PC6/PIACK or PC7/TIACK is

used instead of CS, and the register select pins are

ignored. No combination of the following pin func-

tions may be asserted simultaneously : CS, PIACK,

or TIACK.

1.4.1. READ CYCLES. This category includes all re-

gister reads, except port or timer interrupt acknow-

ledge cycles. When CS is asserted, the register se-

lect and R/W inputs are latched internally. They

must meet small setup and hold time requirements

with respect to the asserted edge of CS. (Refer to

6.6 AC Electrical Specifications for further infor-

mation). The PI/T is not protected against aborted

(shortened) bus cycles generated by an address er-

ror or bus error exception in which it is addressed.

Certain operations triggered by normal read (or

write) bus cycles are not complete within the time al-

lotted to the bus cycle. One example is transfers

to/from the double-buffered latches that occur as a

result of the bus cycle. If the bus master’s clock is

significan-tly faster than the PI/T’s the possibility

exists that, following the bus cycle, CS can be ne-

gated then re-asserted before completion of these

internal operations. In this situation the PI/T does not

recognize the re-assertion of CS until these opera-

tions are complete. Only at that time does it begin

the internal sequencing necessary to react to the as-

serted CS. Since CS also controls the DTACK re-

sponse, this "bus cycle recovery time" can be rela-

ted to the clock edge on which DTACK is asserted

for that cycle. The PI/T will recognize the sub-

sequent assertion of CS three clock periods after the

clock edge on which DTACK was previously asser-

ted.

The register select and R/W inputs pass through an

internal latch that is transparent when the PI/T can

recognize a new CS pulse (see above paragraph).

Since the internal data bus of the PI/T is conti-

nuously engaged for read transfers, the read access

time (to the data bus buffers) begins when the regis-

ter selects are stabilized internally. Also, when the

PI/T is ready to begin a new bus cycle, the assertion

of CS enables the data bus buffers within a short

propagation delay. This does not contribute to the o-

verall read access time unless CS is asserted signi-

ficantly after the register select and R/W inputs are

stabilized (as may occur with synchronous bus

microprocessors).

In addition to the chip select’s previously mentioned

duties, it controls the assertion of DTACK and lat-

ching of read data at the data bus interface. Except

for controlling input latches and enabling the data

bus buffers, all of these functions occur only after CS

has been recognized internally and synchronized

with the internal clock. Chip select is recognized on

the falling edge of the clock if the setup time is met

; DTACK is asserted (low) on the next falling edge

of the clock. Read data is latched at the PI/T’s data

bus interface at the same time DTACK is asserted.

It is stable as long as chip select remains asserted

independent of other external conditions.

From the above discussion it is clear that if the chip

select setup time prior to the falling edge of the clock

is met, the PI/T can consistently respond to a new

read or write bus cycle every four clock cycles. This

fact is especially useful in designing the PI/T’s clock

in synchronous bus systems not using DTACK. (An

extra clock period is required in interrupt acknow-

ledge cycles, see 1.4.2 Interrupt Acknowledge

Cycles).

In asynchronous bus systems in which the PI/T’s

clock differs from that of the bus master, generally

there is no way to guarantee that the chip select se-

tup time with respect to the PI/T clock is met. Thus,

the only way to determine that the PI/T recognized

the assertion of CS is to wait for the assertion of

DTACK. In this situation, all latched bus inputs to the

PI/T must be held stable until DTACK is asserted.

These include register select, R/W, and write data

inputs (see below).

System specifications impose a maximum delay

from the trailing (negated) edge of CS to the negated

edge of DTACK. As system speeds increase this be-

comes more difficult to meet with a simple pullup re-

sistor tied to the DTACK line. Therefore, the PI/T

provides an internal active pullup device to reduce

the rise time, and a level-sensitive circuit that later

turns this device off. DTACK is negated asynchro-

nously as fast as possible following the rising edge

11/61

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet TS68230.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TS68230 | HMOS PARALLEL INTERFACE/TIMER | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |