|

|

PDF PALCE22V10Z-25PC Data sheet ( Hoja de datos )

| Número de pieza | PALCE22V10Z-25PC | |

| Descripción | 24-Pin EE CMOS (Zero Power) Versatile PAL Device | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de PALCE22V10Z-25PC (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

PALCE22V10 COM'L: H-5/7/10/15/25,Q-10/15/25 IND: H-10/15/20/25

PALCE22V10Z COM'L: -25

IND: -15/25

PALCE22V10 and PALCE22V10Z

Families

24-Pin EE CMOS (Zero Power) Versatile PAL Device

DISTINCTIVE CHARACTERISTICS

x As fast as 5-ns propagation delay and 142.8 MHz fMAX (external)

x Low-power EE CMOS

x 10 macrocells programmable as registered or combinatorial, and active high or active low to

match application needs

x Varied product term distribution allows up to 16 product terms per output for complex

functions

x Peripheral Component Interconnect (PCI) compliant (-5/-7/-10)

x Global asynchronous reset and synchronous preset for initialization

x Power-up reset for initialization and register preload for testability

x Extensive third-party software and programmer support

x 24-pin SKINNY DIP, 24-pin SOIC, and 28-pin PLCC

x 5-ns and 7.5-ns versions utilize split leadframes for improved performance

GENERAL DESCRIPTION

The PALCE22V10 provides user-programmable logic for replacing conventional SSI/MSI gates and

flip-flops at a reduced chip count.

The PALCE22V10Z is an advanced PAL® device built with zero-power, high-speed, electrically-

erasable CMOS technology. It provides user-programmable logic for replacing conventional zero-

power CMOS SSI/MSI gates and flip-flops at a reduced chip count.

The PALCE22V10Z provides zero standby power and high speed. At 30 µA maximum standby

current, the PALCE22V10Z allows battery-powered operation for an extended period.

The PAL device implements the familiar Boolean logic transfer function, the sum of products. The

PAL device is a programmable AND array driving a fixed OR array. The AND array is programmed

to create custom product terms, while the OR array sums selected terms at the outputs.

The product terms are connected to the fixed OR array with a varied distribution from 8 to16 across

the outputs (see Block Diagram). The OR sum of the products feeds the output macrocell. Each

macrocell can be programmed as registered or combinatorial, and active-high or active low. The

output configuration is determined by two bits controlling two multiplexers in each macrocell.

Publication# 16564 Rev: E

Amendment/0

Issue Date: November 1998

1 page

Note that preset and reset control the flip-flop, not the output pin. The output level is determined

by the output polarity selected.

Power-Up Reset

All flip-flops power up to a logic LOW for predictable system initialization. Outputs of the

PALCE22V10 will depend on the programmed output polarity. The VCC rise must be monotonic,

and the reset delay time is 1000ns maximum.

Register Preload

The register on the PALCE22V10 can be preloaded from the output pins to facilitate functional

testing of complex state machine designs. This feature allows direct loading of arbitrary states,

making it unnecessary to cycle through long test vector sequences to reach a desired state. In

addition, transitions from illegal states can be verified by loading illegal states and observing

proper recovery.

Security Bit

After programming and verification, a PALCE22V10 design can be secured by programming the

security EE bit. Once programmed, this bit defeats readback of the internal programmed pattern

by a device programmer, securing proprietary designs from competitors. When the security bit is

programmed, the array will read as if every bit is erased, and preload will be disabled.

The bit can only be erased in conjunction with erasure of the entire pattern.

Programming and Erasing

The PALCE22V10 can be programmed on standard logic programmers. It also may be erased to

reset a previously configured device back to its unprogrammed state. Erasure is automatically

performed by the programming hardware. No special erase operation is required.

Quality and Testability

The PALCE22V10 offers a very high level of built-in quality. The erasability of the device provides

a direct means of verifying performance of all AC and DC parameters. In addition, this verifies

complete programmability and functionality of the device to provide the highest programming

yields and post-programming functional yields in the industry.

Technology

The high-speed PALCE22V10 is fabricated with Vantis’ advanced electrically erasable (EE) CMOS

process. The array connections are formed with proven EE cells. Inputs and outputs are designed

to be compatible with TTL devices. This technology provides strong input clamp diodes, output

slew-rate control, and a grounded substrate for clean switching.

PCI Compliance

The PALCE22V10H devices in the -5/-7/-10 speed grades are fully compliant with the PCI Local

Bus Specification published by the PCI Special Interest Group. The PALCE22V10H’s predictable

timing ensures compliance with the PCI AC specifications independent of the design.

Zero-Standby Power Mode

The PALCE22V10Z features a zero-standby power mode. When none of the inputs switch for an

extended period (typically 50 ns), the PALCE22V10Z will go into standby mode, shutting down

PALCE22V10 and PALCE22V10Z Families

5

5 Page

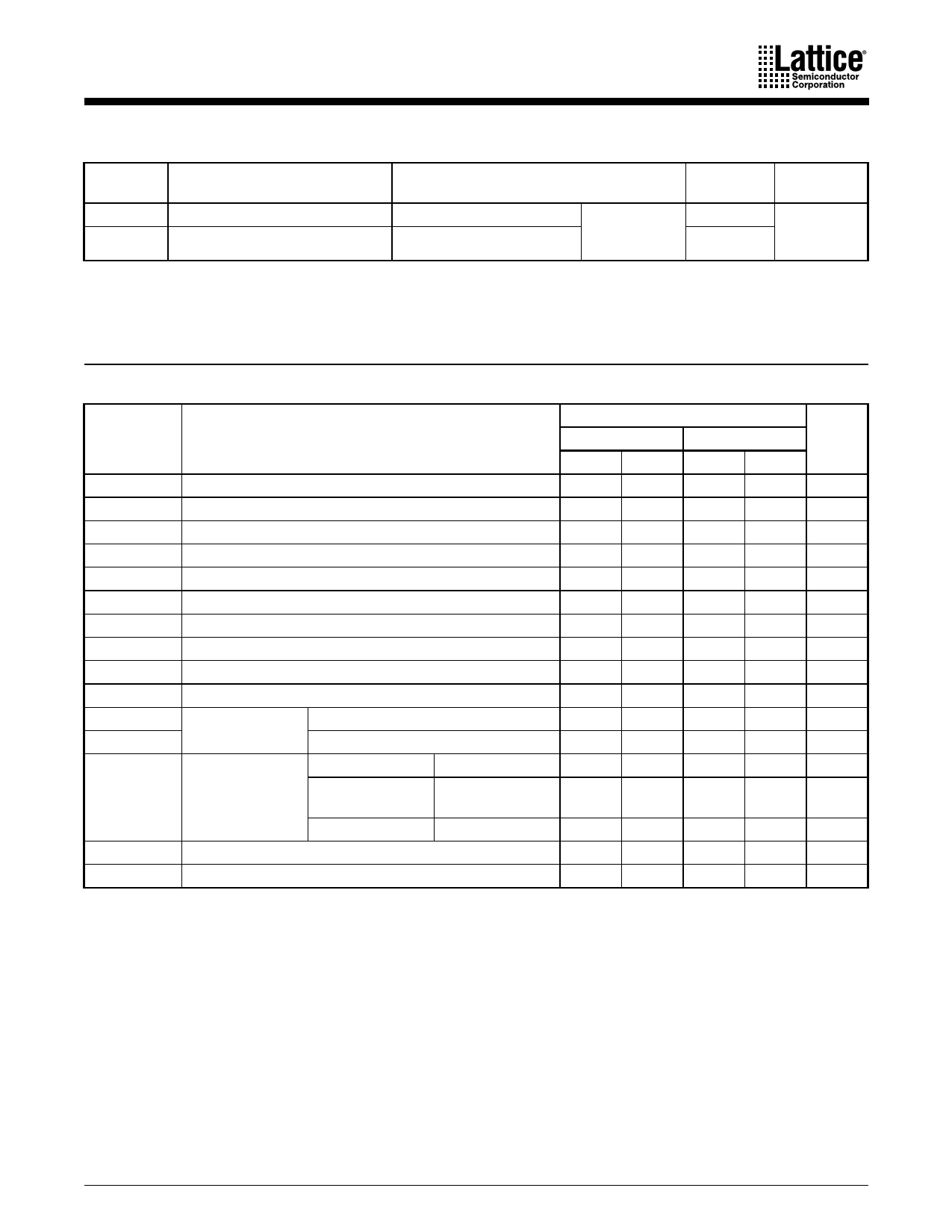

CAPACITANCE 1

Parameter

Symbol

Parameter Description

CIN Input Capacitance

COUT Output Capacitance

VIN = 2.0 V

VOUT = 2.0 V

Test Conditions

VCC = 5.0 V

TA = 25°C

f = 1 MHz

Typ Unit

5

pF

8

Note:

1. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modified where

capacitance may be affected.

SWITCHING CHARACTERISTICS OVER COMMERCIAL OPERATING RANGES 1

Parameter

Symbol

tPD

tS1

tS2

tH

tCO

tSKEWR

tAR

tARW

tARR

tSPR

tWL

tWH

fMAX

tEA

tER

Parameter Description

Input or Feedback to Combinatorial Output

Setup Time from Input or Feedback

Setup Time from SP to Clock

Hold Time

Clock to Output

Skew Between Registered Outputs (Note 2)

Asynchronous Reset to Registered Output

Asynchronous Reset Width

Asynchronous Reset Recovery Time

Synchronous Preset Recovery Time

Clock Width

LOW

HIGH

External Feedback

1/(tS + tCO)

Maximum Frequency Internal Feedback

(Note 3)

(fCNT)

1/(tS + tCF) (Note 4)

No Feedback

1/(tWH + tWL)

Input to Output Enable Using Product Term Control

Input to Output Disable Using Product Term Control

-7

PDIP PLCC

Min Max Min Max

3 7.5 3 7.5

5 4.5

66

00

2 5 2 4.5

11

10 10

77

77

77

3.5 3.0

3.5 3.0

100 111

125 133

142.8

166

7.5 7.5

7.5 7.5

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

MHz

MHz

MHz

ns

ns

Notes:

1. See “Switching Test Circuit” for test conditions.

2. Skew is measured with all outputs switching in the same direction.

3. These parameters are not 100% tested, but are calculated at initial characterization and at any time the design is modified where

frequency may be affected.

4. tCF is a calculated value and is not guaranteed. tCF can be found using the following equation:

tCF = 1/fMAX (internal feedback) - tS.

PALCE22V10H-7 (Com’l)

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet PALCE22V10Z-25PC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| PALCE22V10Z-25PC | 24-Pin EE CMOS (Zero Power) Versatile PAL Device | Lattice Semiconductor |

| PALCE22V10Z-25PI | 24-Pin EE CMOS (Zero Power) Versatile PAL Device | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |