|

|

PDF ZR36060PQC Data sheet ( Hoja de datos )

| Número de pieza | ZR36060PQC | |

| Descripción | Integrated JPEG CODEC | |

| Fabricantes | ETC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ZR36060PQC (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Integrated JPEG CODEC

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

............................................1

Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

The ZR36060 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

The ZR36060 and the JPEG Standard . . . . . . . . . . . . . . . . . . . . . . . 3

JPEG baseline overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3

JPEG markers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

Motion JPEG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5

Notational Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Pin Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

Video Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Video Syncs - Master and Slave Modes. . . . . . . . . . . . . . . . . . . . . . 8

Master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .9

Data Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Video stream sampling and cropping . . . . . . . . . . . . . . . . . . . . . . 10

The PVALID control signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Video Scaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Horizontal down-scaling in compression . . . . . . . . . . . . . . . . . . . . . . . . .11

Vertical down-scaling in compression . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Horizontal up-scaling in decompression . . . . . . . . . . . . . . . . . . . . . . . . .11

Vertical up-scaling in decompression . . . . . . . . . . . . . . . . . . . . . . . . . . .12

Active Area Size Restrictions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Spatial Mix of Video Streams. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Host Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Interrupt Request and Associated Registers . . . . . . . . . . . . . . . . . 15

Code Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Master Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Slave Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Host abort of a code read or write cycle. . . . . . . . . . . . . . . . . . . . . . . . . .18

Data alignment in Code Slave mode. . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Transition between fields in compression . . . . . . . . . . . . . . . . . . . . . . . .19

Transition between fields in decompression . . . . . . . . . . . . . . . . . . . . . .20

Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

ZR36060 Functional States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

State Transitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

The SLEEP State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Loading Parameters and Tables . . . . . . . . . . . . . . . . . . . . . . . . . . .21

Data Flow Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

Data Flow in Compression . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Data Flow in Decompression . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Compression and Decompression Modes . . . . . . . . . . . . . . . . . . . .23

Compression Pass . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

Data Corruption during Compression . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Statistical Compression Pass . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Auto Two-Pass Compression . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Tables-Only Compression Pass. . . . . . . . . . . . . . . . . . . . . . . . . . . .24

Decompression . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

Data Corruption during Decompression . . . . . . . . . . . . . . . . . . . . . . . . . 26

Power Management and Power-up . . . . . . . . . . . . . .27

Register and Memory Description . . . . . . . . . . . . . .28

General Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28

ID and Testing Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

Video Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31

JPEG Marker Segments. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . .35

Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . .35

Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . .35

AC Timing Specifications . . . . . . . . . . . . . . . . . . . . .36

Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . .40

i

1 page

Integrated JPEG CODEC

1.0 INTRODUCTION

1.1 The ZR36060

The ZR36060 is an integrated JPEG codec targeted to video

capture and editing applications in desktop and laptop comput-

ers. Figure 1 shows an example of a typical application, a video

editing subsystem for PCI bus computers.

The ZR36060 integrates the functionality of a JPEG codec such

as the ZR36050, a raster-to-block converter such as the

ZR36015, as well as the strip buffer SRAM for the raster-to-block

converter and additional functions. It is based on the field

proven, fully compliant Zoran JPEG device technology, and

incorporates Zoran’s patented bit rate control mechanism.

In compression, the ZR36060 accepts YUV 4:2:2 digital video,

performs optional cropping and decimation, and encodes it into

a JPEG baseline compressed bitstream, which it outputs to a

host controller. In decompression, it receives the bitstream from

the host controller, decodes it back to YUV 4:2:2 format digital

video, up-scales it if required, and outputs the video to a com-

posite video encoder or other destination.

The ZR36060 incorporates hardware support for multiplexing

two video sources (in rectangular windows) in compression, or

the reconstructed video with another source in decompression.

It can operate as a video sync master or slave, with 8-bit or 16-

bit video bus widths. A pixel flow control mechanism is provided

for convenient implementation of non-real-time video rates, such

as for still picture compression.

VSYNC

HSYNC

FI

BLANK

PVALID

SUBIMG

POE

Y[7:0]

UV[7:0]

RTBSY

DATERR

CCS

COE

CWE

CBUSY

CODE [7:0]

Video Interface

Strip Memory

JPEG CODEC

CODE FIFO

(512 x 8 bits)

PLL & Clocks

Internal

Configuration

Memory

(1K x 8 bits)

(Registers,

Markers, Tables)

Control

CODE and Host Interface

VCLK

VCLKx2

START

FRAME

END

EOI

COMP

SLEEP

RESET

ADDR[1:0]

JIRQ

ACK

CS

WR

RD

DATA[7:0]

Figure 2. ZR36060 Block Diagram

The code interface of the ZR36060 can operate in 8-bit master,

8-bit slave or 16-bit slave modes. In slave mode, code transfer

shares the host interface, which is generic enough to be able to

interface gluelessly with a variety of host controllers, ranging

from the dedicated, high performance ZR36057 to common

microcontrollers.

The ZR36060 is a CMOS device, requiring a 3.3 Volt power

supply. Its inputs and outputs are 5 Volt tolerant. A power-down

(“sleep”) mode reduces current consumption to a very low level,

while preserving the logic state of the device.

A block diagram of the ZR36060 is shown in Figure 2.

1.2 The ZR36060 and the JPEG Standard

The JPEG standard, ISO/IEC 10918-1, defines a whole range of

options for compressing continuous-tone images - a baseline

lossy compression process, extended lossy processes, lossless

compression, and hierarchical compression methods. The

ZR36060 implements the baseline process.

Even the baseline method is defined by the JPEG standard to

provide maximal flexibility in choosing the color space in which

an image is compressed - an image can have an almost unlimit-

ed number of color components, and these can be compressed

in a single scan, or in multiple scans. Because its main targeted

application is motion color video compression and decompres-

sion, the architecture of the ZR36060 supports one particular

subset: Since the ZR36060 supports only the YUV 4:2:2 pixel

format, it supports three color components, in a single inter-

leaved scan.

1.2.1 JPEG baseline overview

The JPEG baseline compression method is based on the

discrete cosine transform or DCT. The DCT is performed on 8x8

blocks of samples, of each color component, resulting in a set of

64 DCT coefficients for each block. Thus, in order for a normal

raster-scanned image to be compressed, it must first be convert-

ed to block format This requires that an 8-line strip of the image

(containing 8 lines of each color component) be stored in a strip

buffer, so that the samples can be re-ordered (see Figure 2).

For subsequent stages of the compression, the 64 DCT coeffi-

cients of each block are further re-ordered by scanning the block

in a zig-zag sequence. Each of the 64 coefficients is quantized

using the appropriate value from a 64-entry quantization table. In

the ZR36060, it is possible to define three different quantization

tables, one per color component; generally, however, two tables

are used, one for the luminance component and one for the

chrominance component.

The quantized DCT coefficients are passed to a Huffman

encoder, for the final stage of the process. The Huffman coding

is performed separately for the DC coefficient of each block (the

first coefficient of the block), and the remaining 63 AC coeffi-

3

5 Page

Integrated JPEG CODEC

• FIVedge - Defines at which VSYNC edge the FI signal

changes state (leading or trailing edge). This is also the reset

point for the vertical counters, indicating the end of the previ-

ous field and the beginning of a new field.

After the parameters are properly initialized and loaded (using

the Load command), the sync generator is free running, and is

not affected by the state of the JPEG codec. The SyncRst

register bit resets the sync generator counters and the PVALID

signal can temporarily freeze the counting and sync signals.

BVstart

BVend

FI BLANK

VsyncSize

VSYNC

BHstart

BHend

BLANK

HsyncSize

HSYNC

Htotal

ODD Field

EVEN Field

Note: In this example VSPol = HSPol = FIPol = BlPol = FIVedge = 0.

Figure 3. Video Sync Generation

3.1.2 Slave mode

When configured as a sync Slave, the ZR36060 samples the fol-

lowing signals:

• HSYNC - Horizontal sync

• VSYNC - Vertical sync

• FI - Even/Odd field indication

The parameters Vtotal, Htotal, VsyncSize, HsyncSize, BVstart,

BVend, BHstart, BHend, BlPol, FIPol are not used in Slave

mode. VSPol, HSPol, FIDet and FIVedge are used as follows:

• VSPol - Polarity of the VSYNC input signal.

• HSPol - Polarity of the HSYNC input signal.

• FIDet - Exchange the even/odd field interpretation after de-

tection. (detection can be accomplished in two ways

according to the FIExt parameter, see below)

• FIVedge - Defines the reset point for the vertical counters in-

dicating the end of the previous field and the beginning of a

new field. When FIExt = 0 it also defines the proper VSYNC

edge used to latch HSYNC to internally detect the even/odd

field.

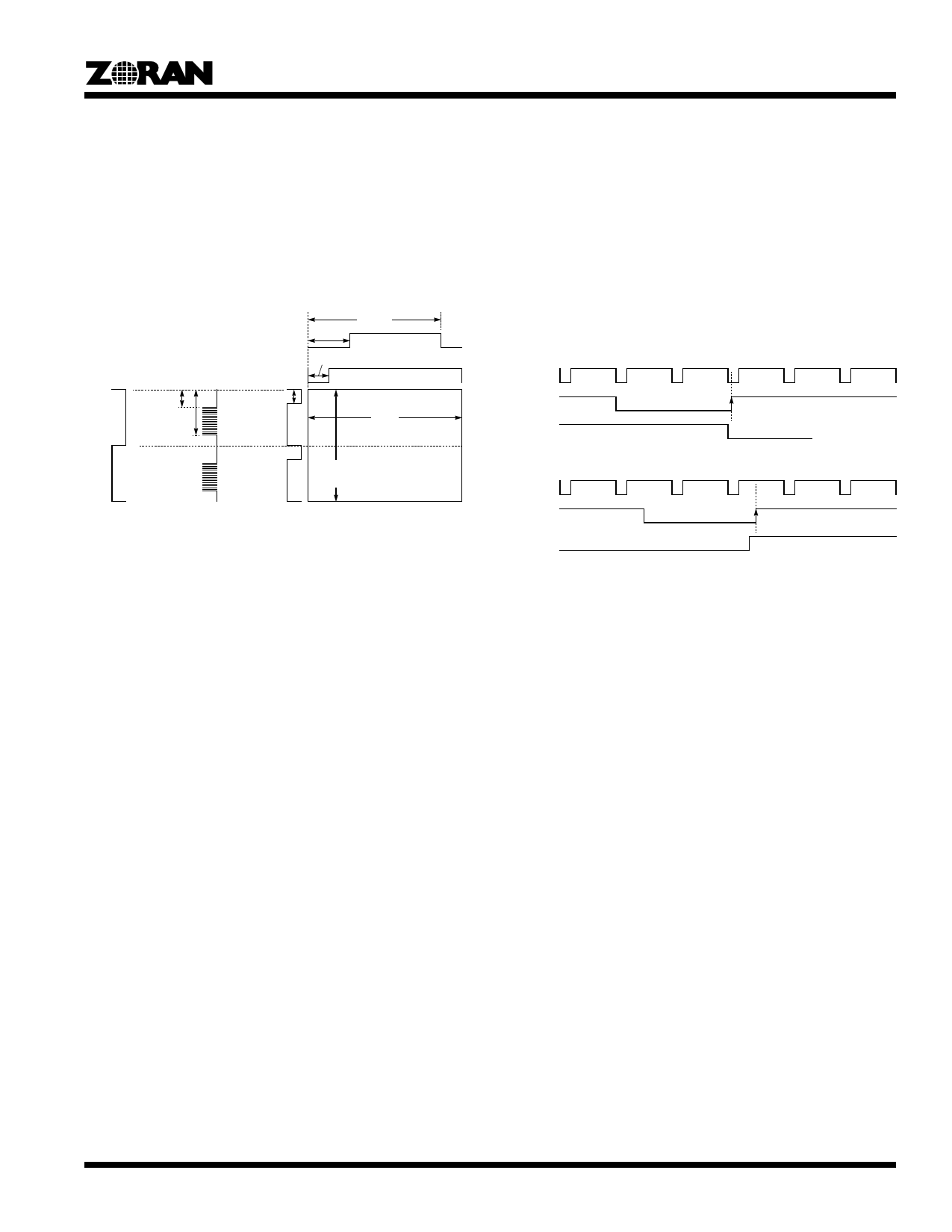

The field detection can be accomplished in two ways depending

on the FIExt parameter (see Figure 4):

• External indication by means of the FI signal (FIExt = 1), tog-

gling at the VSYNC rate, indicating whether the current field

is even or odd. The polarity of FI is programmable, using the

FIPol parameter, while the even/odd interpretation can be

exchanged using the FIDet parameter.

• Internal detection (FIExt = 0), derived from latching the state

of HSYNC at each VSYNC. This is useful when using the

ZR36060 with video sources that do not provide a dedicated

field indication signal. Odd fields are those where the

VSYNC edge latches the HSYNC during its short sync peri-

od, while on even fields the VSYNC edge latches the

HSYNC in the middle of the line (see Figure 4). The VSYNC

edge (leading or trailing) used to latch the HSYNC signal can

be programmed by means of the FIVedge parameter.

Changing FIDet will change the even/odd interpretation.

Note: the HSYNC edge must precede the latching VSYNC edge

by at least 2 VCLKs for reliable latching.

HSYNC

VSYNC

FI

ODD Field (Fields (1, 3, 5…)

HSYNC

VSYNC

FI

EVEN Field (Fields (2, 4, 6…)

Note: VSPol = HSPol = FIPol = FIDet = 0, FIVedge = 1

Figure 4. Field Detection Showing Hor. and Ver. Timing

3.2 Data Formats

When the ZR36060 is configured for 16-bit video bus width

(Video8==0), the luminance signal is on Y7:0, and the chromi-

nance signals are multiplexed on the UV7:0 lines (see Figure 5).

When operating in 8-bit video bus mode (Video8==1), both the

luminance and the chrominance signals are on Y7:0, multiplexed

in time according to the CCIR656 recommendation (U=Cb,

V=Cr):

U0,Y0,V0,Y1,U2,Y2,V2,Y3,....

For 16-bit video, the pixels are sampled on every other rising

edge of VCLKx2, which is enabled by VCLK, the video clock

qualifier. The polarity of the VCLK qualifier is programmable via

the VCLKPol parameter. 8-bit video is sampled using all rising

edges of VCLKx2, at twice the pixel rate.

Note that 1 pixel length is always 1 VCLK, with both 16-bit and

8-bit video. All internal counters and video events are based on

VCLK, that must always be present (at half the frequency of

VCLKx2) even when the video interface is configured for 8-bit

width.

In decompression, the output pixel levels are CCIR-

601compliant, with values in the [16,235] range. It is possible to

override this and let the ZR36060 output the full 256-level scale

with the Range parameter bit.

9

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet ZR36060PQC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ZR36060PQC | Integrated JPEG CODEC | ETC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |