|

|

PDF 74LCX07 Data sheet ( Hoja de datos )

| Número de pieza | 74LCX07 | |

| Descripción | Low Voltage Hex Buffer with Open Drain Outputs | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74LCX07 (archivo pdf) en la parte inferior de esta página. Total 12 Páginas | ||

|

No Preview Available !

December 2013

74LCX07

Low Voltage Hex Buffer with Open Drain Outputs

Features

■ 5V tolerant inputs

■ 2.3V to 5.5V VCC specifications provided

■ 2.9ns tPD max. (VCC = 3.3V), 10µA ICC max.

■ Power down high impedance inputs and outputs

■ +24mA output drive (VCC = 3.0V)

■ Implements proprietary noise/EMI reduction circuitry

■ Latch-up performance exceeds JEDEC 78 conditions

■ ESD performance:

– Human body model > 2000V

– Machine model > 200V

■ Leadless DQFN package

General Description

The LCX07 contains six buffers. The inputs tolerate volt-

ages up to 7V allowing the interface of 5V systems to 3V

systems.

The outputs of the LCX07 are open drain and can be

connected to other open drain outputs to implement

active HIGH wire AND or active LOW wire OR functions.

The 74LCX07 is fabricated with advanced CMOS tech-

nology to achieve high speed operation while maintain-

ing CMOS low power dissipation.

Ordering Information

Package

Order Number Number

Package Description

74LCX07M

M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow

74LCX07SJ

74LCX07BQX(1)

M14D

MLP14A

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

14-Terminal Depopulated Quad Very-Thin Flat Pack No Leads (DQFN), JEDEC

MO-241, 2.5 x 3.0mm

74LCX07MTC

MTC14 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm

Wide

Note:

1. DQFN package available in Tape and Reel only.

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering number.

All packages are lead free per JEDEC: J-STD-020B standard.

©1999 Fairchild Semiconductor Corporation

74LCX07 Rev. 1.11.1

www.fairchildsemi.com

1 page

Dynamic Switching Characteristics

Symbol

VOLP

VOLV

Parameter

Quiet Output Dynamic Peak VOL

Quiet Output Dynamic Valley VOL

VCC (V)

3.3

2.5

3.3

2.5

Conditions

CL = 50pF, VIH = 3.3V, VIL = 0V

CL = 30pF, VIH = 2.5V, VIL = 0V

CL = 50pF, VIH = 3.3V, VIL = 0V

CL = 30pF, VIH = 2.5V, VIL = 0V

TA = 25°C

Typical

0.9

0.7

–0.8

–0.6

Unit

V

V

Capacitance

Symbol

CIN

COUT

CPD

Parameter

Input Capacitance

Output Capacitance

Power Dissipation Capacitance

Conditions

VCC = Open, VI = 0V or VCC

VCC = 3.3V, VI = 0V or VCC

VCC = 3.3V, VI = 0V or VCC, f = 10MHz

Typical

7

8

25

Units

pF

pF

pF

©1999 Fairchild Semiconductor Corporation

74LCX07 Rev. 1.11.1

5

www.fairchildsemi.com

5 Page

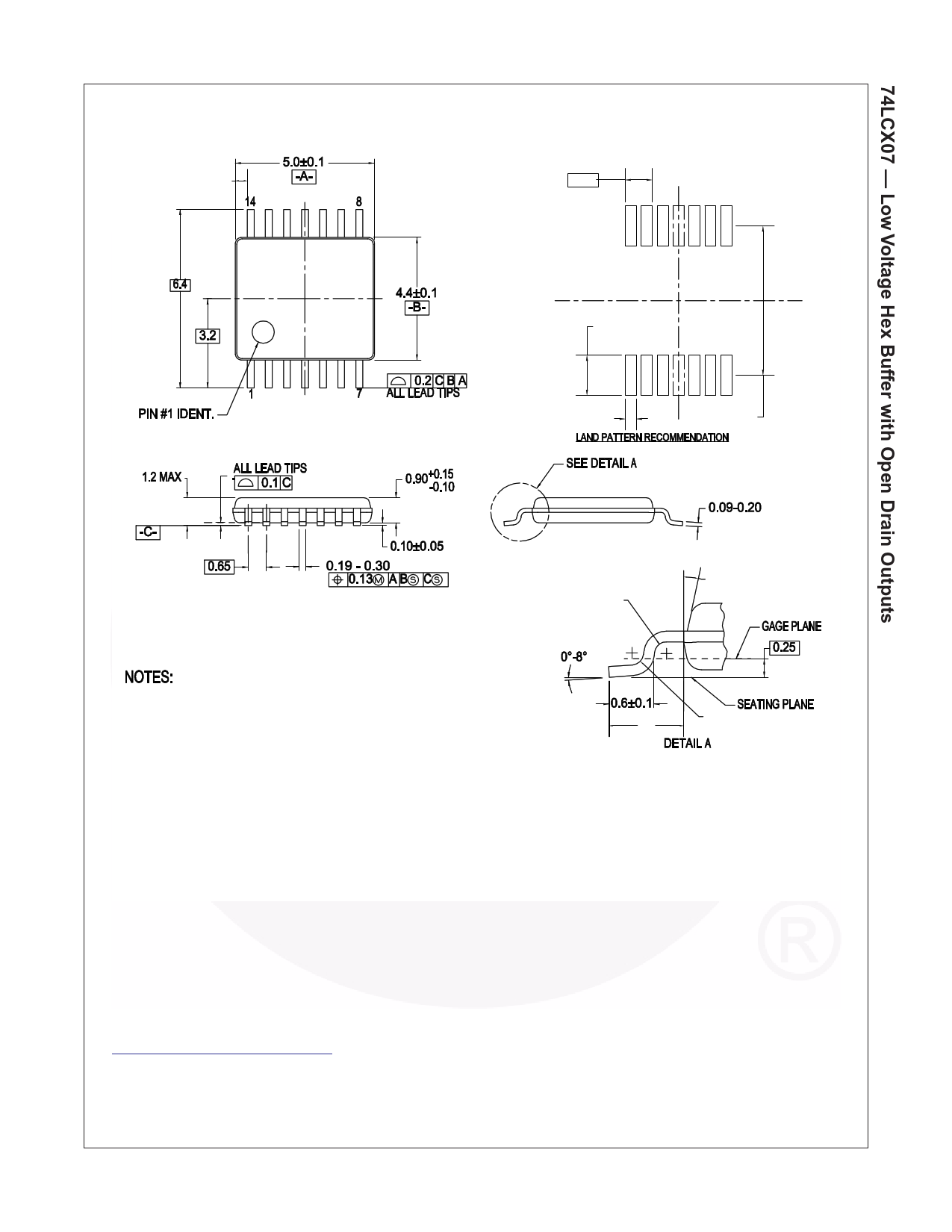

Physical Dimensions (Continued)

0.43 TYP

0.65

1.65

0.45

6.10

R0.09 min

12.00°TOP & BOTTOM

A. CONFORMS TO JEDEC REGISTRATION MO-153,

VARIATION AB, REF NOTE 6

B. DIMENSIONS ARE IN MILLIMETERS

1.00

C. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH,

AND TIE BAR EXTRUSIONS

D. DIMENSIONING AND TOLERANCES PER ANSI

Y14.5M, 1982

E. LANDPATTERN STANDARD: SOP65P640X110-14M

F. DRAWING FILE NAME: MTC14REV6

R0.09min

Figure 6. 14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or

obtain the most recent revision. Package specifications do not expand the terms of Fairchild’s worldwide terms and conditions,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor’s online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/

©1999 Fairchild Semiconductor Corporation

74LCX07 Rev. 1.11.1

11

www.fairchildsemi.com

11 Page | ||

| Páginas | Total 12 Páginas | |

| PDF Descargar | [ Datasheet 74LCX07.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74LCX00 | Low Voltage Quad 2-Input NAND Gate | Fairchild Semiconductor |

| 74LCX00 | Low voltage CMOS QUAD 2-Input NAND gate | ST Microelectronics |

| 74LCX00M | Low Voltage Quad 2-Input NAND Gate | Fairchild Semiconductor |

| 74LCX00MTC | Low Voltage Quad 2-Input NAND Gate with 5V Tolerant Inputs | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |