|

|

PDF HYS72V32300GR-75-C2 Data sheet ( Hoja de datos )

| Número de pieza | HYS72V32300GR-75-C2 | |

| Descripción | PC133 Registered SDRAM-Modules | |

| Fabricantes | Infineon | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de HYS72V32300GR-75-C2 (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

HYS 72Vxx3xxGR

PC133 Registered SDRAM-Modules

3.3 V 168-pin Registered SDRAM Modules

PC133 128 MByte Module

PC133 256 MByte module

PC133 512 MByte Module

PC133 1 GByte Module

PC133 2 GByte Module

• 168-pin Registered 8 Byte Dual-In-Line

SDRAM Module for PC and Server main

memory applications

• Programmable CAS Latency, Burst Length,

and Wrap Sequence (Sequential &

Interleave)

• One bank 16M × 72, 32M x 72, 64M × 72and

128M x 72, two bank 128M × 72 and

256M x 72 organization

• Optimized for ECC applications with very low

input capacitances

• JEDEC standard Synchronous DRAMs

(SDRAM) Programmable CAS Latency, Burst

Length and Wrap Sequence (Sequential &

Interleave)

• Single + 3.3 V (± 0.3 V) power supply

• Auto Refresh (CBR) and Self Refresh

• All inputs and outputs are LVTTL compatible

• Serial Presence Detect with E2PROM

• Utilizes SDRAMs in TSOPII-54 packages

with registers and PLL.

• Card Size: 133.35 mm × 38.10 / 43.18 mm

with Gold contact pads and max. 4.00 / 6.80

mm thickness (JEDEC MO-161)

• These modules all fully compatible with the

current industry standard PC133 and PC100

specifications

• Performance:

speed grade

-7 -7.5 Unit

fCK Clock Frequency (max.) @ CL = 3 133 133 MHz

tCK Clock Cycle Time (min.) @ CL = 3 7.5 7.5 ns

tAC

Clock Access Time (min.) @ CL= 3

5.4

5.4

ns

fCK Clock Frequency (max.) @ CL = 2 133 100 MHz

tCK Clock Cycle Time (min.) @ CL = 2 7.5

10

ns

tAC

Clock Access Time (min.) @ CL= 2

5.4

6

ns

Description

The HYS 72Vxx3xxGR-7 and -7.5 are industry standard 168-pin 8-byte Dual in-line Memory Modules (DIMMs)

organized as 16M × 72, 32M x 72, 64M × 72, 128M × 72 and 256M x 72 high speed memory arrays designed with

Synchronous DRAMs (SDRAMs) for ECC applications. All control and address signals are registered on-DIMM

and the design incorporates a PLL circuit for the Clock inputs. Use of an on-board register reduces capacitive

loading on the input signals but are delayed by one cycle in arriving at the SDRAM devices. Decoupling capacitors

are mounted on the PC board. The DIMMs use a serial presence detects scheme implemented via a serial

E2PROM using the 2-pin I2C protocol. The first 128 bytes are utilized by the DIMM manufacturer and the second

128 bytes are available to the end user. All Infineon 168-pin DIMMs provide a high performance, flexible 8-byte

interface in a 133.35 mm long footprint.

INFINEON Technologies

1

2002-07-18

1 page

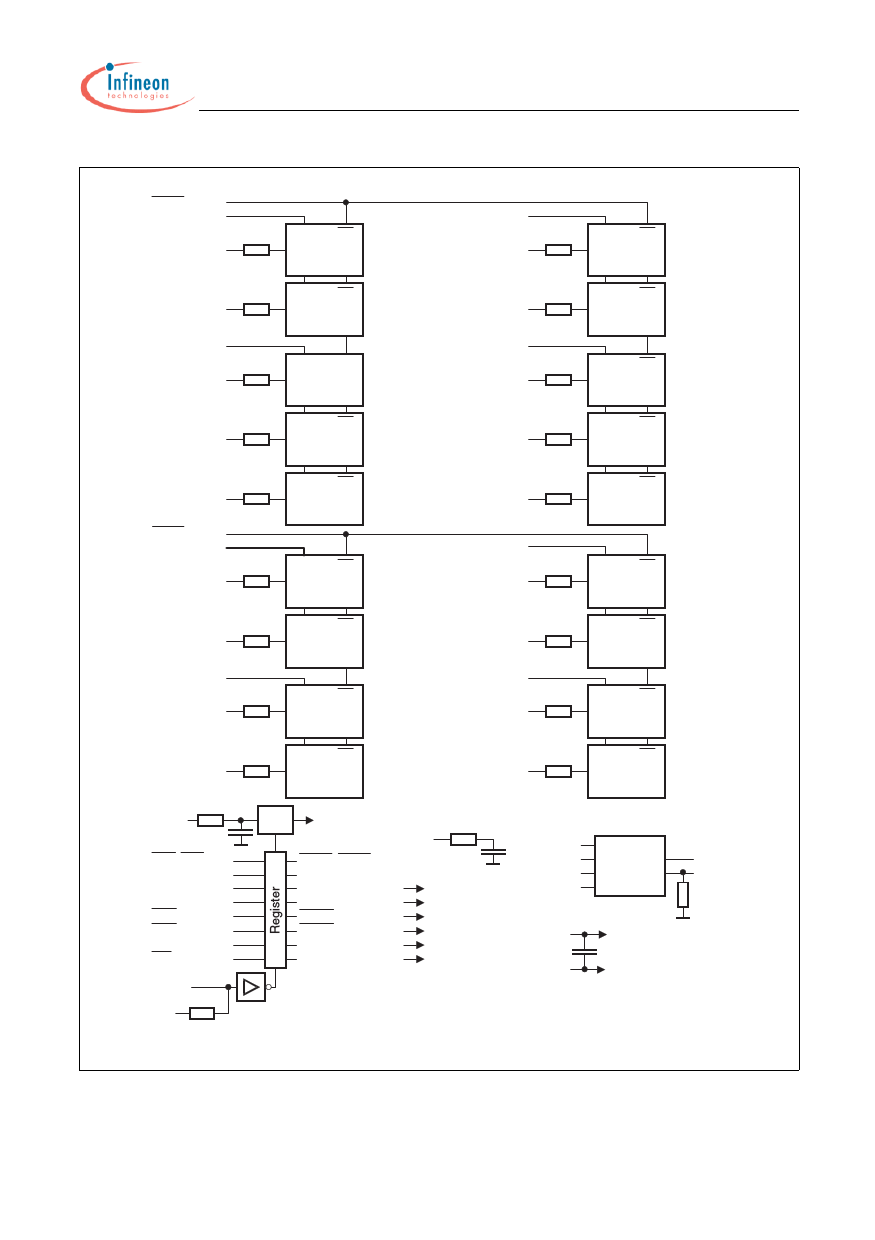

HYS 72Vxx3xxGR

PC133 Registered SDRAM-Modules

RCS0

RDQMB0

DQ0-DQ3

DQM CS

DQ0-DQ3

D0

RDQMB4

DQ32-DQ35

DQM CS

DQ0-DQ3

D8

DQ4-DQ7

RDQMB1

DQ8-DQ11

DQM CS

DQ0-DQ3

D1

DQM

DQ0-DQ3

D2

DQ36-DQ39

RDQMB5

DQ40-DQ43

DQM CS

DQ0-DQ3

D9

DQM CS

DQ0-DQ3

D10

DQ12-DQ15

CB0-CB3

RCS2

RDQMB2

DQ16-DQ19

DQM CS

DQ0-DQ3

D3

DQM CS

DQ0-DQ3

D16

DQM CS

DQ0-DQ3

D4

DQ44-DQ47

CB4-CB7

RDQMB6

DQ48-DQ51

DQM CS

DQ0-DQ3

D11

DQM CS

DQ0-DQ3

D17

DQM CS

DQ0-DQ3

D12

DQ20-DQ23

RDQMB3

DQ24-DQ27

DQM CS

DQ0-DQ3

D5

DQM CS

DQ0-DQ3

D6

DQ52-DQ55

RDQMB7

DQ56-DQ59

DQM CS

DQ0-DQ3

D13

DQM CS

DQ0-DQ3

D14

DQ28-DQ31

CLK0

12 pF

CS0/CS2

DQMB0-7

BA0, BA1

A0-A11, A12

RAS

CAS

CKE0

WE

REGE

10 kΩ

VCC

DQM CS

DQ0-DQ3

D7

DQ60-DQ63

DQM CS

DQ0-DQ3

D15

PLL SDRAMs D0-D17

E2PROM

(256 word x 8 Bit)

CLK1, CLK2, CLK3

RCS0/RCS2

12 pF

SA0

SA1

SA0

SA1 SDA

RDQMB0-7

SA2 SA2 WP

RBA0, RBA1

RA0-RA11, RA12

SDRAMs D0-D17

SDRAMs D0-D17

SCL SCL

47 kΩ

RRAS

SDRAMs D0-D17

RCAS

RCKE0

RWE

SDRAMs D0-D17

SDRAMs D0-D17

SDRAMs D0-D17

VCC

VSS

D0-D17, Reg., DLL

C

D0-D17, Reg., DLL

1) DQ wirding may differ from that decribed

in this drawing; however DQ/DQB relationship

must be maintained as shown

2) All resistors are 10 Ω unless otherwise noted

SPB04135

Block Diagram: One Bank 16M x 72, 32M x 72, 64M x 72 and 128M x 72 SDRAM DIMM Modules

HYS72V16300GR, HYS72V32301GR, HYS72V64300GR and HYS72V128320GR

using x4 organized SDRAMs

INFINEON Technologies

5

2002-07-18

5 Page

HYS 72Vxx3xxGR

PC133 Registered SDRAM-Modules

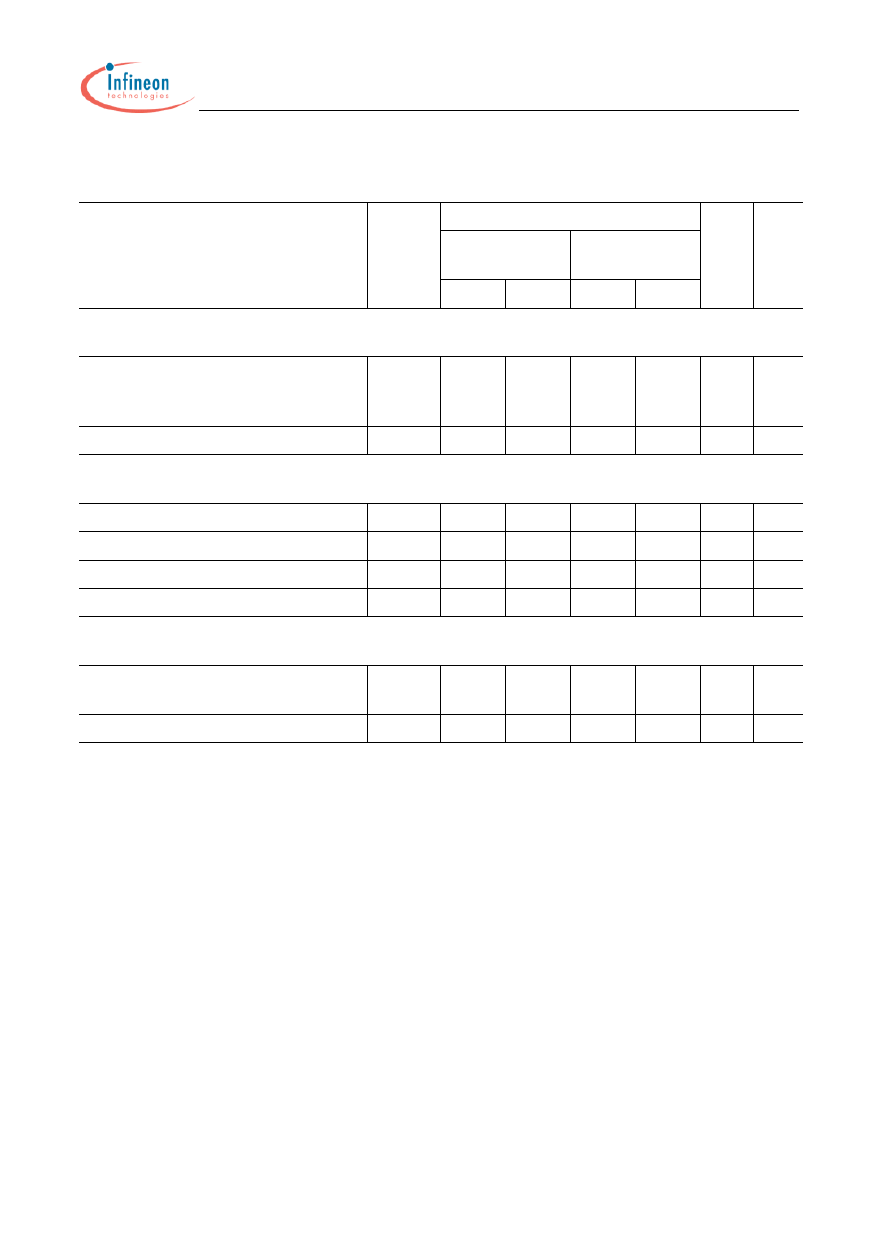

AC Characteristics (SDRAM Device Specification) (cont’d) 4), 5)

TA = 0 to 70 °C 1); VSS = 0 V; VDD = 3.3 V ± 0.3 V, tT = 1 ns

Parameter

Symbol

Limit Values

-7

PC133-222

-7.5

PC133-333

min. max. min. max.

Unit Note

Refresh Cycle

Refresh Period

tREF

64&128MBit SDRAM Based Modules

256&512MBit SDRAM Based Modules

Self Refresh Exit Time

tSREX

Read Cycle

Data Out Hold Time

Data Out to Low Impedance Time

Data Out to High Impedance Time

DQM Data Out Disable Latency

tOH

tLZ

tHZ

tDQZ

Write Cycle

Data Input to Precharge

(write recovery)

DQM Write Mask Latency

tWR

tDQW

–

–

1

3

0

3

–

2

0

15.6

7.8

–

–

–

1

–3

–0

73

2–

–2

–0

15.6

7.8

–

µs

µs

CLK

–

6)

– ns –

– ns 7)

7 ns 7)

2 CLK –

– CLK –

– CLK –

INFINEON Technologies

11

2002-07-18

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet HYS72V32300GR-75-C2.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HYS72V32300GR-75-C2 | PC133 Registered SDRAM-Modules | Infineon |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |