|

|

PDF MA17501 Data sheet ( Hoja de datos )

| Número de pieza | MA17501 | |

| Descripción | Radiation Hard MIL-STD-1750A Execution unit | |

| Fabricantes | Dynex | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MA17501 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Replaces March 1997 version, DS4548 - 2.3

MAM1A715750011

Radiation Hard MIL-STD-1750A Execution unit

DS4548 - 3.2 January 2000

The MA17501 Execution Unit is a component of the Dynex

Semiconductor MAS281 chip set. Other chips in the set

include the MA17502 Control Unit and the MA17503 lnterrupt

Unit. Also available is the peripheral MA31751 Memory

Management Unit/Block Protection Unit. These chips in

conjunction implement the full MlL-STD-1750A lnstruction Set.

The MA17501 - consisting of a full function 16-bit ALU, 24 x

16-bit dual-port RAM register file, 32-bit barrel shifter, 4 x 24-

bit parallel multiplier, synchronisation clock generation logic,

and microcode decode logic - provides all computational,

logical, and synchronisation functions for the chip set. Table 1

provides brief signal definitions.

The MA17501 is offered in several package styles

including; dual-in-line, flatpack and leadless chip carrier. Full

packaging information is given at the end of the document.

BLOCK DIAGRAM

FEATURES

s MIL-STD-1750A Instruction Set Architecture

s Full Performance over Military Temperature Range

(-55°C to +125°C)

s Radiation Hard CMOS/SOS Technology

s 16-Bit Bidirectional Address/Data Bus

s 16-Bit Full Function Registered ALU

s 32-Bit Barrel Shifter

s 24 x 16-Bit Dual-Port RAM File

• 16 User Accessible General Purpose Registers

• 8 Microcode Accessible Registers

s 4 x 24-Bit Parallel Multiplier

• 48-Bit Accumulator

• 16-Bit x 16-Bit Multiply in 4 Machine Cycles

s Instruction Pre-Fetch

s MAS281 Integrated Built-in Self Test

s TTL Compatible System Interface

1.0 SYSTEM CONSIDERATIONS

The MA17501 Execution Unit (EU) is a component of the

Dynex Semiconductor MAS281 chip set. This chip set

implements the full MlL-STD-1750A instruction set

architecture. The other chips in the set are the MA17502

Control Unit (CU) and the MA17503 Interrupt Unit (IU). Also

available is the peripheral MA31751 Memory Management

Unit/Block Protection Unit (MMU(BPU)).

Figure 1 depicts the relationship between the chip set

components. The EU provides the arithmetic and logical

computation resources for the chip set. The EU also provides

program sequencing logic in support of branching and

subroutine functions. The lU provides interrupt and fault

handling resources, DMA interface control signals, and the

three MIL-STD-1750A timers. The EU and lU are each

controlled by microcode from the CU. The MMU(BPU) may be

configured to provide 1M-word memory management (MMU)

and/or 1K-word memory block write protection (BPU)

functions.

1/35

1 page

MA17501

A 20-bit multiplexed microcode (M) bus provides a

pathway between the Control Unit (CU) and the Execution

Register (E) buffered microcode decode logic on the EU chip.

Microcode placed on this bus by the CU controls all actions of

the EU.

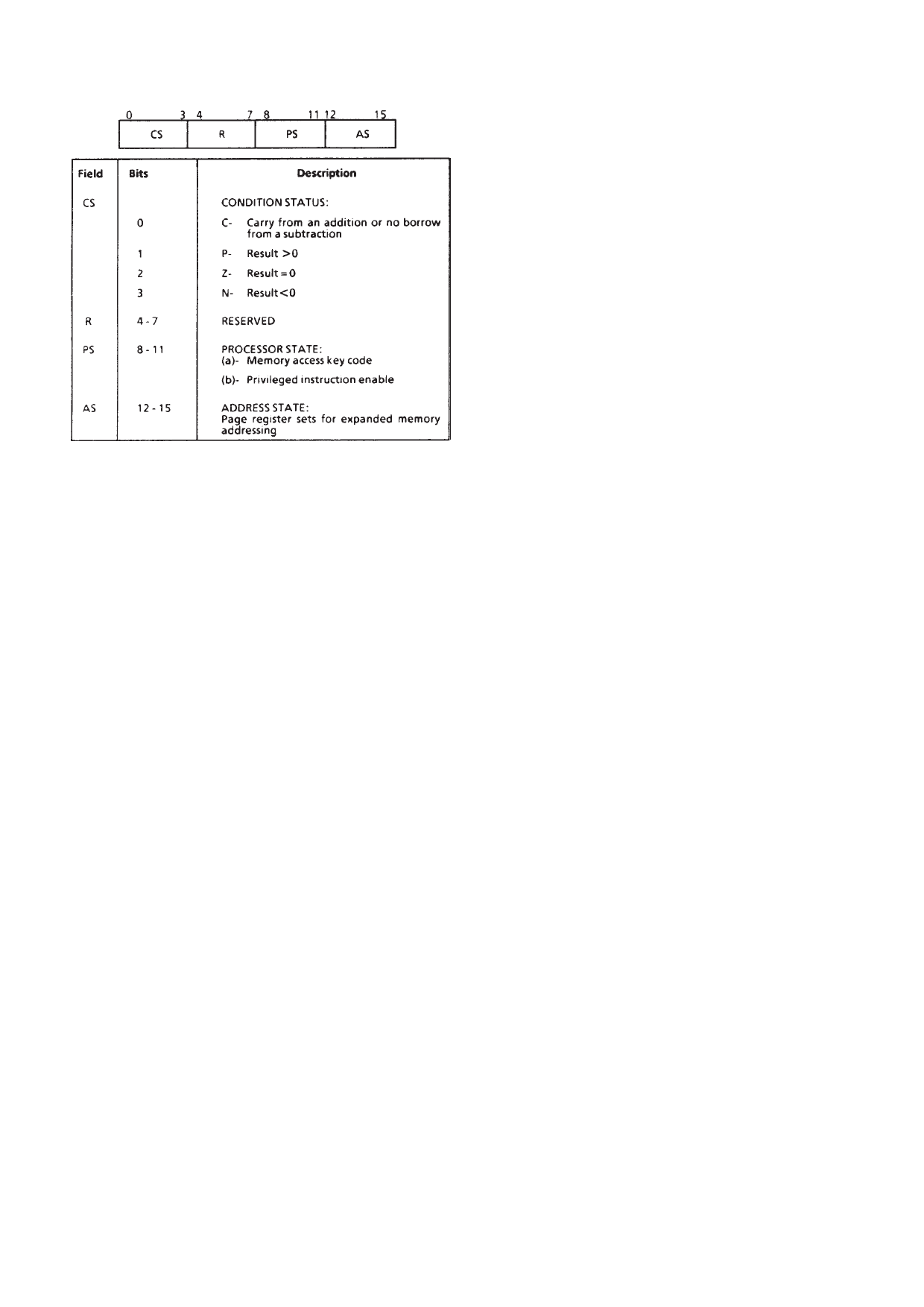

Figure 3: Status Word Format

2.7 INSTRUCTION FETCH REGISTERS

The Instruction Counter (IC), Instruction A (IA), and

Instruction B (IB) registers allow sequential instruction fetches

to be performed without assistance from the ALU. The lC

register, which holds the 16-bit address of the next instruction

to be fetched from memory, is loaded automatically by reset,

jump, or branch operations. Once loaded, it functions as a

dedicated counter to sequence from one instruction to the

next. The current IC contents may be stored in registers R0

through R15 or in memory (pushed onto a stack) to provide

return linkages for subroutine calls. As part of the microcoded

interrupt handling routine the lC is saved in memory via the

interrupt linkage pointer.

Registers lA and IB provide an instruction look-ahead

capability. ln the case of 16-bit instructions, lB holds the

instruction currently executing while lA holds the next

instruction to be executed. ln the case of 32-bit instructions, IB

and lA each hold half of the instruction. IA and Dl (Dl stores the

immediate operands) are loaded as the instruction in lA is

transferred to lB for execution; if the instruction in lB uses an

immediate operand, lA is reloaded with the next instruction

while Dl maintains the immediate data. This overlapping of

operations allows higher performance levels to be achieved.

2.8 BUSES

Three 16-bit wide buses (R, S, and Y) interconnect the EU

data storage and computational elements. The R and S buses

accept operands from selected EU data storage elements and

route them to inputs of selected EU computational elements.

The Y, or destination, bus serves to route computational

results either back to EU data storage and computational

elements or to the various operand transfer registers.

A 16-bit multiplexed Address/Data (AD) Bus provides a

communications path between the EU, other components of

the MAS281 chip set, and any other devices mapped into the

chip set's address space. Data transfers between the AD Bus

and the R, S, and Y buses are buffered by the operand transfer

registers.

2.9 SYNCHRONISATION CLOCK GENERATION LOGIC

The Execution Unit generates all of the synchronisation

clocks required by the chip set and CPU system. The EU

converts an externally supplied oscillator signal into five

synchronisation signals: SYNCN, SYSCLK1N,SYNCLKN,

CLKPCN, CLK02N. The EU generates SYNCN for elements

external to the chip set whereas SYNCLKN and SYSCLK1N

are generated for the Interrupt Unit and internal EU

synchronisation, respectively. SYSCLK1N is also brought out

on a pin for use by external monitoring systems. The EU

generates CLKPCN and CLK02N for use in the Control Unit.

The CU uses CLKPCN to precharge the M Bus and transmit

the first microword while CLK02N is used to transmit

microword two.

The EU also contains the wait state generation interface.

Failure of memory or l/O subsystems to drive RDYN low at the

proper time during the DSN pulse causes the EU to hold

SYNCLKN, SYNCN, SYSCLK1N, and CLKPCN in the high

state; CLK02N, AS and DSN, in the low state; and RD/WN, IN/

OPN and M/ION in their current states for one or more

oscillator cycles beyond the end of the normal five OSC cycle

machine cycle. When RDYN is asserted low, the EU allows the

machine cycle to conclude at the high-to-low transition of the

current oscillator cycle. This will allow all the synchronisation

and control signals to resume normal operation.

Additionally, IRDYN is used to signal completion of internal

l/O command control of the lnterrupt Unit (IU). The IU thus can

extend the duration of the above mentioned bus signals.

Failure of the lU to drive lRDYN low at the proper time during

the DSN low pulse causes the EU to hold SYNCLKN, SYNCN,

SYSCLK1N, and CLKPCN in the high state; CLK02N, AS, and

DSN in the low state; and lN/OPN, M/lON, and RD/WN in the

state for the normal five OSC cycle machine cycle. When the

lU asserts IRDYN low, the EU allows the machine cycle to

conclude at the high-to-low transition of the current oscillator

cycle. This will allow all the synchronisation and control signals

to resume normal operation.

[NOTE: Whenever the EU is executing a machine cycle

which requires IRDYN to drop low for completion, the machine

cycle will be a minimum of six OSC cycles long. The maximum

duration of this machine cycle depends on the length of time

that the lU holds IRDYN high.]

5/35

5 Page

MA17501

BIT Test Coverage

1 Mlcrocode Sequencer

IB Register Control

Barrel Shifter

Byte Operations and Flags

BIT Fail Codes (FT13,14,15)

100

2 Temporary Registers (T0 - T7)

Microcode Flags

Multiply

Divide

101

3 Interrupt Unit - MK, Pl, FT

Enable/Disable Interrupts

111

4 Status Word Control

User Flags

General Registers (R0 - R15

110

5 Timer A

Timer B

111

- BIT Pass/Fail Overhead

-

Note: BIT pass is indicated by all zeros in FT bits 13, 14, and 15.

Table 2: MAS281 BIT Summary

Cycles

221

166

214

154

763

26

4.2 INSTRUCTION EXECUTION

Instruction execution is characterised by a variety of

operations composed of various types of machine cycles. The

Execution Unit contains the clock generation circuitry that

creates the different machine cycles depending on the

particular operation being performed at the time. These

operations include: (1) internal CPU cycles, (2) instruction

fetches, (3) operand transfers, and (4) input/output transfers.

Instruction execution may be interrupted at the end of any

individual machine cycle by the PAUSEN (denoting DMA

operations) clock generation circuitry input, and at the

beginning of any given MIL-STD-1750A instruction by an

(IU)IRN or HOLDN low input to the Control Unit.

4.2.1 Internal CPU Cycles

All CPU data manipulation and housekeeping operations

are performed using internal CPU cycles. Internal CPU cycles

are either five or six OSC periods long and are characterised

by AS low and DSN, (IU)DDN, and M/ION high. Section 5.0

provides timing characteristics for internal CPU cycles.

The majority of lnternal CPU Cycles are five OSC period

machine cycles. Six OSC period machine cycles occur when

executing conditional jump or branch microinstructions; the EU

is calculating the branch condition to determine the state of the

T1 output signal.

4.2.2 Instruction Fetches

lnstruction fetches are used to keep the instruction pipeline

full. This ensures that the next instruction is ready for

execution when the preceding instruction is completed.

During jump and branch instruction execution the pipeline

is flushed, then refilled via two consecutive instruction fetches

starting at the new instruction location. The pipeline is also

refilled as part of the interrupt and Hold processing.

lnstruction fetches are five (minimum) OSC period

machine cycles characterised by IN/OPN, M/lON, and RD/WN

high. lnstruction fetches use pipeline registers lA and IB, the

instruction counter (lC), and the data input register (Dl).

Assuming an empty instruction pipeline (as a result of a reset,

jump or branch), the contents of lC are placed on the AD Bus

as an address. The returned value (the instruction) is stored in

the IA register. The lC register is incremented (dedicated

counter mode) and the next fetch is performed.

This second returned value, which may be an instruction or

an immediate operand, is stored in both the lA and Dl registers

as the previous contents of IA advance to the IB register to be

decoded into their microcoded routine. If the second returned

value is an immediate operand, a third instruction fetch will

occur with the instruction being loaded into lA only; Dl retains

the immediate operand.

The data portion (SYNCN high) of instruction fetch cycles

can be extended beyond their minimum five OSC periods by

use of the RDYN signal. RDYN held high during the high-to-

low transition of the machine cycles fifth OSC cycle will extend

the data portion of the machine cycle. The machine cycle can

be completed at any succeeding OSC cycle high-to-low

transition by enveloping this OSC edge with RDYN low.

4.2.3 Operand Transfers

Operand transfers are used to obtain operands to be used

by an instruction and to save any results of an instructions

execution. Machine cycles associated with operand transfers

are a minimum of five OSC periods in duration. The RDYN

signal can be used to insert wait states into the data portion of

the machine cycle (SYNCN high) to accommodate slow

memory.

11/35

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet MA17501.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MA17501 | Radiation Hard MIL-STD-1750A Execution unit | Dynex |

| MA17502 | Radiation Hard MIL-STD-1750A Control Unit | Dynex |

| MA17503 | Radiation Hard MIL-STD-1750A Interrupt Unit | Dynex |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |