|

|

PDF MF0032M-11ATXX Data sheet ( Hoja de datos )

| Número de pieza | MF0032M-11ATXX | |

| Descripción | 8/16-bit Data Bus Flash ATA PC Card | |

| Fabricantes | Mitsubishi | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MF0032M-11ATXX (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

MITSUBISHI STORAGE CARD

Preliminary

8/16-bit Data Bus

Flash ATA PC Card

Connector Type

Two-piece 68-pin

ATA PC CARDS

MF0032M-11ATxx

MF0064M-11ATxx

MF0128M-11ATxx

MF0192M-11ATxx

MF0256M-11ATxx

MF0320M-11ATxx

MF0384M-11ATxx

MF0448M-11ATxx

MF0512M-11ATxx

DESCRIPTION

Mitsubishi’s Flash ATA cards provide large memory

capacities on a device approximately the size of a

credit card (85.6mm(L) × 54mm(W) × 3.3mm(T) or

5mm(T)). The cards use an 8/16 bit data bus.

Available in 32MB - 512MB capacities, Mitsubishi’s

Flash ATA cards conform to the JEIDA/PCMCIA

standard.

In default mode, the ATA card operates in PC Card

compliant sockets. It conforms to PCMCIA 2.1,JEIDA

4.2 and PC Card Standard.

When the OE# signal is asserted low level by the

Host system in power on cycle, the Mitsubishi’s Flash

ATA cards can be selected in a IDE ATA interface. It

uses the ATA command set so no software drivers

are required.

FEATURES

• 68pin PC Card Standard Type-I PC Card

• Single 5V or 3.3V Supply

• Card density of up to 512MB maximum

• Four PC Card ATA and IDE ATA modes

• Nonvolatile, No Batteries Required

• High reliability based on internal ECC function

• Fast read/write performance(Target)

<PC Card I/F>

Read:1.5MB/s

Write:1.6MB/s(128 - 512MB)

Write:850kB/s(64MB)

Write:450kB/s(32MB)

<IDE ATA I/F PIO=2>

Read:1.8MB/s

Write:1.7MB/s(128MB - 512MB)

Write:1.0MB/s(64MB)

Write:550kB/s(32MB)

• 300,000 program/erase cycles

APPLICATIONS

• Computers

• Digital Camera

• Data Communication

• Office Automation

• Industrial

• Consumer

MITSUBISHI

ELECTRIC

1

June.2001 Rev. 1.3

1 page

MITSUBISHI STORAGE CARD

Preliminary

MF0XXXX-11ATXX series

ATA PC CARDS

Signal Description(Continued)

Signal Name

Attribute Memory Select[REG#]

(PC Card Memory Mode)

Attribute Memory Select[REG#]

(PC Card I/O Mode)

Attribute Memory Select[REG#]

(IDE ATA Interface)

Battery Voltage Detect[BVD2]

(PC Card Memory Mode)

Audio Digital Waveform[SPKR#]

(PC Card I/O Mode)

DASP#

(IDE ATA Interface)

Card Reset[RESET]

(PC Card Memory Mode)

Card Reset[RESET]

(PC Card I/O Mode)

Card Reset[RESET#]

(IDE ATA Interface)

Wait[WAIT#]

(PC card Memory Mode)

Wait[WAIT#]

(PC card I/O Mode)

IORDY

(IDE ATA Interface)

Input Port Acknowledge[INPACK#]

(PC Card I/O Mode)

Input Port Acknowledge[INPACK#]

(IDE ATA Interface)

Battery Voltage Detect[BVD1]

(PC Card Memory Mode)

STSCHG#

(PC Card I/O Mode)

I/O

I

O

I/O

I

O

O

O

Pin No.

61

62

58

59

60

63

PDIAG#

(IDE ATA Interface)

Voltage Sense[VS1, VS2]

I/O

O 43, 57

Cable Select[CSEL]

(PC card Memory Mode)

Cable Select[CSEL]

(PC card I/O Mode)

Cable Select[CSEL]

(IDE ATA Interface)

- 56

-

I

Vcc

GND

- 17, 51

- 1, 34, 35, 68

Description

When this signal is asserted, access is limited to

Attribute Memory with OE#/WE# and I/O Space

with

IORD#/IOWR#.

This input signal is not used for this mode and

should be connected to Vcc by the host.

This output is driven to a high-level.

SPKR# is kept negated because this Card does not

have digital audio output.

This signal is the DISK Active/Slave Present signal

in the Master/Slave handshake protocol.

By assertion of this signal, all registers of this Card

are cleared. This signal should be kept to High-Z or

High Level by the host for at least 1ms after Vcc

applied.

This input pin is the active low hardware reset from

the host.

This signal is asserted to delay completion of the

memory or I/O access cycle.

This signal is asserted when the Card is selected

and can respond to an I/O Read cycle at the

address on the address bus.

This output is driven to a high-level.

This signal is asserted low to alert the host to

changes in the status of Configuration Status

Register in the Attribute Memory Space.

This signal is the Pass Diagnostic signal in the

Master/Slave handshake protocol.

VS1 is grounded so that the Card CIS can be read

at 3.3V and VS2 is N.C.

This signal is not used for this mode.

This signal is used to configure this Card as a

Master or a Slave. When this signal is grounded,

this Card is configured as a Master. When this

signal is Open, this Card is configure as a Slave.

5V or 3.3V power.

Ground.

MITSUBISHI

ELECTRIC

5

June.2001 Rev. 1.3

5 Page

MITSUBISHI STORAGE CARD

Preliminary

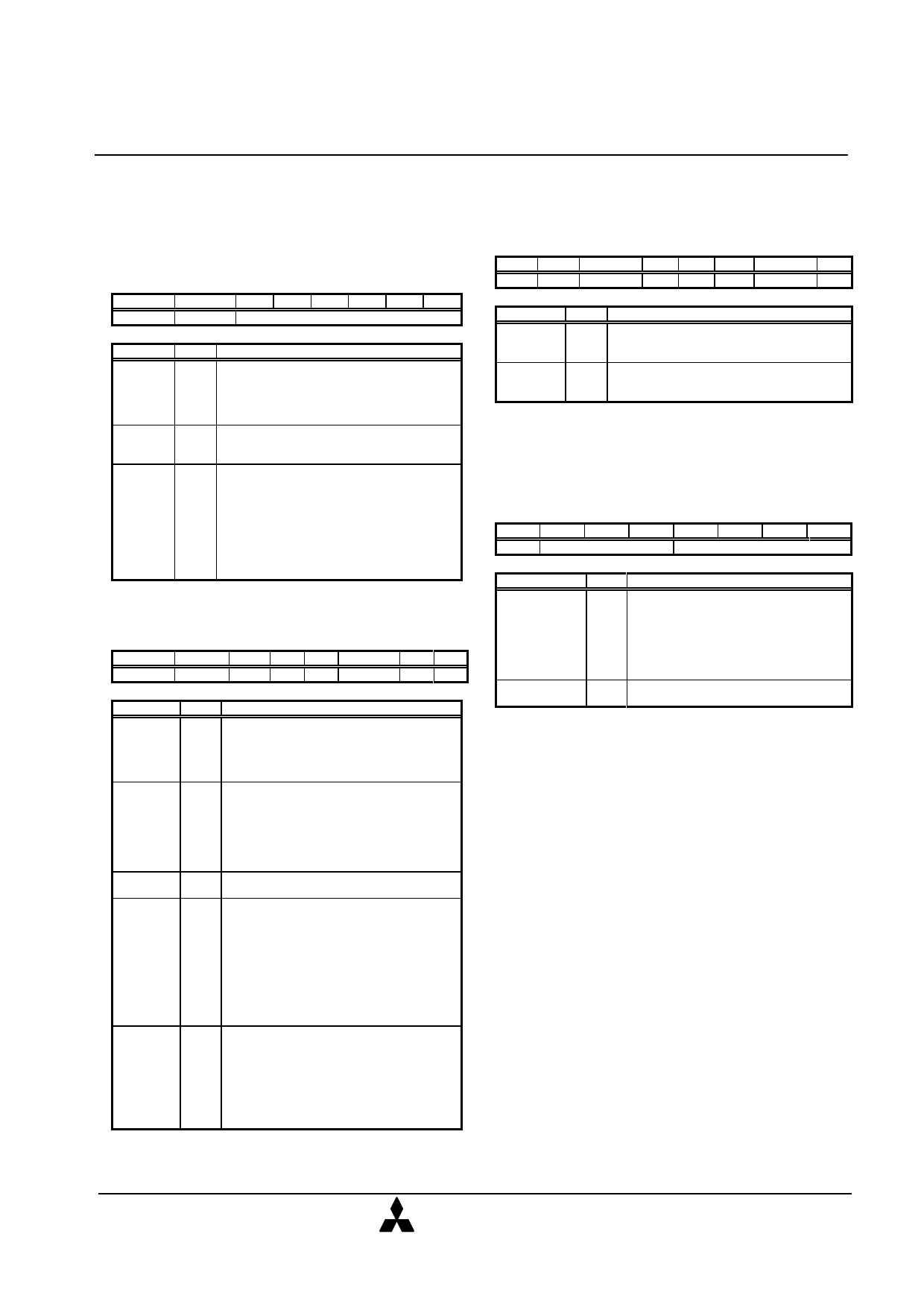

Configuration Register Specifications

Configuration Option Register

This register is used for the configuration of the card

configuration status and for the issuing soft reset to the

card.

D7 D6 D5 D4 D3 D2 D1 D0

SRESET LevIREQ

Index

Name

SRESET

LevIREQ

Index

R/W

R/W

R/W

R/W

Description

Setting this bit to “1”, places the card in the

reset state. When the host returns this bit to

“0”, the function shall enter the same

unconfigured, reset state as the card does

following a power-up and hardware reset.

If this bit is set to “0”, card generates pulse

mode interrupt. If this bit is set to “1”, card

generates level mode interrupts.

This bits is used for select operation mode of

the card as follows.

When Power on, Card Hard Reset and Soft

reset, this data is “000000” for the purpose of

Memory card interface recognition.

Index: 0 -> Memory mapped

1 -> Contiguous I/O mapped

2 -> Primary I/O mapped

3 -> Secondary I/O mapped

Configuration and Status Register

This register is used for observing the card state.

D7 D6 D5 D4 D3 D2 D1 D0

Changed SigChg Iois8 0 0 PwrDwn Intr 0

Name

Changed

SigChg

Iois8

PwrDwn

Intr

R/W

R/O

R/W

R/W

R/W

R/W

Description

This bit indicates that CREADY bit on the Pin

Replacement register is set to “1”. When

Changed bit is set to “1”, STSCHG# pin is

held “L” if the SigChg bit is “1” and the card is

configured for the I/O interface.

This bit is set or reset by the host for enabling

and disabling the status change

signal(STSCHG# pin). When the card is

configured I/O card interface and this bit is set

to “1”, STSCHG# pin is controlled by Changed

bit. If this bit is set to “0”, STSCHG# pin is

kept “H”.

This card is always configured for both 8-bit

and 16-bit I/O, so this bit is ignored.

When this bit is set to “1”, the card enters

Power Down mode. When this bit is reset to

“0”, the host is requesting the card to enter the

active mode. RREADY bit on Pin

Replacement Register becomes BUSY when

this bit is changed. RREADY will not become

Ready until the power state requested has

been entered. This card automatically powers

down when it is idle, and powers back up

when it receives a command.

This bit represents the internal state of the

interrupt request. This bit state is available

whether I/O card interface has been

configured or not. This signal remains true

until the condition which caused the interrupt

request has been serviced. If interrupts are

disabled by the nIEN bit in the Device Control

Register, this bit is a zero.

MF0XXXX-11ATXX series

ATA PC CARDS

Pin Replacement Register

This register is used for providing the signal state of

READY signal when the card configured I/O card

interface.

D7 D6

D5 D4 D3 D2

D1 D0

0 0 CREADY 0 1 1 RREADY 0

Name

CREADY

RREADY

R/W

R/W

R/W

Description

This bit is set to “1” when the RREADY bit

changes state. This bit may also be written by

the host.

When read, this bit indicates READY pin

states. When written, this bit acts as a mask

for writing the CREADY bit.

Socket and Copy Register

This register is used for identification of the card from

the other cards. Host can read and write this register.

This register should be set by host before this card’s

Configuration Option register set.

D7 D6 D5 D4 D3 D2 D1 D0

0 Copy Number

Socket Number

Name

Copy Number

Socket

Number

R/W

R/W

R/W

Description

This bit indicates the drive number of the

card for twin card configuration.

And the host can select and drive one card

by comparing the number in this field with

the drive number of Drive Head Register.

In the way, the host can perform the card’s

master/slave organization.

This field indicates to the card that it is

located in the n’th socket.

MITSUBISHI

ELECTRIC

11

June.2001 Rev. 1.3

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet MF0032M-11ATXX.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MF0032M-11ATXX | 8/16-bit Data Bus Flash ATA PC Card | Mitsubishi |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |