|

|

PDF 74LVX374MTC Data sheet ( Hoja de datos )

| Número de pieza | 74LVX374MTC | |

| Descripción | Low Voltage Octal D-Type Flip-Flop with 3-STATE Outputs | |

| Fabricantes | Fairchild Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 74LVX374MTC (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

October 1993

Revised March 1999

74LVX374

Low Voltage Octal D-Type Flip-Flop with

3-STATE Outputs

General Description

The LVX374 is a high-speed, low-power octal D-type flip-

flop featuring separate D-type inputs for each flip-flop and

3-STATE outputs for bus-oriented applications. A buffered

Clock (CP) and Output Enable (OE) are common to all flip-

flops. The inputs tolerate up to 7V allowing interface of 5V

systems to 3V systems.

Features

s Input voltage translation from 5V to 3V

s Ideal for low power/low noise 3.3V applications

s Guaranteed simultaneous switching noise level and

dynamic threshold performance

Ordering Code:

Order Number Package Number

Package Description

74LVX374M

M20B

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide

74LVX374SJ

74LVX374MTC

M20D

MTC20

20-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

20-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

Logic Symbols

Connection Diagram

IEEE/IEC

Pin Descriptions

Pin Names

D0–D7

CP

OE

O0–O7

Description

Data Inputs

Clock Pulse Input

3-STATE Output Enable Input

3-STATE Outputs

© 1999 Fairchild Semiconductor Corporation DS011612.prf

www.fairchildsemi.com

1 page

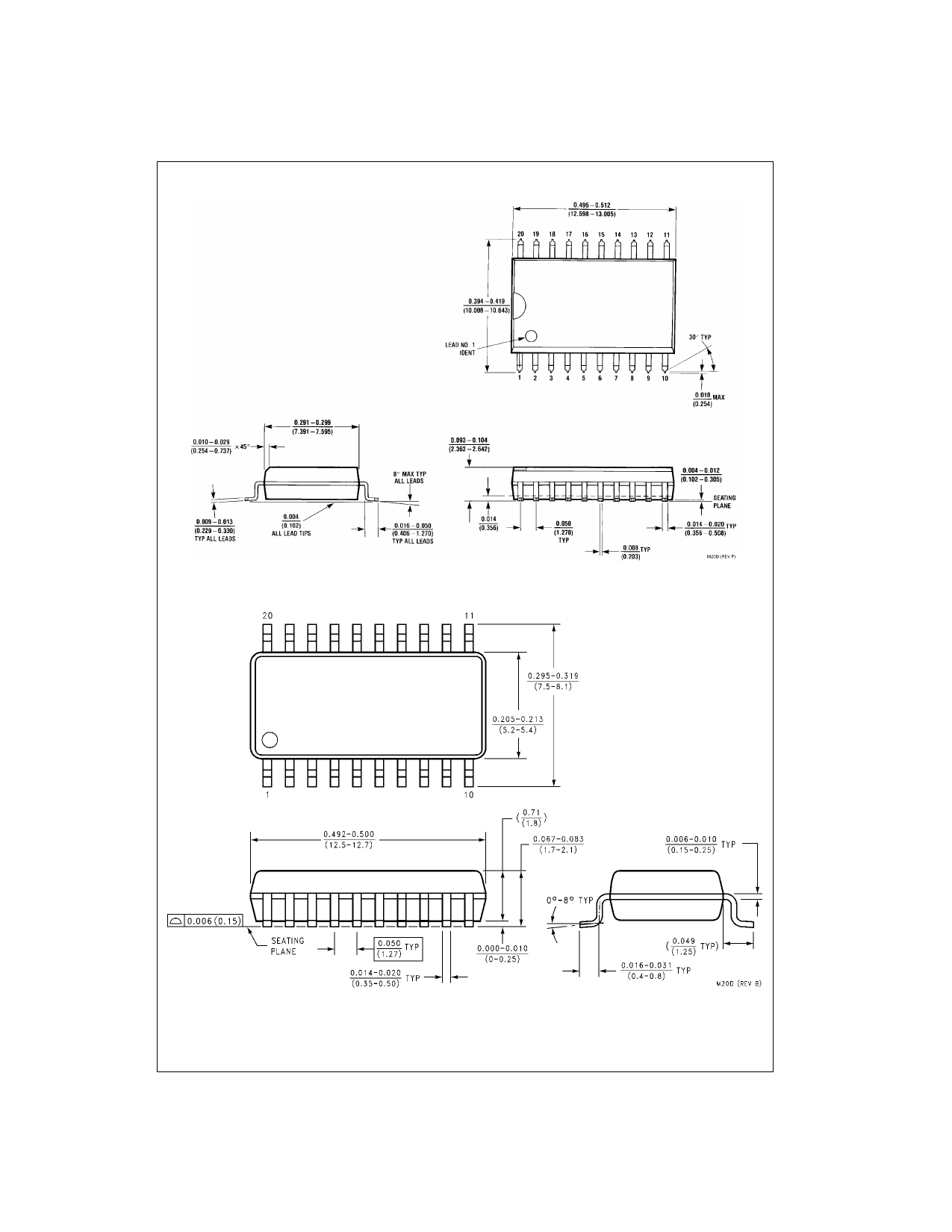

Physical Dimensions inches (millimeters) unless otherwise noted

20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300” Wide

Package Number M20B

20-Lead Small Outline Package (SOP) EIAJ TYPE II, 5.3mm Wide

Package Number M20D

5 www.fairchildsemi.com

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet 74LVX374MTC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 74LVX374MTC | Low Voltage Octal D-Type Flip-Flop with 3-STATE Outputs | Fairchild Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |