|

|

PDF ML2252 Data sheet ( Hoja de datos )

| Número de pieza | ML2252 | |

| Descripción | P Compatible 8-Bit A/D Converters with 2- or 8-Channel Multiplexer | |

| Fabricantes | Micro Linear | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ML2252 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

May 1997

ML2252*, ML2259**

µP Compatible 8-Bit A/D Converters

with 2- or 8-Channel Multiplexer

GENERAL DESCRIPTION

The ML2252 and ML2259 combine an 8-bit A/D

converter, 2- or 8-channel analog multiplexer, and a

microprocessor compatible 8-bit parallel interface and

control logic in a single monolithic CMOS device.

Easy interface to microprocessors is provided by the

latched and decoded multiplexer address inputs and a

double buffered three-state data bus. These analog-to-

digital converters allow the microprocessor to operate

completely asynchronous to the converter clock.

The built in sample and hold function provides the ability

to digitize a 5V, 50kHz sinewave to 8-bit accuracy. The

differential comparator design provides low power supply

sensitivity to DC and AC variations. The voltage reference

can be externally set to any value between ground and

VCC, thus allowing a full conversion over a relatively

small span. All parameters are guaranteed over

temperature with a power supply voltage of 5V ±10%.

The device is suitable for a wide range of applications

from process and machine control to consumer,

automotive, and telecommunication applications.

ML2252 BLOCK DIAGRAM

FEATURES

s Conversion time (fCLK = 1.46MHz); 6.6µs

s Total unadjusted error; ±1/2LSB or ±1LSB

s No missing codes

s Sample and hold; 390ns acquisition

s Capable of digitizing a 5V, 50kHz sinewave

s 2- or 8-channel input multiplexer

s 0V to 5V analog input range with single 5V

power supply

s Operates ratiometrically or with up to 5V

voltage reference

s No zero or full scale adjust required

s Analog input protection; 25mA per input min

s Continuous conversion mode

s Low power dissipation; 15mW max

s TTL and CMOS compatible digital inputs and outputs

* This Part Is Obsolete

** This Part Is End of Life As Of August 1, 2000

CH0

VCC

2-CHANNEL

CH1 MULTIPLEXER

ADDRESS

LATCH

AND

DECODER

ALE A0

CLOCK

CONTROL

& TIMING

+

Σ

–

8pF

+

COMP

–

SUCCESSIVE

APPROXIMATION

REGISTER

8pF

A/D WITH

SAMPLE-AND-HOLD FUNCTION

GND

D/A

CONVERTER

+VREF

–VREF

START

EOC

THREE

STATE

OUTPUT

BUFFER

DB0

DB1

DB2

DB3

DB4

DB5

DB6

DB7

OE

1

1 page

ML2252, ML2259

ELECTRICAL CHARACTERISTICS (Continued)

SYMBOL

PARAMETER

CONDITIONS

MIN

TYP

MAX

UNITS

AC and Dynamic Performance Characteristics (Note 5)

tACQ

fCLK

tC

SNR

THD

Sample and Hold Acquisition

Clock Frequency

Conversion Time

Signal to Noise Ratio

Total Harmonic Distortion

VIN = 51kHz, 5V sine.

fCLK = 1.46MHz

(fSAMPLING > 150kHz). Noise is sum

of all nonfundamental components

up to 1/2 of fSAMPLING

VIN = 51kHz, 5V sine.

fCLK = 1.46MHz

(fSAMPLING > 150kHz).

THD is sum 2, 3, 4, 5 harmonics

relative to fundamental

10

1/2 1/fCLK

1460

kHz

8.5 8.5 + 250ns 1/fCLK

47 dB

–60 dB

IMD

FR

Intermodulation Distortion

Frequency Response

VIN = fA + fB. fA = 49kHz, 2.5V sine.

fB = 47.8kHz, 2.5V sine,

fCLK = 1.46MHz

(fSAMPLING > 150kHz). IMD is (fA + fB),

(fA – fB), (2fA + fB), (2fA – fB), (fA + 2fB),

(fA – 2fB) relative to fundamental

VIN = 0 to 50kHz. 5V sine relative

to 1kHz

–60

0.1

dB

dB

tDC

tEOC

tWS

tSS

tWALE

Clock Duty Cycle

End of Conversion Delay

Start Pulse Width

Start Pulse Setup Time

Address Latch Enable

Pulse Width

(Note 6)

Synchronous only, (Note 7)

40 60 %

1/2 1/2 + 250ns 1/fCLK

50 ns

40 ns

50 ns

tS

tH

tH1, H0

t1H, 0H

CIN

COUT

Address Setup

Address Hold

Output Enable for DB0–DB7

Output Disable for DB0–DB7

Capacitance of Logic Input

Capacitance of Logic Outputs

Figure 1, CL = 50pF

Figure 1, CL = 10pF

Figure 1, CL = 50pF

Figure 1, CL = 10pF

0 ns

50 ns

100 ns

50 ns

100 ns

50 ns

5 pF

10 pF

Note 1:

Note 2:

Note 3:

Note 4:

Note 5:

Note 6:

Note 7:

Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

Total unadjusted error includes offset, full scale, linearity, multiplexer and sample and hold errors.

For –VREF • VIN (+) the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input which will forward conduct for analog input voltages

one diode drop below ground or one diode drop greater than the VCC supply. Be careful, during testing at low VCC levels (4.5V), as high level analog inputs (5V) can

cause this input diode to conduct — especially at elevated temperatures, and cause errors for analog inputs near full scale. The spec allow 100mV forward bias of either

diode. This means that as long as the analog VIN or VREF does not exceed the supply voltage by more than 100mV, the output code will be correct. To achieve an

absolute 0VDC to 5VDC input voltage range will therefore require a minimum supply voltage of 4.900VDC over temperature variations, initial tolerance and loading.

Leakage current is measured with the clock not switching.

CL = 50pF, timing measured at 50% point.

A 40% to 60% clock duty cycle range insures proper operation at all clock frequencies. In the case that an available clock has a duty cycle outside of these limits,

the minimum time the clock is high or the minimum time the clock is low must be at least 40ns. The maximum time the clock can be high or low is 60µs.

The conversion start setup time requirement only needs to be satisfied if a conversion must be synchronized to a given clock rising edge. If the setup time is not met,

start conversion will have an uncertainty of one clock pulse.

5

5 Page

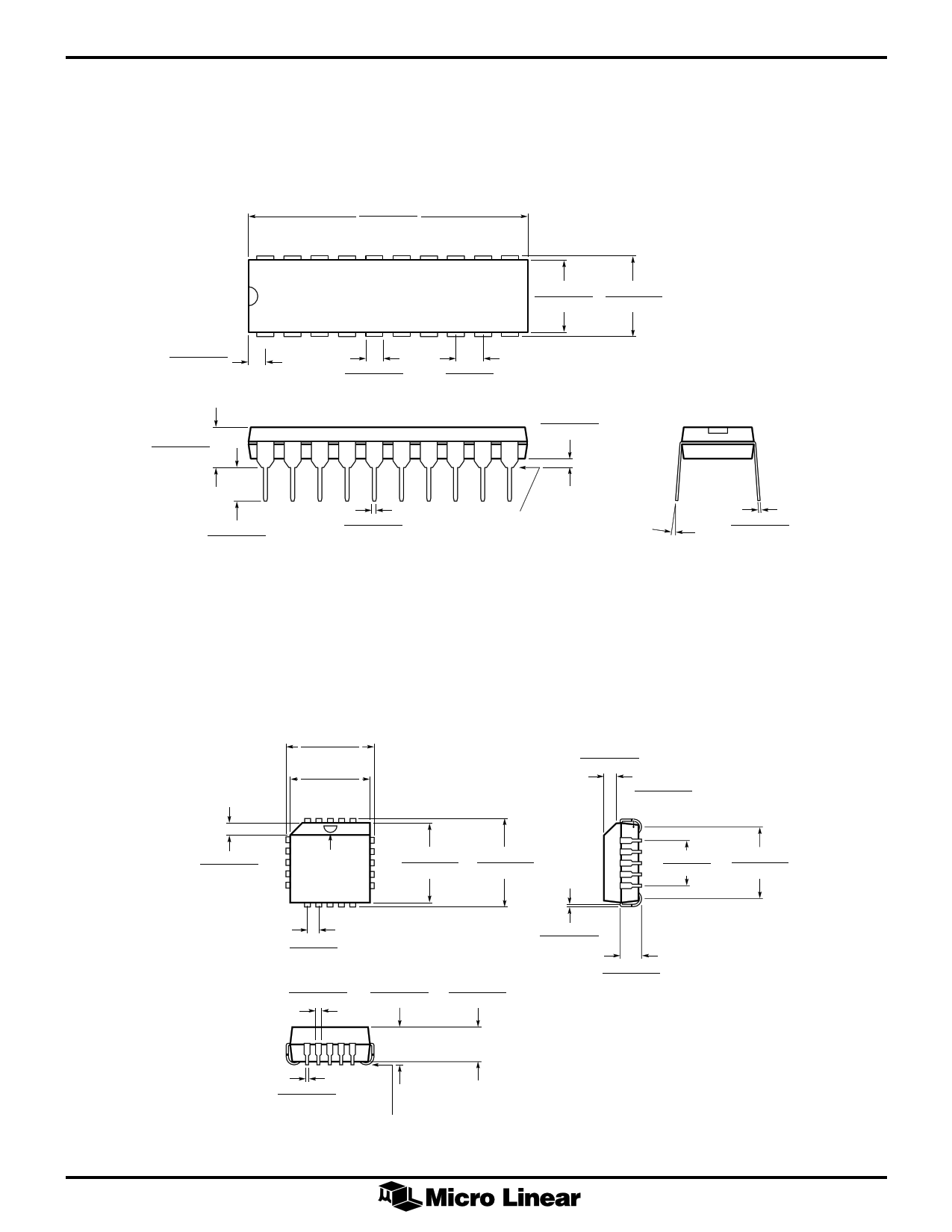

PHYSICAL DIMENSIONS inches (millimeters)

ML2252, ML2259

20

PIN 1 ID

0.060 MIN

(1.52 MIN)

(4 PLACES)

1

0.170 MAX

(4.32 MAX)

Package: P20

20-Pin PDIP

1.010 - 1.035

(25.65 - 26.29)

0.240 - 0.260 0.295 - 0.325

(6.09 - 6.61) (7.49 - 8.26)

0.055 - 0.065

(1.40 - 1.65)

0.100 BSC

(2.54 BSC)

0.015 MIN

(0.38 MIN)

0.125 MIN

(3.18 MIN)

0.016 - 0.022

(0.40 - 0.56)

SEATING PLANE

0º - 15º

0.008 - 0.012

(0.20 - 0.31)

0.385 - 0.395

(9.78 - 10.03)

0.350 - 0.356

(8.89 - 9.04)

1

Package: Q20

20-Pin PLCC

0.042 - 0.056

(1.07 - 1.42)

0.025 - 0.045

(0.63 - 1.14)

(RADIUS)

0.042 - 0.048 6

(1.07 - 1.22)

PIN 1 ID

16

0.350 - 0.356

(8.89 - 9.04)

0.385 - 0.395

(9.78 - 10.03)

0.200 BSC 0.290 - 0.330

(5.08 BSC) (7.36 - 8.38)

11

0.050 BSC

(1.27 BSC)

0.026 - 0.032

(0.66 - 0.81)

0.165 - 0.180 0.146 - 0.156

(4.19 - 4.57) (3.71 - 3.96)

0.009 - 0.011

(0.23 - 0.28)

0.100 - 0.110

(2.54 - 2.79)

0.013 - 0.021

(0.33 - 0.53)

SEATING PLANE

11

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet ML2252.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ML2252 | P Compatible 8-Bit A/D Converters with 2- or 8-Channel Multiplexer | Micro Linear |

| ML2258 | P Compatible 8-Bit A/D Converter with 8-Channel Multiplexer | Micro Linear |

| ML2258BIP | P Compatible 8-Bit A/D Converter with 8-Channel Multiplexer | Micro Linear |

| ML2258BIQ | P Compatible 8-Bit A/D Converter with 8-Channel Multiplexer | Micro Linear |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |