|

|

PDF NJ8820 Data sheet ( Hoja de datos )

| Número de pieza | NJ8820 | |

| Descripción | FREQUENCY SYNTHESISER (PROM INTERFACE) | |

| Fabricantes | Zarlink Inc | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de NJ8820 (archivo pdf) en la parte inferior de esta página. Total 11 Páginas | ||

|

No Preview Available !

This product is obsolete.

This information is available for your

convenience only.

For more information on

Zarlink’s obsolete products and

replacement product lists, please visit

http://products.zarlink.com/obsolete_products/

1 page

NJ8820

PIN DESCRIPTIONS

Pin no. Name

Description

1 PDA Analog output from the sample and hold phase comparator for use as a ‘fine’ error signal. Output at

(VDD2VSS)/2 when the system is in lock. Voltage increases as fv phase lead increases; voltage

decreases as fr phase lead increases. Output is linear over only a narrow phase window, determined

by gain (programmed by RB).

2 PDB Three-state output from the phase/frequency detector for use as a ‘coarse’ error signal.

fv. fr or fv leading: positive pulses with respect to the bias point VBIAS

fv , fr or fr leading: negative pulses with respect to the bias point VBIAS

fv = fr and phase error within PDA window: high impedance.

3 LD An open-drain lock detect output at low level when phase error is within PDA window (in lock); high

impedance at all other times.

4 FIN The input to the main counters, normally driven from a prescaler, which may be AC-coupled or, when

a full logic swing is available, may be DC-coupled.

5 VSS Negative supply (ground).

6 VDD Positive supply.

7, 8 OSC IN/ These pins form an on-chip reference oscillator when a series resonant crystal is connected across

OSC OUT them. Capacitors of appropriate value are also required between each end of the crystal and ground

to provide the necessary additional phase shift. An external reference signal may, alternatively, be

applied to OSC IN. This may be a low-level signal, AC-coupled, or if a full logic swing is available it may

be DC-coupled. The program range of the reference counter is 3 to 2047, with the division ratio being

twice the programmed number.

9,10, 11, 12 D0-D3 Information on these inputs is transferred to the internal data latches during the appropriate data read

time slot. D3 is MSB, D0 is LSB.

13 ME An open drain output for use in controlling the power supply to an external ROM or PROM. ME is low

during the data read period and high impedance at other times.

14 PE A positive or negative pulse or edge AC-coupled into this pin initiates the single-shot data read

procedure. Grounding this pin repeats the data read procedure in a cyclic manner.

15, 16, 17 DS0-DS2 Internally generated three-state data select outputs, which may be used to address external memory.

18 MC Modulus control output for controlling an external dual-modulus prescaler. MC will be low at the beginning

of a count cycle and will remain low until the ‘A’ counter completes its cycle. MC then goes high and

remains high until the ‘M’ counter completes its cycle, at which point both ‘A’ and ‘M’ counters are reset.

This gives a total division ratio of MP1A, where P and P11 represent the dual-modulus prescaler

values. The program range of the ‘A’ counter is 0-127 and therefore can control prescalers with a

division ratio up to and including 4128/129. The programming range of the ‘M’ counter is 8-1023

and, for correct operation, M>A. Where every possible channel is required, the minimum total division

ratio should be P 22P.

19 RB An external sample and hold phase comparator gain programming resistor should be connected

between this pin and VSS.

20 CH An external hold capacitor should be connected between this pin and VSS.

2·0

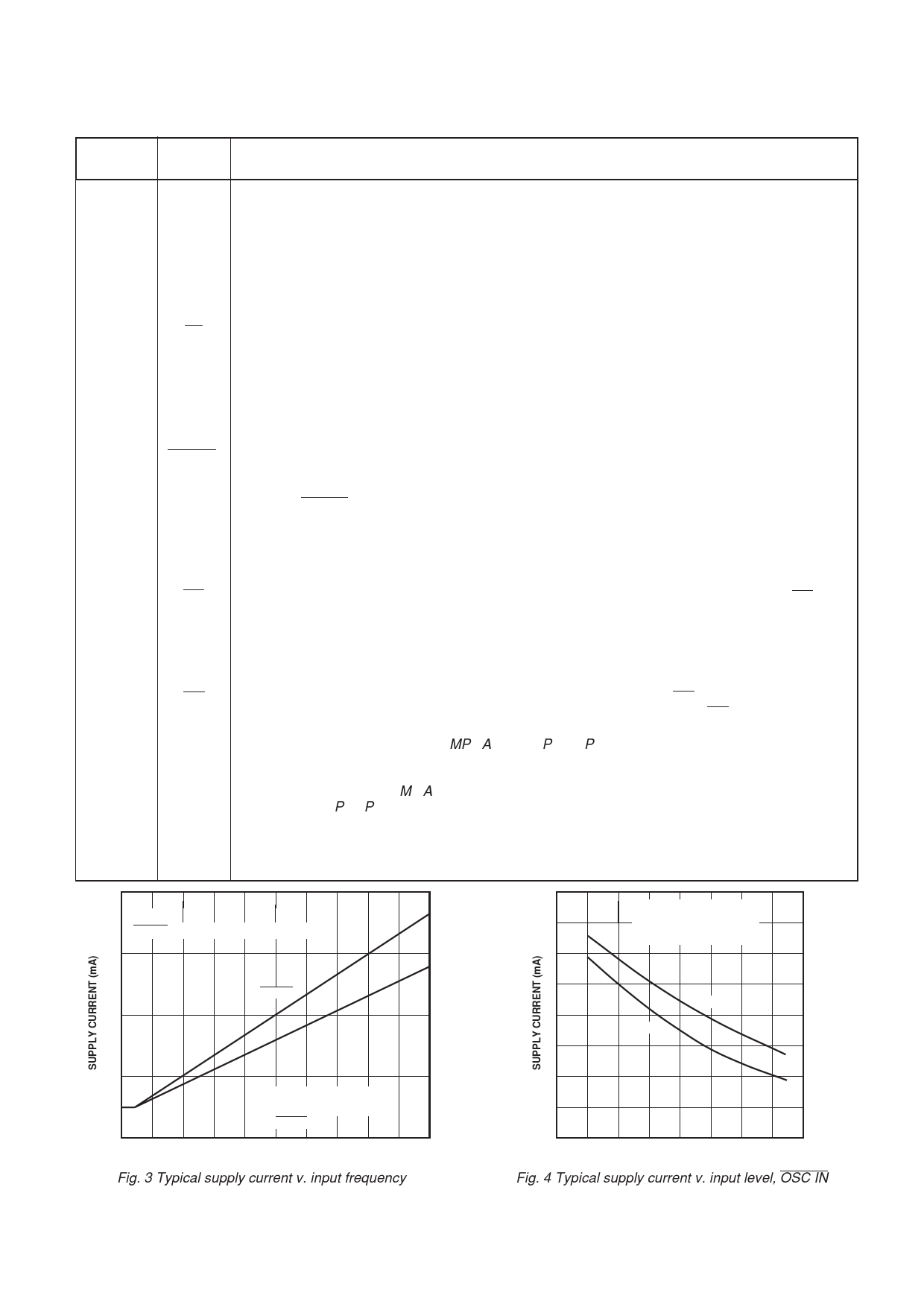

VDD = 5V

OSC IN, FIN = 0V TO 5V SQUARE WAVE

1·5

8

VDD = 5V

7 FIN = LOW FREQUENCY

0V TO 5V SQUARE WAVE

6

OSC IN

1·0

FIN

5

10MHz

4

1MHz

3

0·5

TOTAL SUPPLY CURRENT IS

THE SUM OF THAT DUE TO FIN

AND OSC IN

12 34 5 6789

INPUT FREQUENCY (MHz)

Fig. 3 Typical supply current v. input frequency

10

2

1

0·2 0·4 0·6 0·8 1·0 1·2 1·4 1·6

INPUT LEVEL (V RMS)

Fig. 4 Typical supply current v. input level, OSC IN

3

5 Page

For more information about all Zarlink products

visit our Web Site at

www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively “Zarlink”) is believed to be reliable.

However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such

information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or

use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual

property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in

certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part

of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other

information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the

capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute

any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and

suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does

not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in

significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink’s conditions of sale which are available on request.

Purchase of Zarlink’s I2C components conveys a licence under the Philips I2C Patent rights to use these components in and I2C System, provided that the system

conforms to the I2C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE

11 Page | ||

| Páginas | Total 11 Páginas | |

| PDF Descargar | [ Datasheet NJ8820.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NJ8820 | FREQUENCY SYNTHESISER (PROM INTERFACE) | Zarlink Inc |

| NJ8821 | FREQUENCY SYNTHESISER (MICROPROCESSOR INTERFACE) WITH RESETTABLE COUNTERS | Zarlink Inc |

| NJ8821 | FREQUENCY SYNTHESISER | General Electric Company |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |