|

|

PDF 83C754 Data sheet ( Hoja de datos )

| Número de pieza | 83C754 | |

| Descripción | 80C51 8-bit microcontroller family 4K/256 OTP/ROM/ DAC/ comparator/ UART/ reference | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de 83C754 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

83C754/87C754

80C51 8-bit microcontroller family

4K/256 OTP/ROM, DAC, comparator, UART, reference

Preliminary specification

Supersedes data of 1997 Dec 03

IC20 Data Handbook

1998 Apr 23

Philips

Semiconductors

1 page

Philips Semiconductors

80C51 8-bit microcontroller family

4K/256 OTP/ROM, DAC, comparator, UART, reference

Preliminary specification

83C754/87C754

OSCILLATOR CHARACTERISTICS

X1 and X2 are the input and output, respectively, of an inverting

amplifier which can be configured for use as an on-chip oscillator.

To drive the device from an external clock source, X1 should be

driven while X2 is left unconnected. There are no requirements on

the duty cycle of the external clock signal, because the input to the

internal clock circuitry is through a divide-by-two flip-flop. However,

minimum and maximum high and low times specified in the data

sheet must be observed.

IDLE MODE

The 8XC754 includes the 80C51 power-down and idle mode

features. In idle mode, the CPU puts itself to sleep while all of the

on-chip peripherals stay active. The instruction to invoke the idle

mode is the last instruction executed in the normal operating mode

before the idle mode is activated. The CPU contents, the on-chip

RAM, and all of the special function registers remain intact during

this mode. The idle mode can be terminated either by any enabled

interrupt (at which time the process is picked up at the interrupt

service routine and continued), or by a hardware reset which starts

the processor in the same manner as a power-on reset. Upon

powering-up the circuit, or exiting from idle mode, sufficient time

must be allowed for stabilization of the internal analog reference

voltages before a D/A conversion is started.

Special Function Registers

The special function registers (directly addressable only) contain all

of the 8XC754 registers except the program counter and the four

register banks. Most of the special function registers are used to

control the on-chip peripheral hardware. Other registers include

arithmetic registers (ACC, B, PSW), stack pointer (SP) and data

pointer registers (DPH, DPL). Twelve of the SFRs are bit

addressable.

Data Pointer

The data pointer (DPTR) consists of a high byte (DPH) and a low

byte (DPL). In the 80C51 this register allows the access of external

data memory using the MOVX instruction. Since the 83C754 does

not support MOVX or external memory accesses, this register is

generally used as a 16-bit offset pointer of the accumulator in a

MOVC instruction. DPTR may also be manipulated as two

independent 8-bit registers.

POWER-DOWN MODE

In the power-down mode, the oscillator is stopped and the

instruction to invoke power-down is the last instruction executed.

Only the contents of the on-chip RAM are preserved. A hardware

reset is the only way to terminate the power-down mode. The control

bits for the reduced power modes are in the special function register

PCON.

Table 1. External Pin Status During Idle and

Power-Down Modes

MODE

Port 1

Port 3

Idle

Data

Data

Power-down

Data

Data

STANDARD SERIAL INTERFACE

The serial port is full duplex, meaning it can transmit and receive

simultaneously. It is also receive-buffered, meaning it can

commence reception of a second byte before a previously received

byte has been read from the register. (However, if the first byte still

has not been read by the time reception of the second byte is

complete, one of the bytes will be lost.) The serial port receive and

transmit registers are both accessed at Special Function Register

SBUF. Writing to SBUF loads the transmit register, and reading

SBUF accesses a physically separate receive register.

The serial port can operate in 4 modes:

Mode 0: Serial data enters and exits through RxD. TxD outputs the

shift clock. 8 bits are transmitted/received (LSB first). The

baud rate is fixed at 1/12 the oscillator frequency.

Mode 1: 10 bits are transmitted (through TxD) or received (through

RxD): a start bit (0), 8 data bits (LSB first), and a stop bit

(1). On Receive, the stop bit goes into RB8 in Special

Function Register SCON. The baud rate is variable.

Mode 2: 11 bits are transmitted (through TxD) or received (through

RxD): a start bit (0), 8 data bits (LSB first), a

programmable 9th data bit, and a stop bit (1). On Transmit,

the 9th data bit (TB8 in SCON) can be assigned the value

of 0 or 1. Or, for example, the parity bit (P, in the PSW)

could be moved into TB8. On Receive, the 9th data bit

goes into RB8 in Special Function Register SCON, while

the stop bit is ignored. The baud rate is programmable to

either 1/32 or 1/64 the oscillator frequency.

Mode 3: 11 its are transmitted (through TxD) or received (through

RxD): a start bit (0), 8 data bits (LSB first), a

programmable 9th data bit, and a stop bit (1). In fact,

Mode 3 is the same as Mode 2 in all respects except baud

rate. the baud rate in Mode 3 is variable.

In all four modes, transmission is initiated by any instruction that

uses SBUF as a destination register. Reception is initiated in Mode 0

by the condition RI = 0 and REN = 1. Reception is initiated in the

other modes by the incoming start bit if REN = 1.

Multiprocessor Communications

Modes 2 and 2 have a special provision for multiprocessor

communications. In these modes, 9 data bits are received. The 9th

one goes into RB8. Then comes a stop bit. The port can be

programmed such that when the stop bit is received, the serial port

interrupt will be activated only if RB8 = 1. This feature is enabled by

setting bit SM2 in SCON. A way to use this feature in multiprocessor

systems is as follows:

When the master processor wants to transmit a block of data to one

of several slaves, it first sends out an address byte which identifies

the target slave. An address byte differs from a data byte in that the

9th bit is 1 in an address byte and 9 in a data byte. With SM2 = 1,

no slave will be interrupted by a data byte. An address byte,

however, will interrupt all slaves, so that each slave can examine the

received byte and see if it is being addressed. The addressed slave

will clear its SM2 bit and prepare to receive the data bytes that will

be coming. The slaves that were not being addressed leave their

SM2s set, and go on about their business, ignoring the coming data

bytes.

SM2 has no effect in Mode 0, and in Mode 1 can be used to check

the validity of the stop bit. In a Mode 1 reception, if SM2 = 1, the

receive interrupt will not be activated unless a valid stop bit is

received.

1998 Apr 23

5

5 Page

Philips Semiconductors

80C51 8-bit microcontroller family

4K/256 OTP/ROM, DAC, comparator, UART, reference

Preliminary specification

83C754/87C754

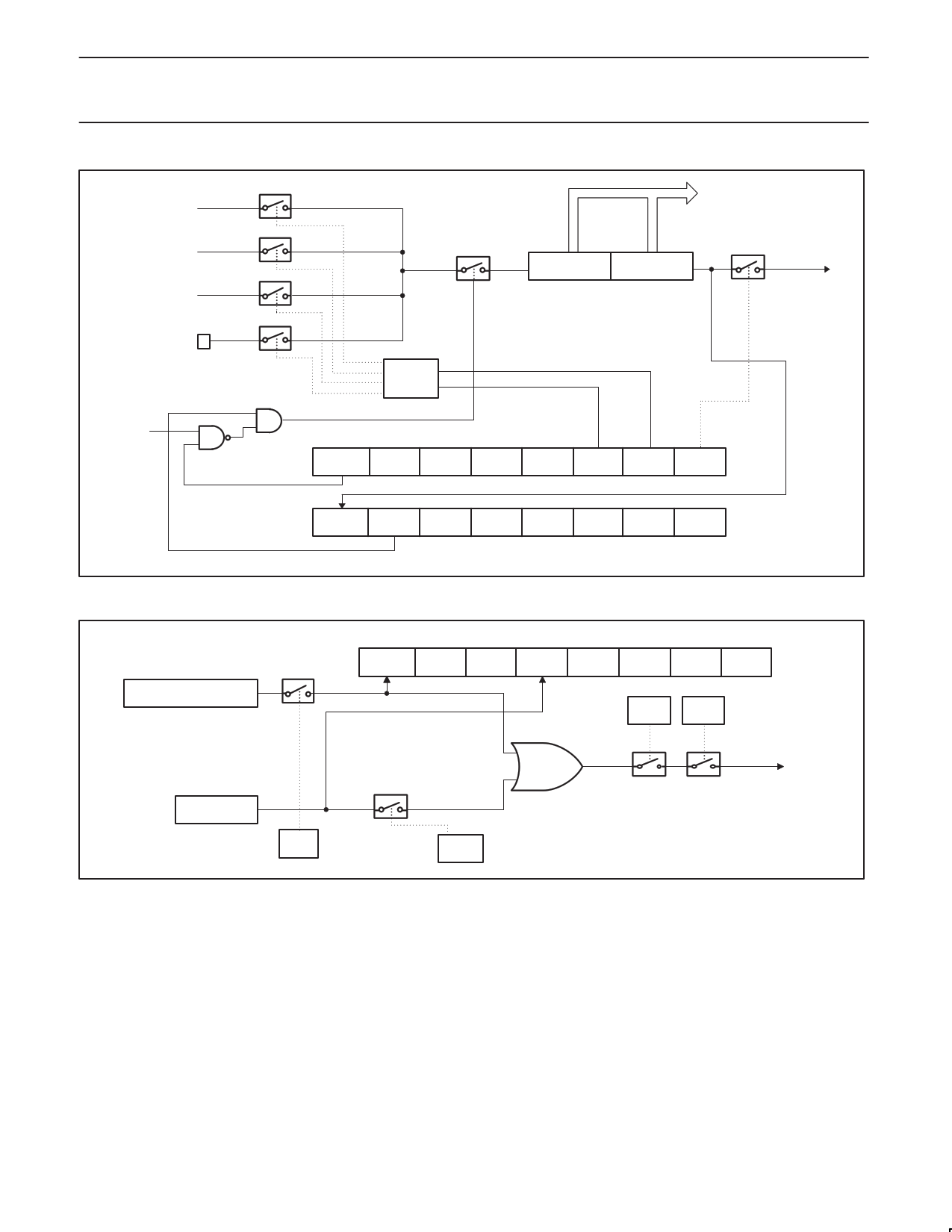

OSC/12

OSC/4

TIMER 0

OVERFLOW

EXTERNAL INPUT

(P3.6/ECI)

IDLE

TO PCA

MODULES

CH CL

16–BIT UP COUNTER

OVERFLOW

INTERRUPT

00

01

10 DECODE

11

CIDL WDTE

––

––

––

CPS1

CPS0

ECF

CMOD

(D9H)

CF

CR –– CCF ––

––

––

––

CCON

(D8H)

Figure 6. PCA Timer/Counter

SU00673B

PCA TIMER/COUNTER

PCA MODULE

CMOD.0 ECF

CF

CR

–– CCF ––

––

––

––

CCON

(D8H)

IE.6 IE.7

EC EA

TO

INTERRUPT

PRIORITY

DECODER

CCAPM ECCFn

Figure 7. PCA Interrupt System

SU00674A

1998 Apr 23

11

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet 83C754.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 83C750 | 80C51 8-bit microcontroller family 1K/64 OTP ROM/ low pin count | NXP Semiconductors |

| 83C750 | 80C51 8-bit microcontroller family 1K/64 OTP ROM/ low pin count | NXP Semiconductors |

| 83C751 | 80C51 8-bit microcontroller family 2K/64 OTP/ROM/ I2C/ low pin count | NXP Semiconductors |

| 83C751 | 80C51 8-bit microcontroller family 2K/64 OTP/ROM/ I2C/ low pin count | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |