|

|

PDF 90S2343 Data sheet ( Hoja de datos )

| Número de pieza | 90S2343 | |

| Descripción | 8-Bit Microcontroller with 2K Bytes of In-System Programmable Flash | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 90S2343 (archivo pdf) en la parte inferior de esta página. Total 11 Páginas | ||

|

No Preview Available !

Features

• Utilizes the AVR ® Enhanced RISC Architecture

• AVR - High Performance and Low Power RISC Architecture

• 118 Powerful Instructions - Most Single Clock Cycle Execution

• 2K bytes of In-System Programmable ISP Flash

– SPI Serial Interface for In-System Programming

– Endurance: 1,000 Write/Erase Cycles

• 128 bytes EEPROM

– Endurance: 100,000 Write/Erase Cycles

• 128 bytes Internal RAM

• 32 x 8 General Purpose Working Registers

– 3 AT90S/LS2323 Programmable I/O Lines

– 5 AT90S/LS2343 Programmable I/O Lines

• VCC: 4.0 - 6.0V AT90S2323/AT90S2343

• VCC: 2.7 - 6.0V AT90LS2323/AT90LS2343

• Power-On Reset Circuit

• Speed Grades: 0 - 10 MHz AT90S2323/AT90S2343

• Speed Grades: 0 - 4 MHz AT90LS2323/AT90LS2343

• Up to 10 MIPS Throughput at 10 MHz

• One 8-Bit Timer/Counter with Separate Prescaler

• External and Internal Interrupt Sources

• Programmable Watchdog Timer with On-Chip Oscillator

• Low Power Idle and Power Down Modes

• Programming Lock for Flash Program and EEPROM Data Security

• Selectable On-Chip RC Oscillator

• 8-Pin Device

Description

The AT90S/LS2323 and AT90S/LS2343 is a low-power CMOS 8-bit microcontrollers

based on the AVR ® enhanced RISC architecture. By executing powerful instructions

in a single clock cycle, the AT90S/LS2323 and AT90S/LS2343 achieves throughputs

approaching 1 MIPS per MHz allowing the system designer to optimize power con-

sumption versus processing speed.

The AVR core combines a rich instruction set with 32 general purpose working regis-

ters. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU),

allowing two independent registers to be accessed in one single instruction executed

in one clock cycle. The resulting architecture is more code efficient while achieving

throughputs up to ten times faster than conventional CISC microcontrollers.

8-Bit

Microcontroller

with 2K Bytes of

In-System

Programmable

Flash

AT90S2323

AT90LS2323

AT90S2343

AT90LS2343

Preliminary

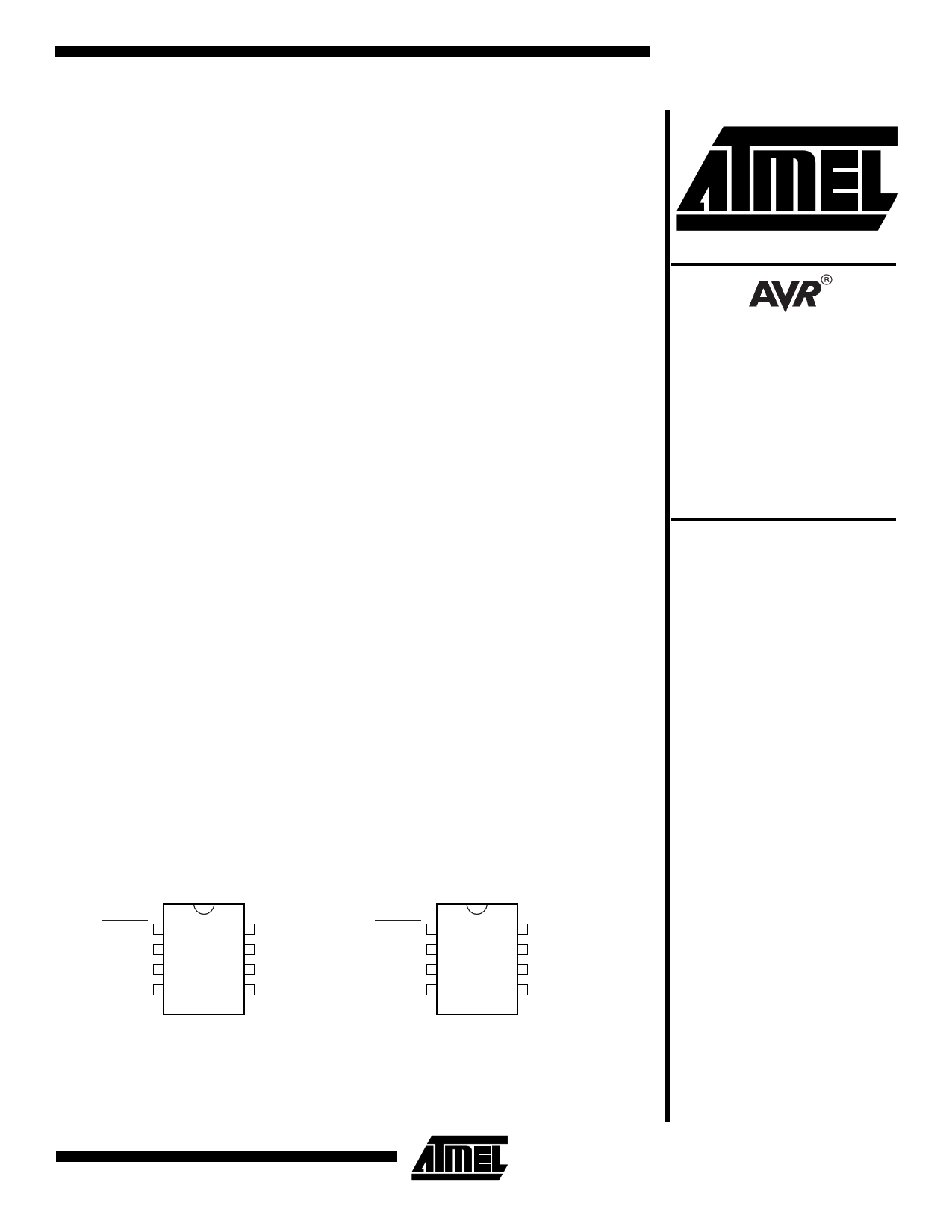

AT90S/LS2323

Pin Configuration

PDIP/SOIC

RESET

(CLOCK) PB3

PB4

GND

1

2

3

4

8 VCC

RESET 1

7 PB2 (SCK/T0) XTAL1 2

6 PB1 (MISO/INT0) XTAL2 3

5 PB0 (MOSI)

GND 4

8 VCC

7 PB2 (SCK/T0)

6 PB1 (MISO/INT0)

5 PB0 (MOSI)

AT90S/LS2343

AT90S/LS2323

Rev. 1004AS–05/98

Note: This is a summary document. For the complete 34 page

document, please visit our website at www.atmel.com

[email protected] and request literature #1004A.

or

e-mail

at

1

1 page

AT90S/LS2323 and AT90S/LS2343

AT90S/LS2323 and AT90S/LS2343

Architectural Overview

The fast-access register file concept contains 32 x 8-bit

general purpose working registers with a single clock cycle

access time. This means that during one single clock cycle,

one ALU (Arithmetic Logic Unit) operation is executed. Two

operands are output from the register file, the operation is

executed, and the result is stored back in the register file -

in one clock cycle.

Six of the 32 registers can be used as three 16-bits indirect

address register pointers for Data Space addressing-

enabling efficient address calculations. One of the three

address pointers is also used as the address pointer for the

constant table look up function. These added function reg-

isters are the 16-bit X-register, Y-register and Z-register.

The ALU supports arithmetic and logic functions between

registers or between a constant and a register. Single reg-

ister operations are also executed in the ALU. Figure 5

shows the AT90S/LS2323 and AT90S/LS2343 AVR

Enhanced RISC microcontroller architecture.

In addition to the register operation, the conventional mem-

ory addressing modes can be used on the register file as

well. This is enabled by the fact that the register file is

assigned the 32 lowermost Data Space addresses ($00 -

$1F), allowing them to be accessed as though they were

ordinary memory locations.

The I/O memory space contains 64 addresses for CPU

peripheral functions as Control Registers, Timer/Counters,

A/D-converters, and other I/O functions. The I/O memory

can be accessed directly, or as the Data Space locations

following those of the register file, $20 - $5F.

The AVR has Harvard architecture - with separate memo-

ries and buses for program and data. The program memory

is accessed with a two stage pipeline. While one instruction

is being executed, the next instruction is pre-fetched from

the program memory. This concept enables instructions to

be executed in every clock cycle. The program memory is

in-system downloadable Flash memory.

With the relative jump and call instructions, the whole 1K

address space is directly accessed. Most AVR instructions

have a single 16-bit word format. Every program memory

address contains a 16- or 32-bit instruction.

During interrupts and subroutine calls, the return address

program counter (PC) is stored on the stack. The stack is

effectively allocated in the general data SRAM, and conse-

quently the stack size is only limited by the total SRAM size

and the usage of the SRAM. All user programs must initial-

ize the SP in the reset routine (before subroutines or inter-

rupts are executed). The 8-bit stack pointer SP is read/write

accessible in the I/O space.

The 128 bytes data SRAM + register file and I/O registers

can be easily accessed through the five different address-

ing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear

and regular memory maps.

5

5 Page

Packaging Information

8P3, 8-Lead, 0.300" Wide,

Plastic Dual Inline Package (PDIP)

Dimensions in Inches and (Millimeters)

JEDEC STANDARD MS-001 BA

.400 (10.16)

.355 (9.02)

PIN

1

.300 (7.62) REF

.280 (7.11)

.240 (6.10)

.037 (.940)

.027 (.690)

.210 (5.33) MAX

SEATING

PLANE

.100 (2.54) BSC

.150 (3.81)

.115 (2.92)

.070 (1.78)

.045 (1.14)

.015 (.380) MIN

.022 (.559)

.014 (.356)

.012 (.305)

.008 (.203)

.325 (8.26)

.300 (7.62)

0

15

REF

.430 (10.9) MAX

8S2, 8-Lead, 0.200" Wide,

Plastic Gull Wing Small Outline (EIAJ SOIC)

Dimensions in Inches and (Millimeters)

.020 (.508)

.012 (.305)

PIN 1

.213 (5.41) .330 (8.38)

.205 (5.21) .300 (7.62)

.050 (1.27) BSC

.212 (5.38)

.203 (5.16)

.080 (2.03)

.070 (1.78)

.013 (.330)

.004 (.102)

0

8

REF

.035 (.889)

.020 (.508)

.010 (.254)

.007 (.178)

11 AT90S/LS2323 and AT90S/LS2343

11 Page | ||

| Páginas | Total 11 Páginas | |

| PDF Descargar | [ Datasheet 90S2343.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 90S2343 | 8-Bit Microcontroller with 2K Bytes of In-System Programmable Flash | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |