|

|

PDF ST24LC21 Data sheet ( Hoja de datos )

| Número de pieza | ST24LC21 | |

| Descripción | 1Kb x8 DUAL MODE SERIAL EEPROM for VESA Plug&Play | |

| Fabricantes | ST Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ST24LC21 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

ST24LC21

1Kb (x8) DUAL MODE SERIAL EEPROM

for VESA Plug&Play

1 MILLION ERASE/WRITE CYCLES

40 YEARS DATA RETENTION

2.5V to 5.5V SINGLE SUPPLY VOLTAGE

400k Hz COMPATIBILITY OVER the FULL

RANGE of SUPPLY VOLTAGE

TWO WIRE SERIAL INTERFACE I2C BUS

COMPATIBLE

PAGE WRITE (up to 8 BYTES)

BYTE, RANDOM and SEQUENTIAL READ

MODES

SELF TIMED PROGRAMMING CYCLE

AUTOMATIC ADDRESS INCREMENTING

ENHANCED ESD/LATCH UP

PERFORMANCES

ST24LC21 is replaced by the ST24LC21B

DESCRIPTION

The ST24LC21 is a 1K bit electrically erasable

programmable memory (EEPROM), organized by

8 bits.This device can operate in two modes: Trans-

mit Only mode and I2C bidirectional mode. When

powered, the device is in Transmit Only mode with

EEPROM data clocked out from the rising edge of

the signal applied on VCLK.

The device will switch to the I2C bidirectional mode

upon the falling edge of the signal applied on SCL

pin. The ST24LC21 cannot switch from the I2C

bidirectional mode to the Transmit Only mode (ex-

cept when the power supply is removed). The

device operates with a power supply value as low

as 2.5V. Both Plastic Dual-in-Line and Plastic Small

Outline packages are available.

NOT FOR NEW DESIGN

8

1

PSDIP8 (B)

0.25mm Frame

8

1

SO8 (M)

Figure 1. Logic Diagram

VCC

SCL

VCLK

ST24LC21

SDA

Table 1. Signal Names

SDA

SCL

Serial Data Address Input/Output

Serial Clock (I2C mode)

VCC Supply Voltage

VSS Ground

VCLK

Clock Transmit only mode

VSS

AI01489

June 1997

This is information on a product still in production but not recommended for new designs.

1/18

1 page

ST24LC21

SIGNAL DESCRIPTIONS

I2C Serial Clock (SCL). The SCL input pin is used

to synchronize all data in and out of the memory. A

resistor can be connected from the SCL line to VCC

to act as a pull up (see Figure 5).

Transmit Only Clock (VCLK). The VCLK input pin

is used to synchronize data out when the

ST24LC21 is in Transmit Only mode. The VCLK

input offers also a Write Enable (active high) func-

tion when the ST24LC21 is in I2C bidirectional

mode.

Serial Data (SDA). The SDA pin is bi-directional

and is used to transfer data in or out of the memory.

It is an open drain output that may be wire-OR’ed

with other open drain or open collector signals on

the bus. Aresistor must be connected from the SDA

bus line to VCC to act as pull up (see Figure 5).

DEVICE OPERATION

I2C Bus Background

The ST24LC21 supports the I2C protocol. This

protocol defines any device that sends data onto

the bus as a transmitter and any device that reads

the data as a receiver. The device that controls the

data transfer is known as the master and the other

as the slave. The master will always initiate a data

transfer and will provide the serial clock for syn-

chronisation. The ST24LC21 are always slave de-

vices in all communications.

Start Condition. START is identified by a high to

low transition of the SDA line while the clock SCL

is stable in the high state. A START condition must

precede any command for data transfer. Except

during a programming cycle, the ST24LC21 con-

tinuously monitor the SDA and SCL signals for a

START condition and will not respond unless one

is given.

Stop Condition. STOP is identified by a low to high

transition of the SDA line while the clock SCL is

stable in the high state. A STOP condition termi-

nates communication between the ST24LC21 and

the bus master. A STOP condition at the end of a

Read command forces the standby state. A STOP

condition at the end of a Write command triggers

the internal EEPROM write cycle.

Acknowledge Bit (ACK). An acknowledge signal

is used to indicate a successfull data transfer. The

bus transmitter, either master or slave, will release

the SDA bus after sending 8 bits of data. During the

9th clock pulse period the receiver pulls the SDA

bus low to acknowledge the receipt of the 8 bits of

data.

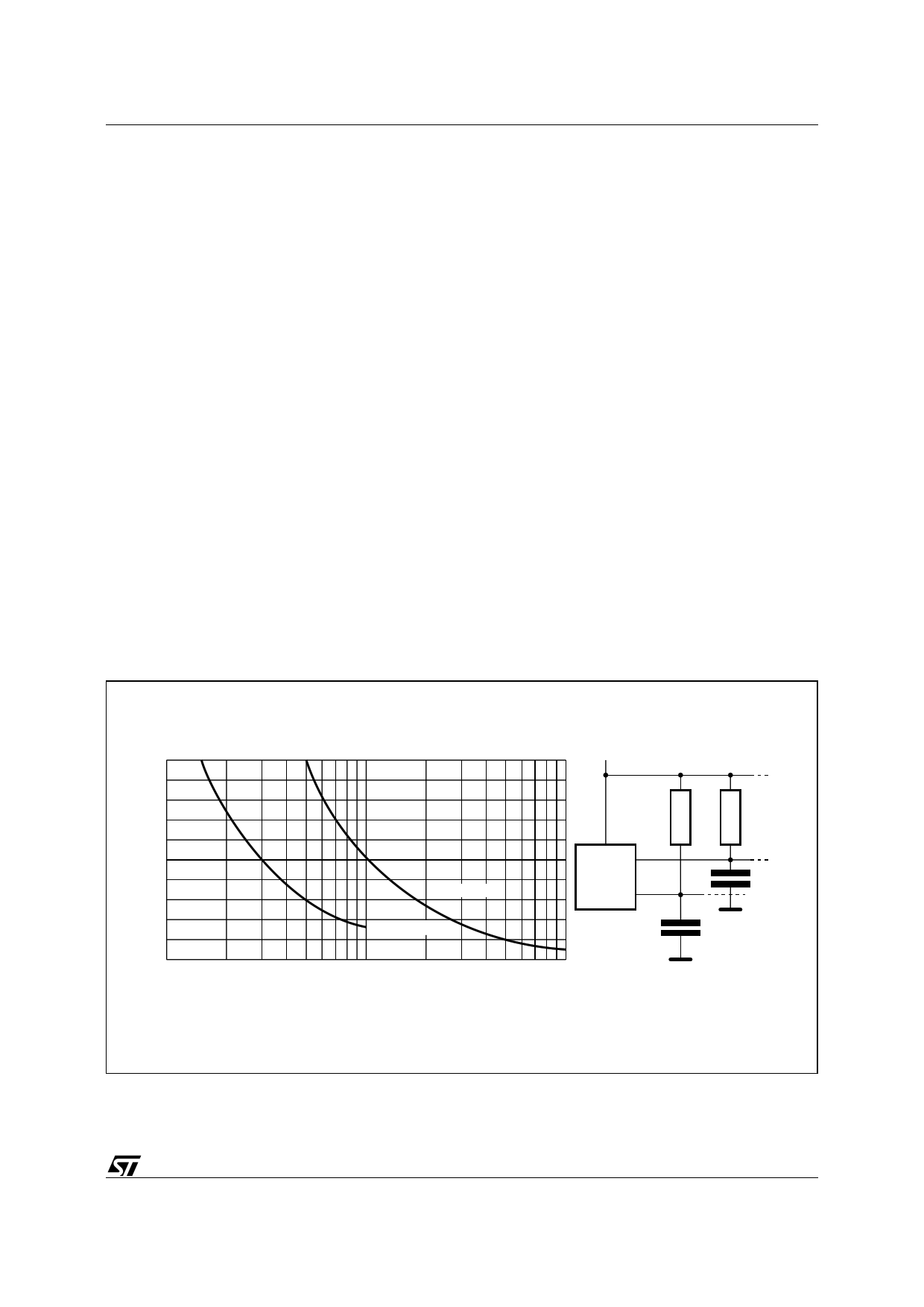

Figure 5. Maximum RL Value versus Bus Capacitance (CBUS) for an I2C Bus

20

16

12

8

4

0

10

VCC

fc = 100kHz

fc = 400kHz

100

CBUS (pF)

SDA

MASTER

SCL

RL

RL

CBUS

1000

CBUS

AI01665

5/18

5 Page

Figure 9. Write Cycle Polling using ACK

WRITE Cycle

in Progress

START Condition

DEVICE SELECT

with RW = 0

First byte of instruction

with RW = 0 already

decoded by ST24xxx

NO ACK

Returned

YES

Next

NO Operation is

Addressing the

Memory

ReSTART

YES

Send

Byte Address

STOP

ST24LC21

Proceed

WRITE Operation

Proceed

Random Address

READ Operation

AI01099B

DEVICE OPERATIONS (cont’d)

After each byte is transfered, the internal byte

address counter (3 least significant bits only) is

incremented. The transfer is terminated by the

master generating a STOP condition. Care must be

taken to avoid address counter ’roll-over’ which

could result in data being overwritten. Note that, for

any write mode, the generation by the master of the

STOP condition starts the internal memory pro-

gram cycle. All inputs are disabled until the comple-

tion of this cycle and the memory will not respond

to any request.

Minimizing System Delays by Polling On ACK.

During the internal write cycle, the memory discon-

nects itself from the bus in order to copy the data

from the internal latches to the memory cells. The

maximum value of the write time (tW) is given in the

AC Characteristics table, since the typical time is

shorter, the time seen by the system may be re-

duced by an ACK polling sequence issued by the

master. The sequence is as follows:

– Initial condition: a Write is in progress (see Figure

9).

– Step 1: the Master issues a START condition

followed by a Device Select byte (1st byte of the

new instruction).

– Step 2: if the memory is busy with the internal

write cycle, no ACK will be returned and the

master goes back to Step 1. If the memory has

terminated the internal write cycle, it will respond

with an ACK, indicating that the memory is ready

to receive the second part of the next instruction

(the first byte of this instruction was already sent

during Step 1).

11/18

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet ST24LC21.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ST24LC21 | 1Kb x8 DUAL MODE SERIAL EEPROM for VESA Plug&Play | ST Microelectronics |

| ST24LC21B | (ST24xx21B) 1 Kbit x8 Dual Mode Serial EEPROM | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |