|

|

PDF ST24C16 Data sheet ( Hoja de datos )

| Número de pieza | ST24C16 | |

| Descripción | 16 Kbit Serial I2C Bus EEPROM with User-Defined Block Write Protection | |

| Fabricantes | ST Microelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ST24C16 (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

ST24C16, ST25C16

ST24W16, ST25W16

16 Kbit Serial I2C Bus EEPROM

with User-Defined Block Write Protection

1 MILLION ERASE/WRITE CYCLES, with

40 YEARS DATA RETENTION

SINGLE SUPPLY VOLTAGE:

– 4.5V to 5.5V for ST24x16 versions

– 2.5V to 5.5V for ST25x16 versions

HARDWARE WRITE CONTROL VERSIONS:

ST24W16 and ST25W16

TWO WIRE SERIAL INTERFACE, FULLY I2C

BUS COMPATIBLE

BYTE and MULTIBYTE WRITE (up to 8

BYTES) for the ST24C16

PAGE WRITE (up to 16 BYTES)

BYTE, RANDOM and SEQUENTIAL READ

MODES

SELF TIMED PROGRAMING CYCLE

AUTOMATIC ADDRESS INCREMENTING

ENHANCED ESD/LATCH UP

PERFORMANCES

8

1

PSDIP8 (B)

0.25mm Frame

8

1

SO8 (M)

150mil Width

Figure 1. Logic Diagram

DESCRIPTION

This specification covers a range of 16 Kbit I2C bus

EEPROM products, the ST24/25C16 and the

ST24/25W16. In the text, products are referred to

as ST24/25x16 where "x" is: "C" for Standard ver-

sion and "W" for hardware Write Control version.

The ST24/25x16 are 16 Kbit electrically erasable

programmable memories (EEPROM), organized

as 8 blocks of 256 x8 bits. These are manufactured

in STMicroelectronics’s Hi-Endurance Advanced

CMOS technology which guarantees an endur-

Table 1. Signal Names

PRE

PB0, PB1

SDA

SCL

MODE

WC

VCC

VSS

Write Protect Enable

Protect Block Select

Serial Data Address Input/Output

Serial Clock

Multybyte/Page Write Mode

(C version)

Write Control (W version)

Supply Voltage

Ground

VCC

2

PB0-PB1

PRE

SCL

MODE/WC*

ST24x16

ST25x16

SDA

VSS

AI00866B

Note: WC signal is only available for ST24/25W16 products.

February 1999

1/17

1 page

ST24/25C16, ST24/25W16

Table 5. Input Parameters (1) (TA = 25 °C, f = 100 kHz )

Symbol

Parameter

Test Condition

CIN Input Capacitance (SDA)

CIN Input Capacitance (other pins)

ZWCL

WC Input Impedance (ST24/25W16)

VIN ≤ 0.3 VCC

ZWCH

WC Input Impedance (ST24/25W16)

VIN ≥ 0.7 VCC

tLP

Low-pass filter input time constant

(SDA and SCL)

Note: 1. Sampled only, not 100% tested.

Min Max Unit

8 pF

6 pF

5 20 kΩ

500 kΩ

100 ns

Table 6. DC Characteristics

(TA = 0 to 70 °C or –40 to 85 °C; VCC = 4.5V to 5.5V or 2.5V to 5.5V)

Symbol

Parameter

Test Condition

ILI Input Leakage Current

0V ≤ VIN ≤ VCC

ILO Output Leakage Current

0V ≤ VOUT ≤ VCC

SDA in Hi-Z

Supply Current (ST24 series)

ICC

Supply Current (ST25 series)

VCC = 5V, fC = 100kHz

(Rise/Fall time < 10ns)

VCC = 2.5V, fC = 100kHz

ICC1

Supply Current (Standby)

(ST24 series)

VIN = VSS or VCC,

VCC = 5V

VIN = VSS or VCC,

VCC = 5V, fC = 100kHz

ICC2

Supply Current (Standby)

(ST25 series)

VIN = VSS or VCC,

VCC = 2.5V

VIN = VSS or VCC,

VCC = 2.5V, fC = 100kHz

VIL Input Low Voltage (SCL, SDA)

VIH Input High Voltage (SCL, SDA)

VIL

Input Low Voltage

(PB0 - PB1, PRE, MODE, WC)

VIH

Input High Voltage

(PB0 - PB1, PRE, MODE, WC)

VOL Output Low Voltage (ST24 series) IOL = 3mA, VCC = 5V

Output Low Voltage (ST25 series) IOL = 2.1mA, VCC = 2.5V

Min Max

±2

±2

2

1

100

300

5

–0.3

0.7 VCC

–0.3

50

0.3 VCC

VCC + 1

0.5

VCC – 0.5 VCC + 1

0.4

0.4

Unit

µA

µA

mA

mA

µA

µA

µA

µA

V

V

V

V

V

V

5/17

5 Page

ST24/25C16, ST24/25W16

Write Protection. Data in the upper four blocks of

256 bytes of the memory may be write protected.

The memory is write protected between a boundary

address and the top of memory (address

7FFh).The boundary address is user defined by

writing it in the Block Address Pointer (location

7FFh).

The Block Address Pointer is an 8 bit EEPROM

register located at the address 7FFh. It is com-

posed by 4 MSBs Address Pointer, which defines

the bottom boundary address, and 4 LSBs which

must be programmed at ’0’. This Address Pointer

can therefore address a boundary by page of 16

bytes.

The block in which the Block Address Pointer de-

fines the boundary of the write protected memory

is defined by the logic level applied on the PB1 and

PB0 input pins:

– PB1 =’0’and PB0 =’0’ select block 4

– PB1 =’0’and PB0 =’1’ select block 5

– PB1 =’1’and PB0 =’0’ select block 6

– PB1 =’1’and PB0 =’1’ select block 7

The following sequence should be used to set the

Write Protection:

– write the data to be protected into the top of

the memory, up to, but not including, location

7FFh;

– select the block by hardwiring the signals PB0

& PB1;

– set the protection by writing the correct bottom

boundary address in the Address Pointer (4

MSBs of location 7FFh) with bit b2 (Protect

Flag) set to ’0’.

Note that for a correct fonctionality of the memory,

all the 4 LSBs of the Block Address Pointer must

also be programmed at ’0’. The area will be pro-

tected when the PRE input is taken High.

Remark: The Write Protection is active if and only

if the PRE input pin is driven High and the bit 2 of

location 7FFh is set to ’0’. In all the other cases, the

memory Block will not be protected. While the PRE

input pin is read at ’0’ by the memory, the location

7FFh can be used as a normal EEPROM byte.

Caution: Special attention must be used when

using the protect mode together with the Multibyte

Write mode (MODE input pin High). If the Multibyte

Write starts at the location right below the first byte

of the Write Protected area, then the instruction will

write over the first 7 bytes of the Write Protected

area. The area protected is therefore smaller than

the content defined in the location 7FFh, by 7 bytes.

This does not apply to the Page Write mode as the

address counter ’roll-over’ and thus cannot go

above the 16 bytes lower boundary of the protected

area.

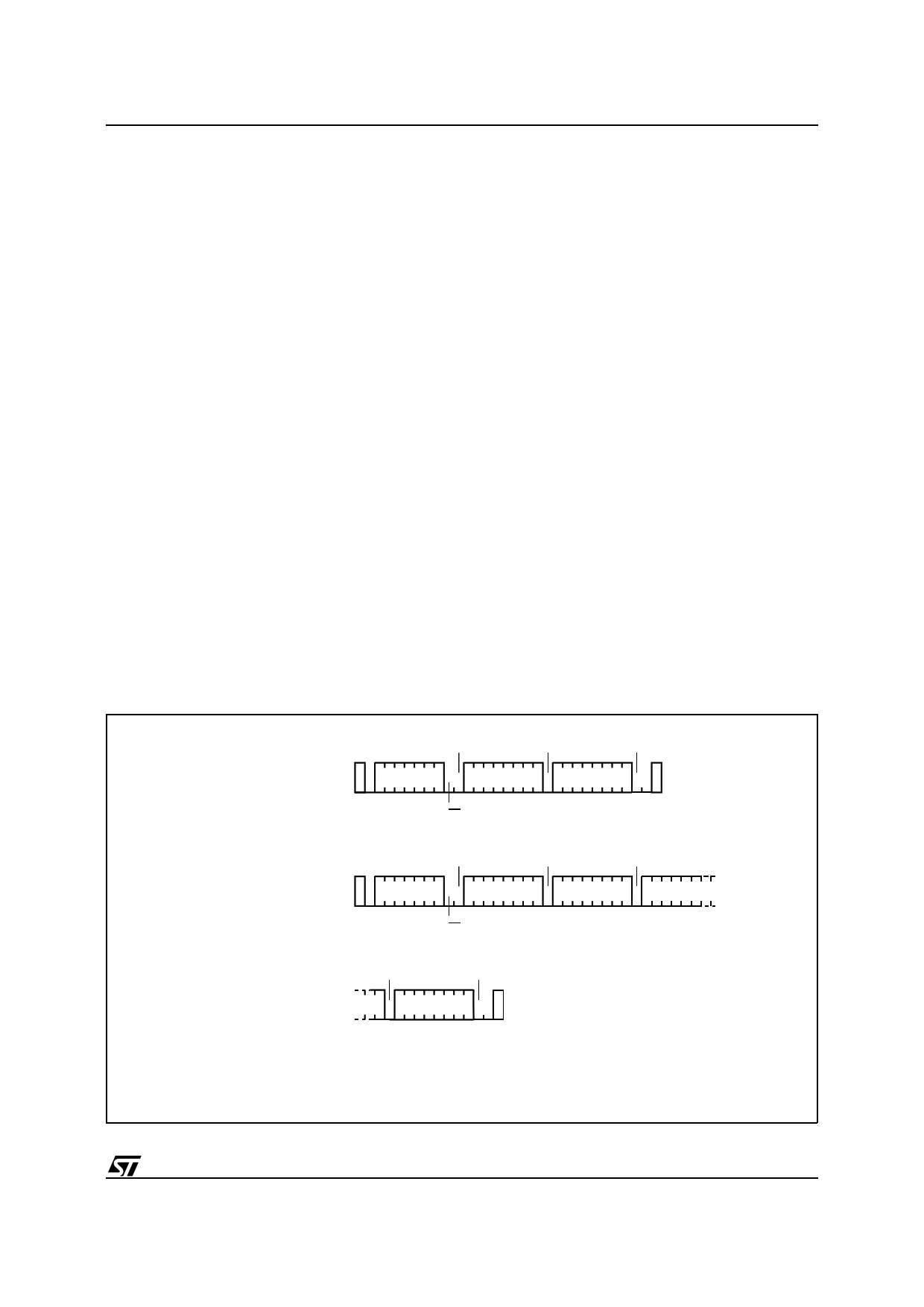

Figure 9. Write Modes Sequence (ST24/25C16)

BYTE WRITE

MULTIBYTE

AND

PAGE WRITE

ACK

ACK

ACK

DEV SEL

BYTE ADDR

DATA IN

R/W

ACK

ACK

ACK

DEV SEL

BYTE ADDR DATA IN 1

DATA IN 2

R/W

ACK

ACK

DATA IN N

AI00793

11/17

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet ST24C16.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ST24C16 | 16 Kbit Serial I2C Bus EEPROM with User-Defined Block Write Protection | ST Microelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |