|

|

PDF MTB6N60E1 Data sheet ( Hoja de datos )

| Número de pieza | MTB6N60E1 | |

| Descripción | TMOS POWER FET 6.0 AMPERES 600 VOLTS | |

| Fabricantes | Motorola Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de MTB6N60E1 (archivo pdf) en la parte inferior de esta página. Total 8 Páginas | ||

|

No Preview Available !

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Product Preview

TMOS E-FET.™

High Energy Power FET

D2PAK-SL Straight Lead

N–Channel Enhancement–Mode Silicon Gate

This advanced TMOS E–FET is designed to withstand high

energy in the avalanche and commutation modes. The new energy

efficient design also offers a drain–to–source diode with a fast

recovery time. Designed for low voltage, high speed switching

applications in power supplies, converters and PWM motor

controls, these devices are particularly well suited for bridge circuits

where diode speed and commutating safe operating areas are

critical and offer additional safety margin against unexpected

voltage transients.

• Robust High Voltage Termination

• Avalanche Energy Specified

• Source–to–Drain Diode Recovery Time Comparable to a

Discrete Fast Recovery Diode

• Diode is Characterized for Use in Bridge Circuits

• IDSS and VDS(on) Specified at Elevated Temperature

• Short Heatsink Tab Manufactured — Not Sheared

• Specially Designed Leadframe for Maximum Power Dissipation

G

Order this document

by MTB6N60E1/D

MTB6N60E1

Motorola Preferred Device

TMOS POWER FET

6.0 AMPERES

600 VOLTS

RDS(on) = 1.2 OHM

®

D

CASE 418C–01, Style 2

D2PAK–SL

S

MAXIMUM RATINGS (TC = 25°C unless otherwise noted)

Rating

Drain–to–Source Voltage

Drain–to–Gate Voltage (RGS = 1.0 MΩ)

Gate–Source Voltage — Continuous

Gate–Source Voltage — Non–Repetitive (tp ≤ 10 ms)

Drain Current — Continuous

Drain Current — Continuous @ 100°C

Drain Current — Single Pulse (tp ≤ 10 µs)

Total Power Dissipation @ 25°C

Derate above 25°C

Total Power Dissipation @ TA = 25°C (1)

Operating and Storage Temperature Range

Single Pulse Drain–to–Source Avalanche Energy — Starting TJ = 25°C

(VDD = 100 Vdc, VGS = 10 Vdc, Peak IL = 9.0 Apk, L = 10 mH, RG = 25 Ω)

Thermal Resistance — Junction to Case

Thermal Resistance — Junction to Ambient

Thermal Resistance — Junction to Ambient (1)

Maximum Lead Temperature for Soldering Purposes, 1/8″ from case for 10 seconds

(1) When surface mounted to an FR4 board using the minimum recommended pad size.

Symbol

VDSS

VDGR

VGS

VGSM

ID

ID

IDM

PD

TJ, Tstg

EAS

RθJC

RθJA

RθJA

TL

Value

600

600

± 20

± 40

6.0

4.6

18

125

1.0

2.5

– 55 to 150

405

1.0

62.5

50

260

This document contains information on a product under development. Motorola reserves the right to change or discontinue this product without notice.

E–FET is a trademark of Motorola, Inc. TMOS is a registered trademark of Motorola, Inc.

Preferred devices are Motorola recommended choices for future use and best overall value.

Unit

Vdc

Vdc

Vdc

Vpk

Adc

Apk

Watts

W/°C

Watts

°C

mJ

°C/W

°C

REV 1

©MMoottoororolal,aInTc.M19O9S7 Power MOSFET Transistor Device Data

1

1 page

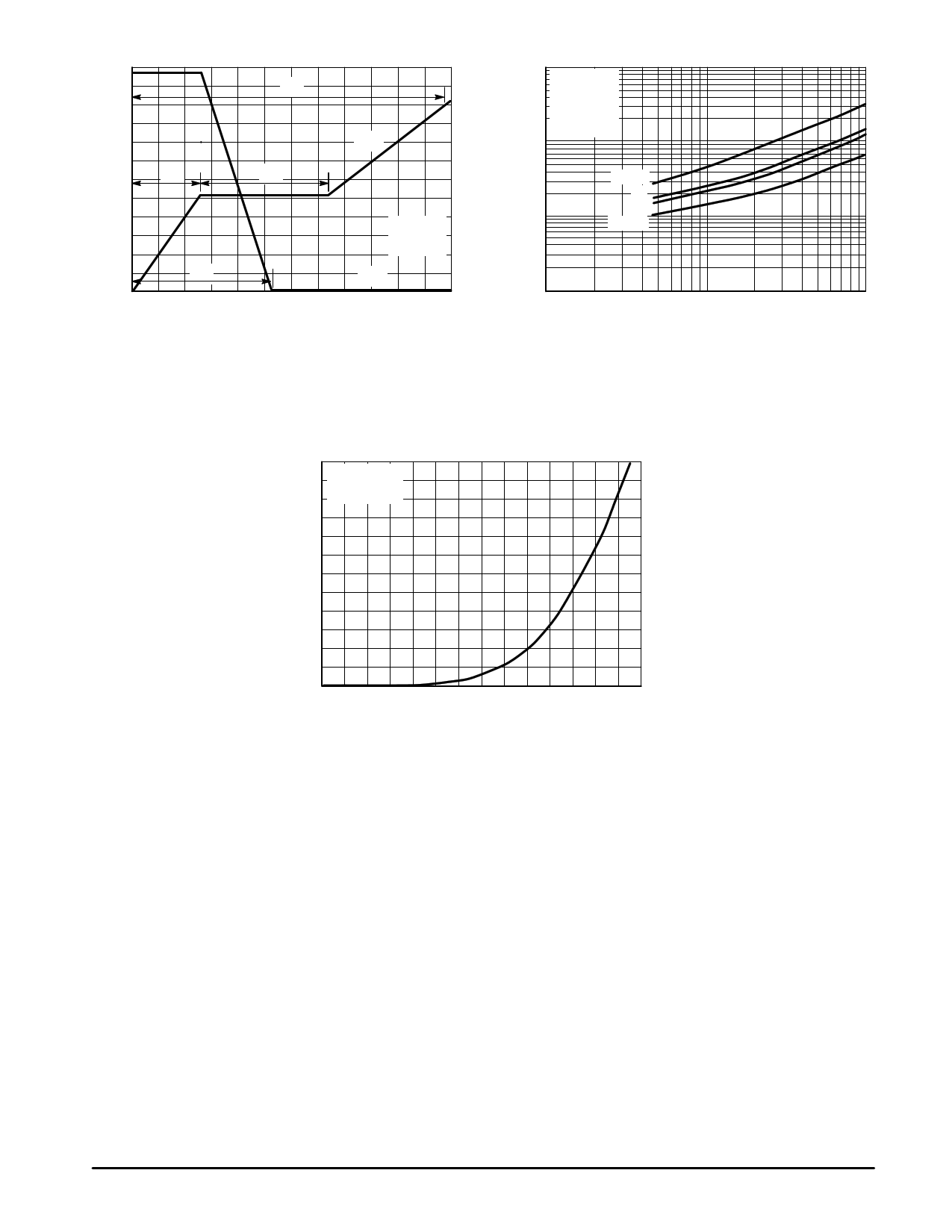

12 300

QT

10

8

6 Q1

VGS 200

Q2

4 ID = 6 A 100

2 TJ = 25°C

Q3 VDS

00

0 6 12 18 24 30 36

QT, TOTAL CHARGE (nC)

Figure 8. Gate–To–Source and Drain–To–Source

Voltage versus Total Charge

100

VDD = 300 V

ID = 6 A

VGS = 10 V

TJ = 25°C

10 td(off)

tf

tr

td(on)

MTB6N60E1

1

1 10 100

RG, GATE RESISTANCE (OHMS)

Figure 9. Resistive Switching Time

Variation versus Gate Resistance

DRAIN–TO–SOURCE DIODE CHARACTERISTICS

6

VGS = 0 V

5 TJ = 25°C

4

3

2

1

0

0.50 0.55 0.60 0.65 0.70 0.75 0.80 0.85

VSD, SOURCE–TO–DRAIN VOLTAGE (VOLTS)

Figure 10. Diode Forward Voltage versus Current

SAFE OPERATING AREA

The Forward Biased Safe Operating Area curves define

the maximum simultaneous drain–to–source voltage and

drain current that a transistor can handle safely when it is for-

ward biased. Curves are based upon maximum peak junc-

tion temperature and a case temperature (TC) of 25°C. Peak

repetitive pulsed power limits are determined by using the

thermal response data in conjunction with the procedures

discussed in AN569, “Transient Thermal Resistance–Gener-

al Data and Its Use.”

Switching between the off–state and the on–state may tra-

verse any load line provided neither rated peak current (IDM)

nor rated voltage (VDSS) is exceeded and the transition time

(tr,tf) do not exceed 10 µs. In addition the total power aver-

aged over a complete switching cycle must not exceed

(TJ(MAX) – TC)/(RθJC).

A Power MOSFET designated E–FET can be safely used

in switching circuits with unclamped inductive loads. For reli-

able operation, the stored energy from circuit inductance dis-

sipated in the transistor while in avalanche must be less than

the rated limit and adjusted for operating conditions differing

from those specified. Although industry practice is to rate in

terms of energy, avalanche energy capability is not a con-

stant. The energy rating decreases non–linearly with an in-

crease of peak current in avalanche and peak junction

temperature.

Although many E–FETs can withstand the stress of drain–

to–source avalanche at currents up to rated pulsed current

(IDM), the energy rating is specified at rated continuous cur-

rent (ID), in accordance with industry custom. The energy rat-

ing must be derated for temperature as shown in the

accompanying graph (Figure 12). Maximum energy at cur-

rents below rated continuous ID can safely be assumed to

equal the values indicated.

Motorola TMOS Power MOSFET Transistor Device Data

5

5 Page | ||

| Páginas | Total 8 Páginas | |

| PDF Descargar | [ Datasheet MTB6N60E1.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MTB6N60E | TMOS POWER FET 6.0 AMPERES 600 VOLTS | Motorola Semiconductors |

| MTB6N60E1 | TMOS POWER FET 6.0 AMPERES 600 VOLTS | Motorola Semiconductors |

| MTB6N60E1 | High Energy Power FET | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |